世界不是平的,半導體行業亦是如此。

2023 年,生成式AI如同當紅炸子雞,吸引著全球的目光。

當前,圍繞這一領域的競爭愈發白熱化,全球陷入百模大戰,并朝著千模大戰奮進。

大模型應用需要處理大規模的數據,以OpenAI的ChatGPT從第一代大約50億個參數,發展到GPT4.0大約將超過 1T 的參數,對算力的高需求不必多說。

在這場潮流中,AI芯片成為支撐引擎,為大模型應用提供強有力的支持。

在人工智能領域,大模型應用的興起,讓芯片的發展來到了一個新高度。蓬勃發展的大模型應用所帶來的特殊性需求,正推動芯片設計行業邁向新紀元。眾多頂級的半導體廠商紛紛為大模型應用而專門構建AI芯片,其高算力、高帶寬、動輒千億的晶體管數量成為大芯片的標配。

逐漸的,先進封裝技術如 CoWoS 成為 GPU 的主流選擇,先進封裝技術與 HBM(HBM 作為一種高性能內存解決方案被各大芯片廠商廣泛的應用)是一對無法忽視的組合,通過多芯片堆疊提高了芯片之間的通信速度和能效,為大模型應用提供強有力的支持。

當然,芯片設計行業的挑戰并不僅限于大模型應用的迅速發展:

智能手機、物聯網設備、自動駕駛汽車等應用市場的發展,各個領域對芯片的要求越來越高,因此,半導體設計和制造商必須利用更精密和復雜的設計方法來滿足這些新的需求。

正如在消費電子領域,許多移動和手持設備對低功耗的要求十分迫切。為了實現低功耗設計目標,芯片設計商不得不采用先進的低功耗技術,包括電源關斷技術(PSO)、多供電電壓(MSV)以及動態電壓頻率縮放(DVFS)等技術。

隨著晶體管數量的急劇攀升與設計師面臨的驗證場景越加豐富;特別是Chiplet技術的火熱也讓芯片設計復雜度,邁向新高峰。

Chiplet技術被認為是后摩爾時代繼續提高算力密度的重要技術之一,也獲得了大模型AI芯片的青睞。

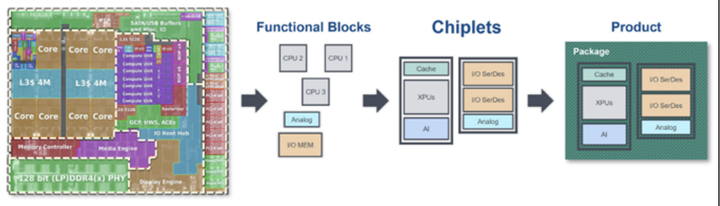

圖片來自:Google

Chiplet技術將芯片分割成更小的模塊,使得芯片可以采用異構設計,即不同的模塊可以由不同制造商提供,這為芯片設計帶來更大的靈活性和創新空間(更有甚者認為:Chiplet 技術正在改變半導體行業,其應用前景潛力無限)。

根據研究機構 Omdia 報告,2024 年采用Chiplet 的處理器芯片的全球市場規模將達 58 億美元,到 2035 年將達到 570 億美元。

但也由于Chiplet的發展剛起步不久,其還面臨著非常多的挑戰,就以其堆疊的設計問題而言:電路設計和協議標準可謂之相輔相成。

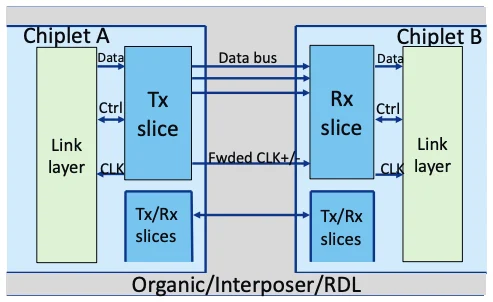

2.5D封裝SerDes方法,圖片來自:NASA

Chiplet之間的通信雖然可以依靠傳統的高速Serdes電路來解決,甚至能完整復用PCIe這類成熟協議;但這些協議主要用于解決芯片間甚至板卡間的通信,在Chiplet之間通信用會造成面積和功耗的浪費。

其次,通信協議是決定Chiplet能否“復用”的前提條件。如:Intel公司推出了AIB協議、TSMC和Arm合作推出LIPINCON協議,但在目前Chiplet仍是頭部半導體公司才會采用的技術,這些廠商缺乏與別的Chiplet互聯互通的動力。(如:UCIe聯盟的誕生,或許可以實現了通信協議的統一,IP公司就有可能實現從“賣IP”到“賣Chiplet”的轉型)。

需要特別注意的是:Chiplet理念下的芯片設計新思路也是設計方法學在芯片設計上體現的一種。

要讓基于Chiplet的設計方法從“可用”變為“好用”,或許仍需一個相對成熟且完整的設計流程,以及研制配套的設計輔助工具。

結合以上種種,我們不難發現:無論是哪種技術,變革都來自于客戶的需求。

就如對多芯片堆疊技術的需求與日俱增,催生出Chiplet理念下的芯片設計新思路,打開了新的性能和能效維度。

而要滿足這些需求,并沒有一招鮮吃遍天的方法,需要我們走出平面思維的局限,在全新的維度中探索。

審核編輯:劉清

-

芯片設計

+關注

關注

15文章

1155瀏覽量

56677 -

AI芯片

+關注

關注

17文章

2126瀏覽量

36771 -

OpenAI

+關注

關注

9文章

1245瀏覽量

10065 -

chiplet

+關注

關注

6文章

495瀏覽量

13601 -

ChatGPT

+關注

關注

31文章

1598瀏覽量

10264

原文標題:平面芯片思維的結束,Chiplet理念下的芯片設計新思路

文章出處:【微信號:奇普樂芯片技術,微信公眾號:奇普樂芯片技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

擁抱Chiplet,大芯片的必經之路

多Chiplet異構集成的先進互連技術

數字音頻放大器新思路:MAX98360全方位解析

躍昉科技受邀出席第四屆HiPi Chiplet論壇

得一微電子受邀出席第四屆HiPi Chiplet論壇

Chiplet核心挑戰破解之道:瑞沃微先進封裝技術新思路

Chiplet封裝設計中的信號與電源完整性挑戰

解構Chiplet,區分炒作與現實

CMOS 2.0與Chiplet兩種創新技術的區別

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet理念下的芯片設計新思路

Chiplet理念下的芯片設計新思路

評論