摩爾定律正在減速。過去我們靠不斷縮小晶體管尺寸提升芯片性能,但如今物理極限越來(lái)越近。在這樣的背景下,兩種創(chuàng)新技術(shù)站上舞臺(tái):CMOS 2.0和Chiplet(芯粒)。它們都在解決 “如何讓芯片更強(qiáng)” 的問題,但思路卻大相徑庭。

CMOS 2.0:把芯片做成“多層定制蛋糕”

要理解CMOS 2.0,得先說說它的“前輩”——傳統(tǒng)CMOS技術(shù):

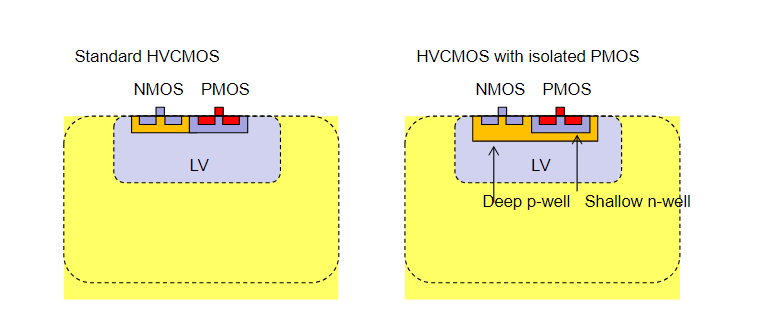

我們?nèi)粘S玫?a target="_blank">手機(jī)芯片、電腦CPU,本質(zhì)都是基于CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)打造的,就像用同一種配方烤出的單層蛋糕,所有運(yùn)算、存儲(chǔ)、供電模塊都擠在同一層面,功能越多,“蛋糕”就越厚,數(shù)據(jù)在模塊間傳遞的路徑也越長(zhǎng),不僅耗電還容易卡頓。而比利時(shí)研究機(jī)構(gòu)Imec在2024年提出的CMOS 2.0,徹底改變了這種“單層結(jié)構(gòu)”。它的核心是“單片異構(gòu)3D堆疊”,簡(jiǎn)單說就是:

把原本擠在同一層的芯片功能,拆成垂直疊加的不同層級(jí):最底層是高驅(qū)動(dòng)邏輯層,專門負(fù)責(zé)像“高速運(yùn)算”這樣的重活;中間層是高密度邏輯層,擅長(zhǎng)同時(shí)處理多個(gè)任務(wù);頂層還能疊上存儲(chǔ)器層,讓數(shù)據(jù)存取更方便。更關(guān)鍵的是,它在芯片背面偷偷加了一套“背面供電網(wǎng)絡(luò)(BSPDN)”,就像給蛋糕裝了隱形輸油管,不用再?gòu)恼胬@路供電,大幅降低了功耗。

這些功能層之間不是簡(jiǎn)單堆疊,而是靠納米級(jí)的高密度3D互連技術(shù)緊緊“粘”在一起,層間距離只有十億分之一米,數(shù)據(jù)傳遞速度比傳統(tǒng)芯片快10倍以上,功耗卻能降30%。

打個(gè)比方,傳統(tǒng)芯片是把巧克力、奶油、面粉全混在一起烤蛋糕,味道混雜還不好控制;CMOS 2.0則是分層制作——底層用高筋面粉做“支撐底座”(高驅(qū)動(dòng)邏輯層),中層用低筋面粉做“蓬松夾層”(高密度邏輯層),頂層抹上奶油當(dāng)“儲(chǔ)物格”(存儲(chǔ)器層),層間再涂一層超薄奶油(3D互連),既讓每一層的口感發(fā)揮到極致,又能快速傳遞味道,最終在同樣大小的蛋糕里,裝下更豐富的口感和營(yíng)養(yǎng)。

Chiplet:用“樂高積木”拼出高性能芯片

如果說CMOS 2.0是在“精雕細(xì)琢一塊蛋糕”,那Chiplet就是“用積木拼出復(fù)雜玩具”。我們先想想傳統(tǒng)大芯片的困境:一塊能滿足AI計(jì)算、多任務(wù)處理的高端芯片,面積可能達(dá)到400平方毫米,用5nm工藝制造時(shí),只要其中一個(gè)小區(qū)域有瑕疵,整個(gè)芯片就報(bào)廢了——這也是為什么高端芯片越來(lái)越貴,因?yàn)榱悸蕦?shí)在太低,5nm大芯片的良率甚至不到50%。

Chiplet的出現(xiàn),就是把這種“整塊廢”的風(fēng)險(xiǎn)降到最低。它的邏輯很簡(jiǎn)單:

把原本完整的大芯片,拆成一個(gè)個(gè)獨(dú)立的“小模塊”(功能裸片),每個(gè)模塊只干一件事——有的專門負(fù)責(zé)計(jì)算,有的專注存儲(chǔ),有的管外部接口。這些小模塊可以用不同工藝制造:比如計(jì)算模塊用最先進(jìn)的5nm工藝保證性能,接口模塊用成本更低的12nm工藝就夠了;甚至可以由不同廠商生產(chǎn),最后再通過2.5D中介層(類似積木的連接件)或者3D堆疊技術(shù),把這些小模塊裝到同一個(gè)“外殼”里,再靠UCIe(通用芯粒互連)這種“通用卡扣”,讓模塊間能快速傳遞數(shù)據(jù)。

那么,兩種技術(shù)差在哪呢?

CMOS 2.0追求的是“極致優(yōu)化”,而Chiplet追求的是“靈活實(shí)用”。它們之間的區(qū)別,可以從“一本書”和“活頁(yè)本”說起:

CMOS 2.0所有功能都在“同一塊芯片里”,那些垂直堆疊的功能層,就像在同一本書里做的立體夾頁(yè),夾頁(yè)和正文的距離只有幾毫米(對(duì)應(yīng)芯片里的納米級(jí)),靠“隱形裝訂線”(3D互連)緊緊連在一起,翻頁(yè)找內(nèi)容(數(shù)據(jù)傳輸)不用打開另一本書,速度自然快。而Chiplet是把多個(gè)獨(dú)立芯片(功能裸片)拼在一起,就像多本書組成的活頁(yè)筆記本,每本書(裸片)是獨(dú)立分冊(cè),靠活頁(yè)夾(封裝技術(shù))裝在一起,冊(cè)與冊(cè)之間距離有幾厘米(對(duì)應(yīng)芯片里的毫米級(jí)),找內(nèi)容得靠“書簽索引”(UCIe接口),雖然靈活,但傳遞效率不如同一本書里的夾頁(yè)。

不是“二選一”,而是未來(lái)芯片的“左右腿”

很多人可能會(huì)覺得,CMOS 2.0和Chiplet是競(jìng)爭(zhēng)關(guān)系,但實(shí)際上,它們更像是芯片行業(yè)的“左右腿”——一個(gè)解決“性能極限”問題,一個(gè)解決“成本可行性”問題,未來(lái)會(huì)一起推動(dòng)芯片技術(shù)往前走。

CMOS 2.0的價(jià)值,在于打破了“平面縮放”的限制。當(dāng)晶體管尺寸快要摸到1nm的物理極限,往垂直方向堆疊功能層,就像在同樣大小的土地上蓋高樓,能裝下更多功能。

而Chiplet的意義,在于降低了先進(jìn)技術(shù)的門檻。現(xiàn)在7nm工藝的成本比14nm高40%,3nm更是直接翻倍,很多廠商根本用不起。但有了Chiplet,廠商不用整顆芯片都用先進(jìn)工藝,只要核心模塊用高端工藝,其他模塊用成熟工藝就行,開發(fā)成本能降30%。這也讓更多行業(yè)能用上高性能芯片,比如智能汽車、工業(yè)機(jī)器人,不用再為“整塊高端芯片”的高價(jià)發(fā)愁。

未來(lái)我們很可能看到這樣的場(chǎng)景:一塊高端AI芯片,核心的計(jì)算部分用CMOS 2.0技術(shù)做多層堆疊,追求極致的運(yùn)算速度;而外圍的存儲(chǔ)、接口模塊,用Chiplet的方式組裝,控制成本。就像一棟地標(biāo)性摩天大樓,核心承重結(jié)構(gòu)用最堅(jiān)固的立體技術(shù)(類似CMOS 2.0),保證大樓能蓋得高、站得穩(wěn);而非承重的墻體、管道,用預(yù)制模塊組裝(類似Chiplet),降低成本還方便維護(hù)。

其實(shí)不管是CMOS 2.0的“多層蛋糕”,還是Chiplet的“樂高積木”,最終的目標(biāo)都是讓我們的電子設(shè)備更好用。半導(dǎo)體行業(yè)的創(chuàng)新從來(lái)不是“一條路走到黑”,而是在不同思路的碰撞中找到新方向,而這兩種技術(shù),無(wú)疑會(huì)是未來(lái)幾年芯片領(lǐng)域值得關(guān)注的“破局者”。

-

CMOS

+關(guān)注

關(guān)注

58文章

6224瀏覽量

243270 -

晶體管

+關(guān)注

關(guān)注

78文章

10429瀏覽量

148414 -

chiplet

+關(guān)注

關(guān)注

6文章

499瀏覽量

13638

原文標(biāo)題:蛋糕遇上積木:一文讀懂 CMOS 2.0 與 Chiplet

文章出處:【微信號(hào):奇普樂芯片技術(shù),微信公眾號(hào):奇普樂芯片技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

用PLC實(shí)現(xiàn)卷徑計(jì)算的兩種算法

黑芝麻智能斬獲AITX熱點(diǎn)創(chuàng)新技術(shù)獎(jiǎng)

ADI GMSL技術(shù)兩種視頻數(shù)據(jù)傳輸模式的區(qū)別

廣汽夸克電驅(qū)2.0榮獲2025全球新能源汽車創(chuàng)新技術(shù)獎(jiǎng)

2025是德科技創(chuàng)新技術(shù)峰會(huì)深圳站即將舉辦

這兩種TVS有啥不同?

兩種散熱路徑的工藝與應(yīng)用解析

村田中國(guó)亮相2025開放計(jì)算創(chuàng)新技術(shù)大會(huì):以創(chuàng)新技術(shù)驅(qū)動(dòng)智能化發(fā)展

歐菲光兩項(xiàng)創(chuàng)新技術(shù)通過國(guó)家發(fā)明專利授權(quán)

貼片晶振中兩種常見封裝介紹

東芝推出兩項(xiàng)創(chuàng)新技術(shù)提升碳化硅功率器件性能

2025年恩智浦創(chuàng)新技術(shù)峰會(huì)上海站圓滿落幕

銣原子鐘與CPT原子鐘:兩種時(shí)間標(biāo)準(zhǔn)的區(qū)別

CMOS 2.0與Chiplet兩種創(chuàng)新技術(shù)的區(qū)別

CMOS 2.0與Chiplet兩種創(chuàng)新技術(shù)的區(qū)別

評(píng)論