從1965年摩爾定律被提出至今,不到60年的時間里,集成電路制程工藝取得了飛躍式發展。

北京時間9月13日凌晨,隨著蘋果發布最新機型iPhone 15 pro/15 Pro Max,搭載A17 pro,意味著人類正式邁入3納米時代。

事實上,早在芯片設計進入納米時代之后,布局布線的復雜度便呈指數增長,從布局規劃到布局布線,時鐘樹綜合,每一步涉及到的算法在近年都有顛覆性的革新。這些步驟,都高度的依賴EDA工具。因此,EDA軟件也被譽為“芯片之母”。

EDA是英文Electronic Design Automation的縮寫,翻譯成漢語就是電子設計自動化。

如果說摩爾定律時代是EDA的1.0版,那么隨著摩爾定律逼近物理極限(1nm),一種全新對系統級芯片的定義被審視。

先進封裝加持AI,EDA進入了2.0時代。在EDA 2.0時代,“功耗低、性能優、成本低”所構筑的“不可能三角”將帶來哪些新挑戰,半導體設計廠商又該如何應對?

新思科技——這家全球第15大軟件公司,長期以來一直是EDA和半導體IP領域的全球領導者,在剛剛舉辦的9月8日“2023新思科技開發者大會”上,新思科技全球總裁Sassine Ghazi進一步闡述了對IC設計的未來以及EDA工具發展新趨勢。

芯片設計的五大挑戰

在主題演講中,新思科技全球總裁Sassine Ghazi前瞻性地提出了在SysMoore時代下芯片開發者將面臨的五大維度挑戰:軟件復雜性、系統復雜性、能效、信息安全和功能安全以及產品上市時間。

Sassine Ghazi先生指出,未來,移動通信與5G、個人電腦與游戲、消費電子、智能駕駛、AI和數據中心這五大領域引領科技創新航向。

當前,這些領域的創新一直在停留在軟件層面。而半導體芯片的創新能力,以及芯片與系統和軟件連接的能力,將真正驅動并加速創新步伐。

創新存在于芯片和軟件的交叉點

半導體市場經過60年發展,實現了5萬億美元的規模。但現在,僅需要再花7年時間,就能實現另一個5萬億美元的規模。這是由五大應用領域的需求指數級增加所帶來的。

“半導體產業正處于一個顛覆和創新的重要時刻。”Sassine Ghazi先生表示。

過去的60年里,我們在“摩爾定律”的指引下前進。我們的創新有一個特定的節奏,每兩年就把集成電路中的晶體管數量翻一番。回想一下這個節奏,它不僅是半導體公司創新的核心,也是系統公司創新的核心。因為系統公司認為,他們每隔兩年就可以提高性能和功耗來升級自己的產品。

現在很多人質疑,“摩爾定律”是走到盡頭了。“從技術角度看,我不認為摩爾定律到了盡頭。但是,這張圖展示的是摩爾定律的可負擔性以及每平方毫米良品芯片的成本。你可以看到,在14和16納米后,每平方毫米的制造成本是呈指數級增長的。”Sassine Ghazi先生談到。

現在,許多應用領域仍然沿著這個模型趨勢前進。這張圖中可以看到,我們有很多機會可以沿著摩爾定律的延續進行優化。這就是我們為什么需要AI加速芯片、GPU、CPU,去榨干它們的性能,然后繼續沿著摩爾定律的路徑前進。這就是我們所說的“規模復雜性”。還有另一個優化的方向叫做“系統的復雜性”或“系統復雜性”。

對此,國際頭部EDA廠商——新思科技提出了新的發展模式,即SysMoore,在系統層面對性能進行優化,而不單單是從晶圓當中所集成的晶體管數量的層面去優化性能。

新思科技領先工具應對挑戰

以汽車行業為例,過去5年中,汽車行業在“軟件復雜性、系統復雜性、能效、信息安全和功能安全以及產品上市時間”這五大方面都出現了重大的挑戰。

如今,一輛現代化的汽車上大概運行著1億行代碼,到2030年將超過3億行。3億行個什么概念呢?比如新思科技深耕軟件行業多年,產品種類豐富而全面,如今,新思科技公司37年的積累大約擁有3億行代碼量。而現在,一臺汽車就能擁有這么多代碼了。

這是由于,現代化汽車通過中央計算機系統連接了多個區域。可以像使用手機一樣更好地對汽車進行管理,對軟件和功能進行升級和更新。汽車將實現互聯和智能,汽車可以與車主相連,還可以連另一輛汽車、或是連另一個城市,而所有這些都由軟件驅動。

有機構預計,到2029-2030年末,也就是7年內,軟件定義汽車也就是SDV的占比將超過汽車總量的90%。而現在這個比例僅僅接近5%。

未來,軟件定義汽車的比例將從5%上升到90%。這樣的發展趨勢下,如何在連接汽車的硬件上對大量軟件進行建模和驗證?

新思科技通過電子數字孿生技術創建虛擬模型及進行硬件輔助軟件開發,應對軟件復雜性挑戰。

虛擬數字孿生,你可以通過它創建汽車整個系統的虛擬模型。該虛擬模型是在真車落地之前,在軟件層面的完整實現。一旦有了實物硬件,就可以進行硬件輔助軟件開發,還可以將兩者結合起來,其中一部分是可視化系統,另一部分是通過軟件驗證的硬件模型。基于我們在硬件輔助驗證方面的效率、性能和能力,新思科技在這兩個領域都處于領先地位。從移動領域開始,我們就一直致力于虛擬原型的開發,現在我們正在將這一理念帶入汽車領域。

談到了摩爾定律放緩以及摩爾定律的成本。那么,替代方案是什么?如果不按照摩爾定律的指導進行優化,如何才能繼續創新?這就是系統復雜性帶來的困難。

新思對這一問題的解答是:以3DIC Compiler、Die-to-Die接口及芯片全生命周期管理助力多裸晶芯片系統創新。

目前,汽車電子占整個多裸晶芯片系統份額的13%,并且正在快速增長。如果汽車自動駕駛級別從當前的L0-L2,到L4、L5,那么在汽車半導體投入將提升50倍,才能實現自動駕駛、高級輔助駕駛(ADAS)類型的互聯汽車。這對硬件的復雜性和可負擔性構成了巨大挑戰。

我們可以采用流行的多裸晶芯片方式,選擇哪些功能需要采用最先進的技術,哪些功能可以采用16納米或7納米技術,然后把它們組合在一個系統中并整合到一個封裝內。

新思科技在5、6年前就關注到了業界的創新正在轉向這一趨勢。據估計,到2026年,約20%的芯片系統將采用多裸晶芯片或3DIC技術,到2030年,這一比例將上升到40%。未來,在整個芯片設計中,40%的多裸晶芯片系統將是3D的。新思科技推出的3DIC compiler和Die-to-Die接口及芯片全生命周期管理能夠幫助多裸晶芯片系統研發與創新。

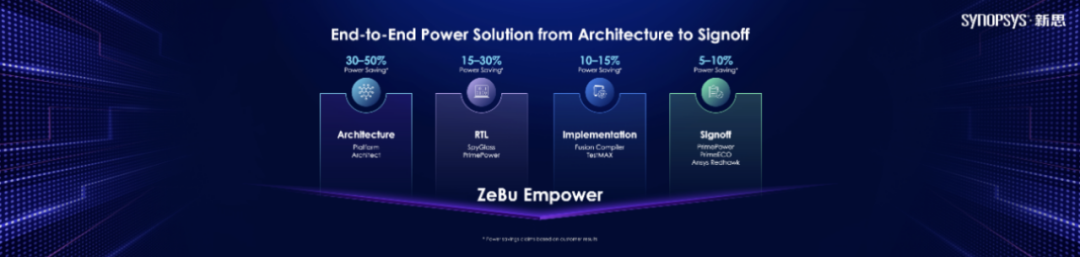

而對于汽車功耗面對的挑戰,新思科技提出了可覆蓋架構、RTL、實施到簽核的完整流程的端到端低功耗解決方案。

數據顯示,平均每輛電動汽車消耗20千瓦時電量只能行駛100公里,相當于一個獨棟別墅一天的用電量。而當電動汽車數量呈現指數級增長,又需要行駛幾百、上千公里時,如何降低能耗、提升每輛汽車的能源利用效率?

新思科技推出了端到端低功耗解決方案,可覆蓋架構、RTL、實施到簽核的完整流程。

2022年,12%的網絡攻擊都是針對汽車的。到2030年,電動汽車的數量會大幅增加。2022年,超過一千萬輛汽車因功能安全隱患(在美國)被召回。其中很多都是由軟件和半導體芯片導致的功能安全隱患。

因此信息安全和功能安全至關重要,是信息技術可靠性的重中之重。鑒于汽車主要由軟件和芯片、半導體驅動,汽車的可靠性就變得至關重要。

對于汽車的功能安全和信息安全,新思科技利用包括芯片、系統及應用層面的三階段芯片生命周期管理得以保護。第一是,監控芯片的健康狀況,在芯片內部嵌入監控器、傳感器和路徑監控,以持續跟蹤和測量整個芯片的性能和功耗。第二是,預測性維護。當了解了芯片健康狀況,對多系統或多車輛進行應用管理,這也是提高實地車輛安全性和可靠性。

最后是產品的上市時間,在西方國家汽車制造商生產自動駕駛汽車,如果從零開始研發汽車芯片,那么從開始開發到投產的周期大約為6到7年。中國汽車制造商周期相對更短,但人才缺口也是十分棘手的問題。

因此,更多企業加入利用AI加快產品上市的進程,用AI大大縮短產品上市時間、提高工作效率并實現更好的設計結果等。

今年,新思科技推出了業界首個AI驅動型全棧式EDA解決方案Synopsys.ai。截止目前,DSO.ai已經成功實現超過270次商業流片。與此同時,新思科技所提供的廣泛的IP組合也為開發者大幅提升生產率,加速產品上市速度。

最后,Sassine Ghazi先生強調:“中國約占全球半導體芯片消費量的50%,中國的需求和技術創新也持續影響著全球技術發展的風向。新思科技已深耕中國市場28年,支持中國半導體行業的發展。”未來,新思科技將繼續攜手產業上下游的合作伙伴,繼續推動整個生態系統加速發展。

-

算法

+關注

關注

23文章

4784瀏覽量

98060 -

芯片設計

+關注

關注

15文章

1155瀏覽量

56679 -

新思科技

+關注

關注

5文章

957瀏覽量

52900

原文標題:后摩爾時代,新思科技如何應對IC設計的5大挑戰

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新思科技亮相CES 2026國際消費電子展

摩爾線程在SIGGRAPH Asia 2025斬獲3DGS重建挑戰賽銀獎

Chiplet封裝設計中的信號與電源完整性挑戰

先進封裝轉接板的典型結構和分類

后摩爾時代破局者:物元半導體領航中國3D集成制造產業

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

LitePoint如應對UWB測試挑戰

后摩爾時代:芯片不是越來越涼,而是越來越燙

新思科技攜手微軟借助AI技術加速芯片設計

高溫IC設計必懂基礎知識:高結溫帶來的5大挑戰

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

后摩爾時代,新思科技如何應對IC設計的5大挑戰

后摩爾時代,新思科技如何應對IC設計的5大挑戰

評論