在智能手機、筆記本電腦、服務器,尤其是AI加速器芯片上,我們正在見證一個時代性的趨勢:計算力不斷攀升,芯片的熱也隨之“失控”。NVIDIA的Blackwell架構GPU芯片,整卡TDP功耗超過1500W,而在消費領域,旗艦顯卡RTX 5090也首次引入了液態金屬這一更高效但成本更高的熱界面材料(TIM)。

為什么芯片越來越熱?它的熱從哪里來?芯片內部每一個晶體管在開關動作時的能量損耗,匯聚成了最終“無處安放的熱量”。隨著晶體管數量的飛漲和面積不斷壓縮,我們正面臨著一個關鍵指標的持續抬升:熱流密度(Heat Flux Density)。

雖然摩爾定律正在放緩,但芯片集成度卻并未因此降低,尤其在臺積電CoWoS、英特爾Foveros等先進封裝技術的推動下,多芯粒堆疊和超高帶寬互連正推動芯片走向前所未有的“熱集中”時代。

那么,熱是怎么產生的?過去這些年晶體管密度和熱流密度如何變化?先進制程和封裝是否會讓芯片更熱?這一期,我們來系統聊一聊。

01

熱從哪里來?晶體管為什么發熱

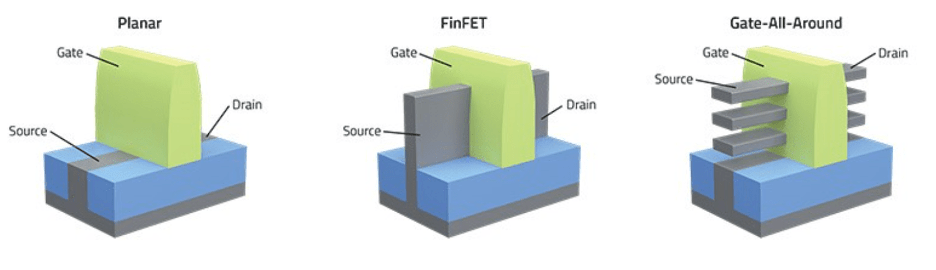

芯片之所以會發熱,根源在于其內部成千上億個晶體管在不斷地“開”和“關”。在這個過程中,一部分電能不可避免地轉化成熱能。一個芯片中可能包含數十億、甚至超過一萬億個晶體管。下圖是當前常用的FinFET晶體管的結構,FinFET全稱Fin Field-Effect Transistor,中文名叫鰭式場效應晶體管,是一種新的互補式金氧半導體晶體管。1999年,胡正明教授及其團隊成員成功制造出第一個p型FinFET,它的柵長度只有18nm,溝道寬度15nm,鰭的高度50nm。這些萬億晶體管被集成在芯片里每天“開關自如”,運行著從搜索推薦到AI訓練的復雜任務。

但每當晶體管切換狀態時,它就消耗能量并釋放熱量。這個過程中主要涉及兩個方面的功耗來源:

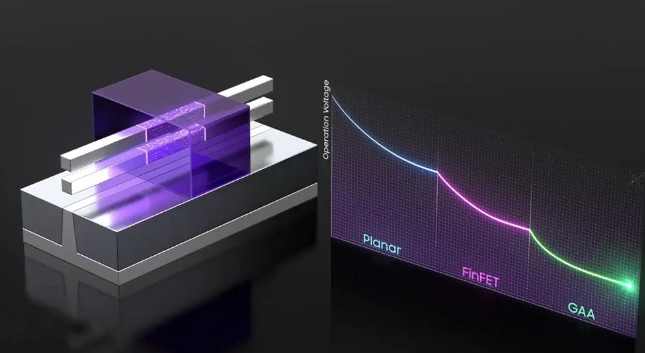

(1)動態功耗:當晶體管從關閉狀態切換到打開狀態,或從打開切換到關閉狀態時,內部的電荷重新分布或復合,產生能量損耗,并以熱的形式釋放出來。這種過程稱為動態功耗,是芯片運行時最主要的熱量來源。它可以近似表示為:它可以被近似地表示為:P = α · C · V2 · f;其中:α 是活動因子(代表多少晶體管在同時工作);C 是負載電容;V 是電壓;f 是頻率。可以看到,電壓越高、頻率越高,芯片的動態發熱就越嚴重。這也是為何芯片“超頻”時溫度急劇上升。

(2)靜態功耗:即使不工作也會漏電。即便晶體管處于“靜止狀態”,也仍有微弱電流泄漏,形成所謂的“靜態功耗”,其來源包括:亞閾值漏電流(Subthreshold leakage)、閂鎖電流(Gate leakage)、PN結反向偏置漏電(Junction leakage)。隨著晶體管尺寸不斷縮小,漏電流顯著增加,成為芯片發熱的“隱性殺手”。這也是當前制程演進中越來越難壓低功耗的原因之一。

電能在晶體管工作中損耗后,大部分以熱能的形式散發。這種能量轉換不可逆,最終導致芯片溫度升高。也就是說,不論是開關還是靜止狀態,晶體管都會發熱,只是程度不同。

02

晶體管密度提升,熱流密度同步飆升

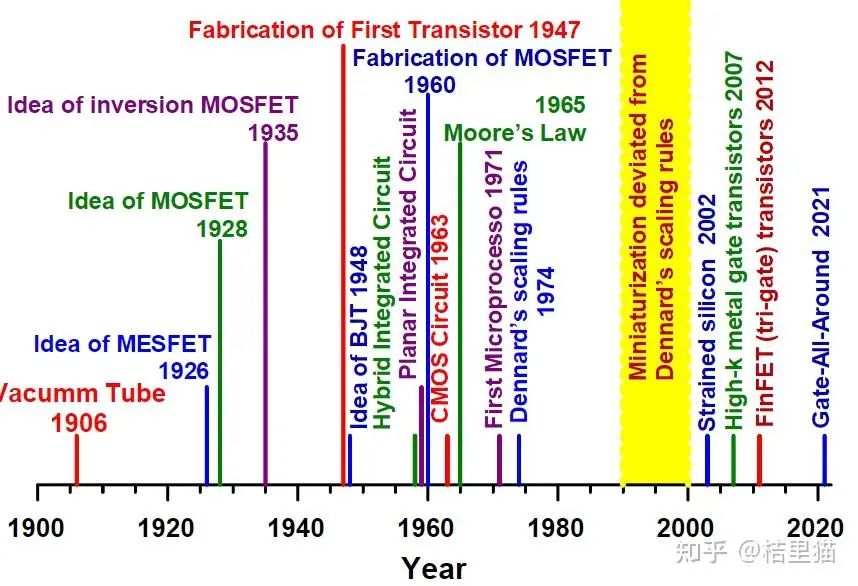

1965年,英特爾創始人之一的戈登·摩爾提出了經典的摩爾定律, “每18個月性能提升一倍,價格降低一半”。過去幾十年間,摩爾定律推動芯片性能飛速發展,這背后依賴的是制造工藝的不斷進步,使晶體管的尺寸越來越小、密度越來越高。但隨之而來的,是一個不可忽視的問題——熱流密度的快速上升。

早期節點(比如130nm、90nm)時,晶體管密度和功耗提升是相對線性的,但進入65nm之后,漏電流的急劇上升讓靜態功耗成為了大問題。雖然工藝不斷推進,但功耗墻(Power Wall)逐漸顯現。

圖3. 晶體管發展歷史(圖源:桔里貓)

與此同時,為了追求性能,芯片主頻也不斷升高——這意味著單位時間內的動態功耗暴增。而晶體管越密、芯片面積增長受限,結果就是:單位面積上的熱功耗密度不斷上升,熱管理難度迅速加劇。

這里我們要明確兩個概念:功耗(Power):整個芯片的總能耗,單位是瓦(W);熱流密度(Power Density):單位面積上的功耗,單位是W/cm2或W/mm2。舉個簡單的例子:一塊100W的CPU,面積為2cm2,則熱流密度為50 W/cm2。

| 制程節點 | 晶體管密度 | 功耗密度 | 主頻(GHz) |

|---|---|---|---|

| 90nm | ~10M | <30 | ~3 |

| 45nm | ~100M | ~80 | ~3.5 |

| 7nm | ~1000M | >100 | ~3.5-4 |

特別在7nm及之后,即使主頻不再大幅提升,但密度和功耗依舊在上漲,熱流密度成為設計瓶頸。如A100/A800 TDP是400W,芯片熱流密度 50W/cm2;H100/H800 TDP是700W,熱流密度87.5W/cm2,當下芯片熱流密度已經遠超風冷極限。

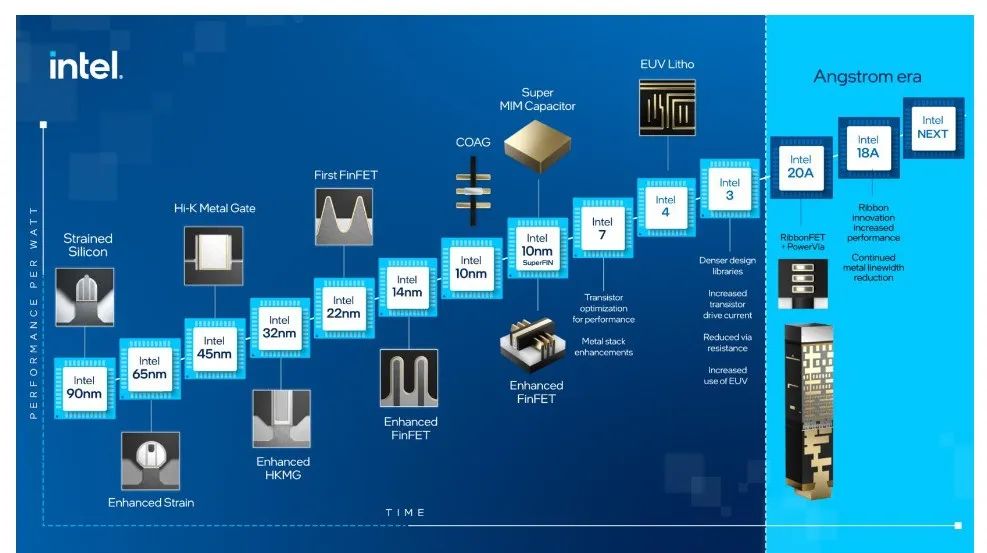

圖4. Intel晶體管發展計劃

早在20年前,英特爾前CTO和CEO帕特·蓋爾辛格就放話說,如果芯片耗能和散熱的問題得不到解決,當芯片上集成了2億個晶體管時,就會熱得像“核反應堆”,2010年時會達到火箭發射時高溫氣體噴射的水平,而到2015 年就會與太陽的表面一樣熱。

英偉達的B200芯片則達到了2080億晶體管,功耗高達1000W+。如果按單位面積換算,芯片的熱流密度早已超過核反應堆冷卻板、鋼鐵冶煉爐,逼近火箭噴嘴。

03

GAA與先進封裝:熱流密度會再度飆升嗎?

3.1從FinFET到GAA,熱管理走入“精細博弈”

摩爾定律放緩后,熱流密度會下降嗎?在摩爾定律不斷逼近物理極限的背景下,晶體管結構也在經歷代際更替。FinFET(鰭式場效應晶體管)已經在10年內主導了芯片工藝的主流。但從2025年臺積電N2、Intel18A以及三星SF2最新的產品架構看,幾家頭部大廠都開始轉型GAA(全環繞柵極)晶體管。

圖6. 從平面晶體管到FinFET再到GAA晶體管的轉變(圖源:Lam Research)

GAA的優勢在于能更有效地控制漏電流、提升開關性能,是功耗控制的一大利器。但這項結構創新也帶來了新的熱挑戰:

GAA晶體管單元結構更復雜、更精密,單位體積內的功耗密度更高;

多根納米片堆疊形成通道,柵極完全包覆,熱擴散路徑更短、更局限;

晶體管柵長進一步縮小,亞閾值泄漏和量子穿隧效應成為主要發熱來源。

總結:GAA讓“每一個晶體管”都更高效了,但也更熱了。

3.2 先進封裝:熱不再是“平均值”,而是“熱點集中”與GAA晶體管技術幾乎同步推進的,還有近年來蓬勃發展的先進封裝技術。臺積電的CoWoS、英特爾的Foveros、三星的I-Cube,都試圖將多個芯粒(chiplets)以2.5D或3D方式進行堆疊、集成,提升帶寬、降低延遲。但熱管理難度也隨之翻倍:

熱點集中:AI芯片、HPC芯片往往在中間集成一顆大算力芯粒,形成局部極端高溫區域;

熱路徑增長:上下堆疊的芯片彼此遮擋,芯片底部的熱量更難傳導到外部;

材料不匹配:封裝中的TIM(熱界面材料)、載板、芯粒之間存在熱膨脹系數差異,導致界面熱阻增大。

在B200這類AI芯片中,一顆核心芯粒+多顆HBM堆疊組成的“熱島”,不僅考驗散熱能力,也正在倒逼產業鏈重新設計整個熱結構。

進入先進封裝時代后多個高功耗芯片裸片被集成到同一封裝基板上,在空間不變的情況下,熱源集中度進一步提高,熱流密度陡增。如果在先進封裝中,熱源面積被進一步“壓縮”。這意味著傳統的風冷方式可能無法滿足需求,必須引入液冷、熱管、3D冷卻、甚至微射流等更激進的熱管理方案。臺積電已經開始在晶圓上嘗試微射流的液冷方案,感興趣的同學可以看上一期的文章。

AI芯片熱到極限?CoWoS封裝里藏著怎樣的“散熱”難題

04

結語與討論:熱管理,正在變成芯片設計的“第一門檻”?

曾經熱設計是最后一公里的工程問題。而今天,在GAA+3D封裝加持下的先進芯片,熱設計已然走到產品開發的最前沿。

很多人以為,摩爾定律趨緩、頻率不再提升,芯片的熱密度問題應該會“緩一緩”。但事實上,進入3D異構集成時代后,熱問題從“全局擴散”轉向“局部災難”:

提問:面對GAA與先進封裝的雙重推進,下一代熱管理材料和冷卻技術該如何跟上?歡迎大家在評論區分享你的看法同時留下你感興趣的話題?

參考資料[1] 芯片熱量如何產生的?,大米的老爹;[2] 芯片功耗是否都轉換為熱量,百科;[3] 一文了解晶體管發展歷程,半導體全解;[4] FinFET交棒GAA?關于GAA制程技術必須知道的事,EDN電子技術設計;

[4]半導體制程從180nm到14nm技術演進總結,半導體小馬;

-

芯片

+關注

關注

463文章

54223瀏覽量

468066 -

晶體管

+關注

關注

78文章

10423瀏覽量

148222 -

后摩爾時代

+關注

關注

0文章

13瀏覽量

9339

發布評論請先 登錄

電源“免疫力”決定芯片穩定性:PSRR測試為何越來越關鍵

【微納談芯】芯片測試越來越難的背后

為什么AI數據中心越來越依賴電流監測?

為什么原廠越來越需要一套自己的 Studio

為什么原廠越來越需要一套自己的 Studio

為什么機器人控制器越來越偏愛 RK3588?

為何Type-C越來越受歡迎?

負載越來越大,傳統互感器為什么開始拖企業用電管理的后腿?

Windows 在工廠里為什么越來越少見?答案只有兩個字:Linux

FPGA技術為什么越來越牛,這是有原因的

PCB為啥現在行業越來越流行“淺背鉆”了?

后摩爾時代破局者:物元半導體領航中國3D集成制造產業

芯片的驗證為何越來越難?

后摩爾時代:芯片不是越來越涼,而是越來越燙

后摩爾時代:芯片不是越來越涼,而是越來越燙

評論