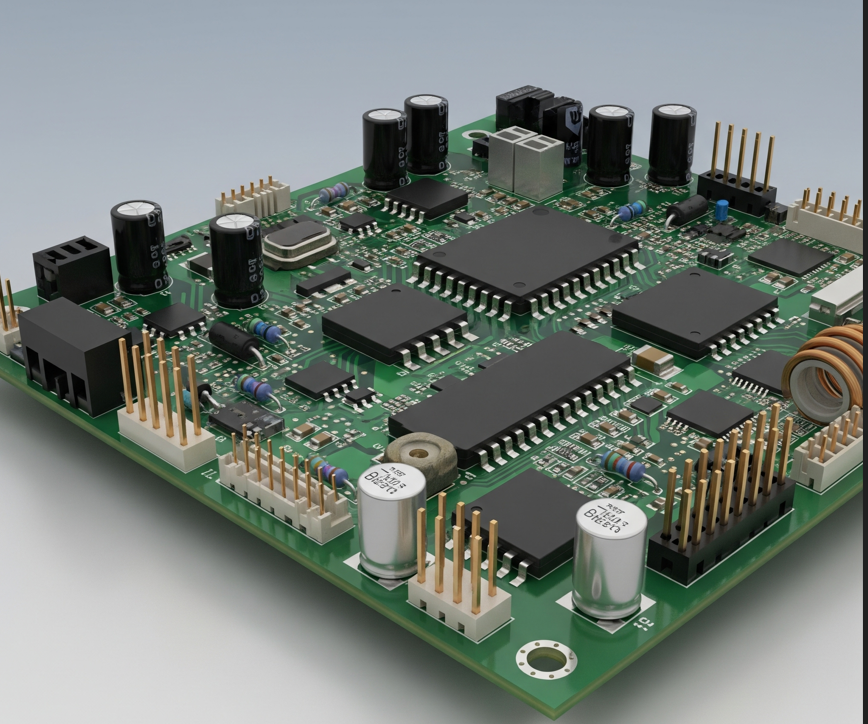

電子集成技術分為三個層次,芯片上的集成,封裝內的集成,PCB板級集成,其代表技術分別為SoC,SiP和PCB(也可以稱為SoP或者SoB)

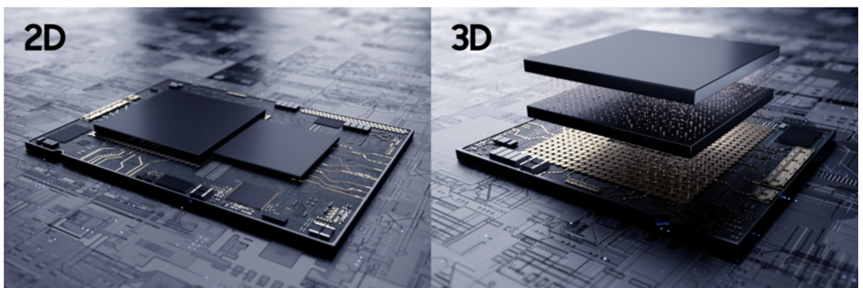

芯片中的整合主要是2D,晶體管采用平鋪方式整合在晶圓平面內;類似地,PCB中的集成主要由2D來完成,電子元器件平放在PCB的表面,所以,兩者均屬2D集成范疇。而且對于封裝內部集成來說情況要復雜很多。

電子集成技術分類的兩個重要判據:1.物理結構,2.電氣連接(電氣互連)。

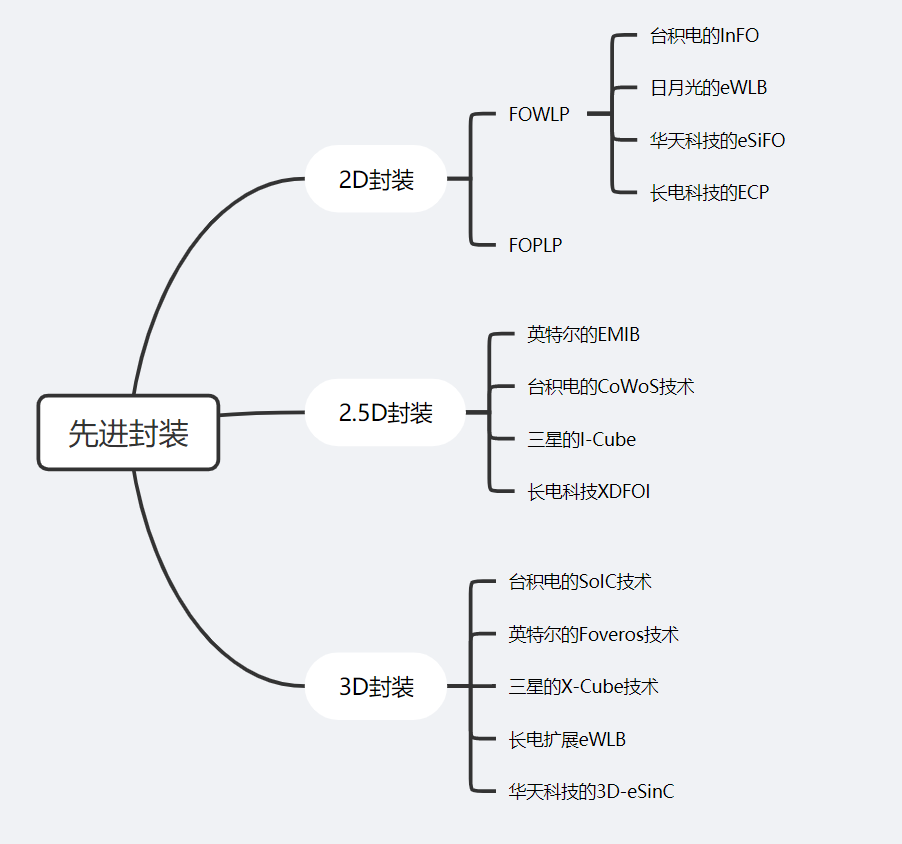

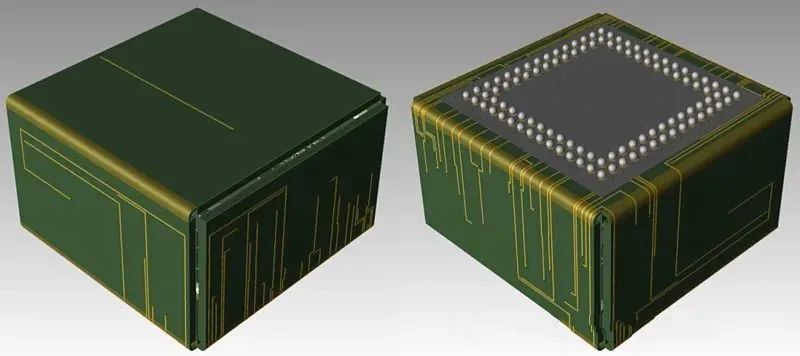

目前先進封裝中按照主流可分為2D封裝、2.5D封裝、3D封裝三種類型。

2D封裝

芯片中的整合主要是2D,晶體管采用平鋪方式整合在晶圓平面內;2D封裝方面包含FOWLP,FOPLP和其他技術。

物理結構:所有芯片和無源器件均安裝在基板平面,芯片和無源器件和 XY 平面直接接觸,基板上的布線和過孔均位于 XY 平面下方;

電氣連接:均需要通過基板(除了極少數通過鍵合線直接連接的鍵合點)

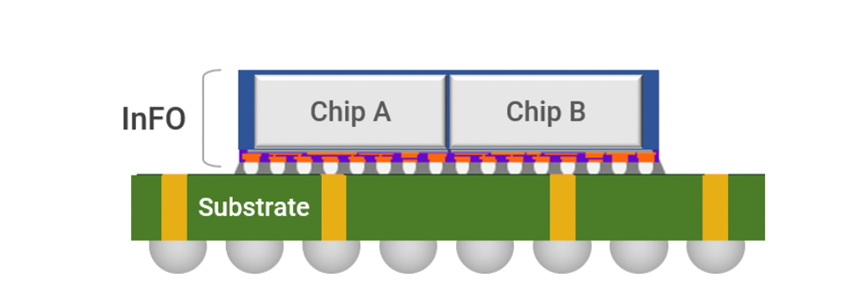

臺積電的InFO:

臺積電在2017年開發的InFO技術。InFO技術與大多數封裝廠的Fan-out類似,可以理解為多個芯片Fan-out工藝的集成,主要區別在于去掉了silicon interposer,使用一些RDL層進行串連(2016年推出的iPhone7中的A10處理器,采用臺積電16nm FinFET工藝以及InFO技術)。

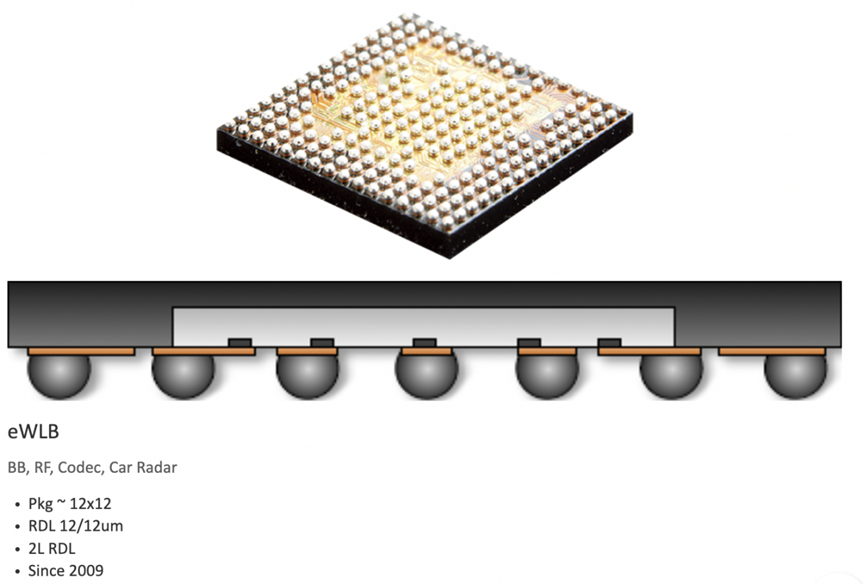

日月光的eWLB:與臺積的InFO類似,都屬于Fan-out技術

另外,還有一種2D+ 集成

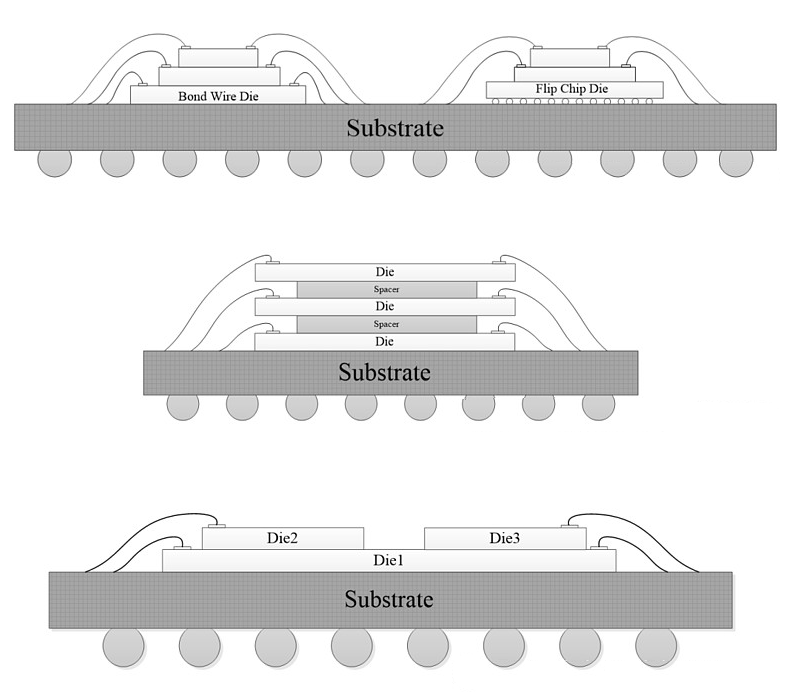

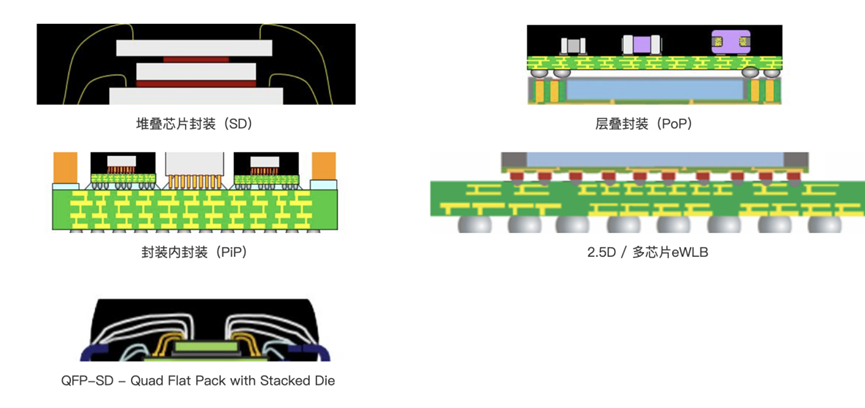

2D+集成是指的傳統的通過鍵合線連接的芯片堆疊集成。也許會有人問,芯片堆疊不就是3D嗎,為什么要定義為2D+集成呢?

主要基于以下兩點原因:

1)3D集成目前在很大程度上特指通過3D TSV的集成,為了避免概念混淆,我們定義這種傳統的芯片堆疊為2D+集成;

2)盡管物理結構為3D,但是它們的電氣互連都要經過基板,即首先要經過鍵合線與基板鍵合,再將電氣互連于基板。這一點與2D集成一樣,與2D集成相比,改進了結構堆疊,可以節約封裝空間,所以被稱為2D+集成。

物理結構:所有芯片及無源器件都地在XY平面之上,有些芯片與基板沒有直接接觸,基板中布線及過孔都在XY平面之下;

電氣連接:均需要通過基板(除了極少數通過鍵合線直接連接的鍵合點)

2.5D封裝:

2.5D封裝通常是指既有2D的特點,又有部分3D的特點,其中的代表技術包括英特爾的EMIB、臺積電的CoWoS、三星的I-Cube。

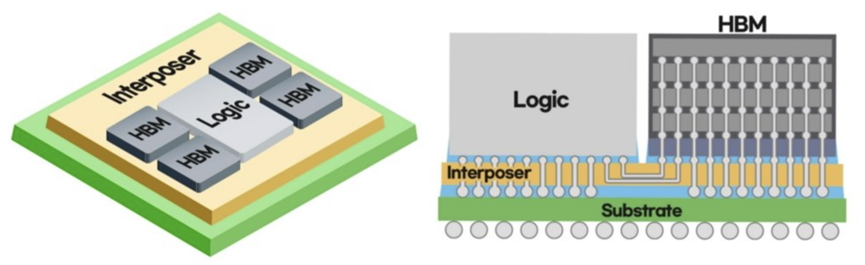

物理結構:所有芯片和無源器件均XY平面上方,至少有部分芯片和無源器件安裝在中介層上(Interposer),在XY平面的上方有中介層的布線和過孔,在XY平面的下方有基板的布線和過孔。

電氣連接:中介層(Interposer)可提供位于中介層上的芯片的電氣連接。

2.5D集成的關鍵在于中介層Interposer,一般會有幾種情況,

1)中介層是否采用硅轉接板,

2)中介層是否采用TSV,

3)采用其他類型的材質的轉接板;

在硅轉接板上,我們將穿越中介層的過孔稱之為TSV,對于玻璃轉接板,我們稱之為TGV

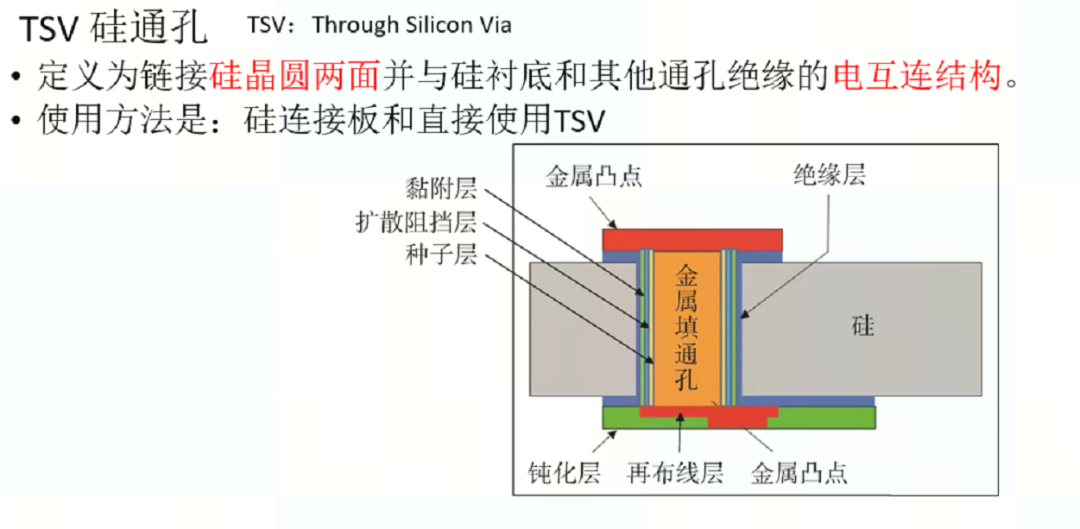

所謂的TSV 指的是:

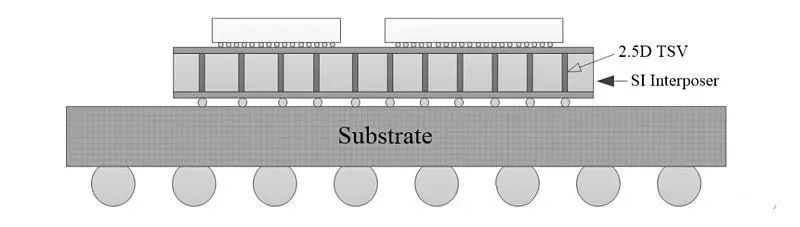

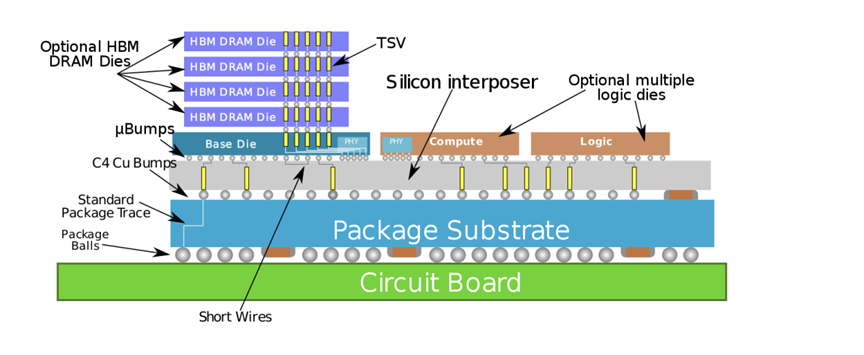

硅中介層具有TSV集成方式為2.5D集成技術中最為普遍的方式,芯片一般用MicroBump與中介層連接,硅基板做中介層使用Bump與基板連接,硅基板的表面采用RDL接線,TSV是硅基板上,下表面電連接通道,該2.5D集成方式適用于芯片尺寸相對較大的場合,當引腳密度較大時,通常采用FlipChip方式將芯片裝夾到硅基板中。

有TSV的2.5D集成示意圖:

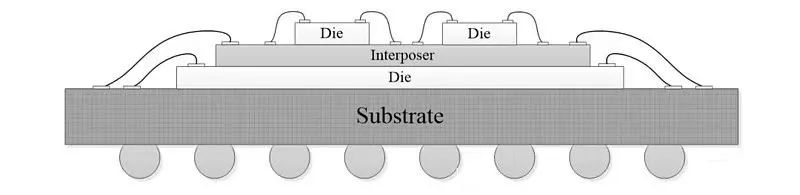

硅中介層無TSV的2.5D集成的結構一般如下圖所示,有一顆面積較大的裸芯片直接安裝在基板上,該芯片和基板的連接可以采用Bond Wire或者Flip Chip兩種方式,大芯片上方由于面積較大,可以安裝多個較小的裸芯片,但小芯片無法直接連接到基板,所以需要插入一塊中介層(Interposer),若干裸芯片安裝于中介層之上,中介層具有RDL布線可以從中介層邊緣引出芯片信號,再經Bond Wire與基板相連。這種中介層一般無需TSV,僅需在Interposer的上層布線來實現電氣互連,Interposer采用Bond Wire和封裝基板連接。

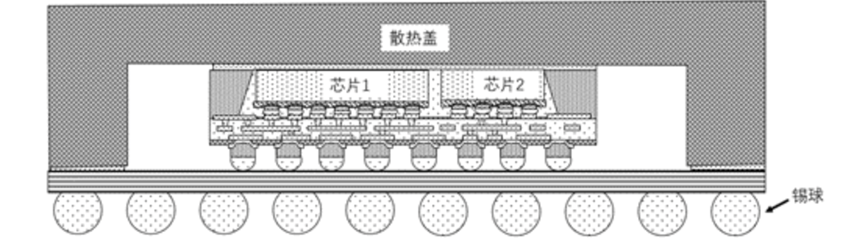

無TSV的2.5D集成示意圖:

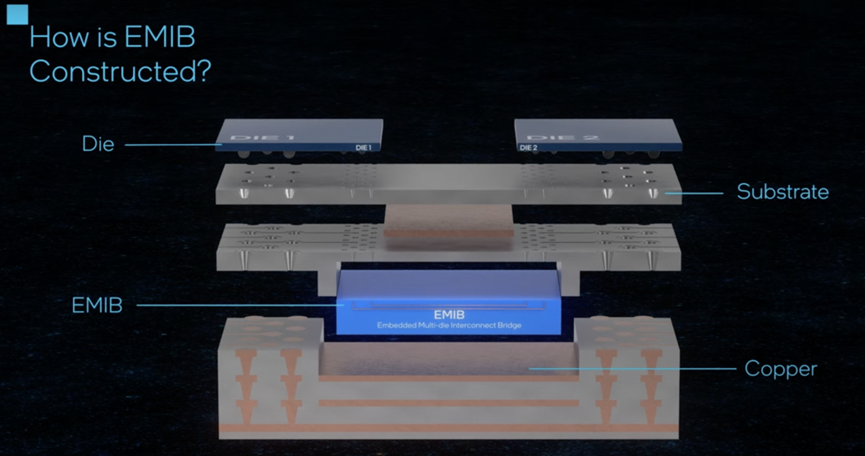

英特爾的EMIB:

概念與2.5D封裝類似,但與傳統2.5D封裝的區別在于沒有TSV。也正是這個原因,EMIB技術具有正常的封裝良率、無需額外工藝和設計簡單等優點。

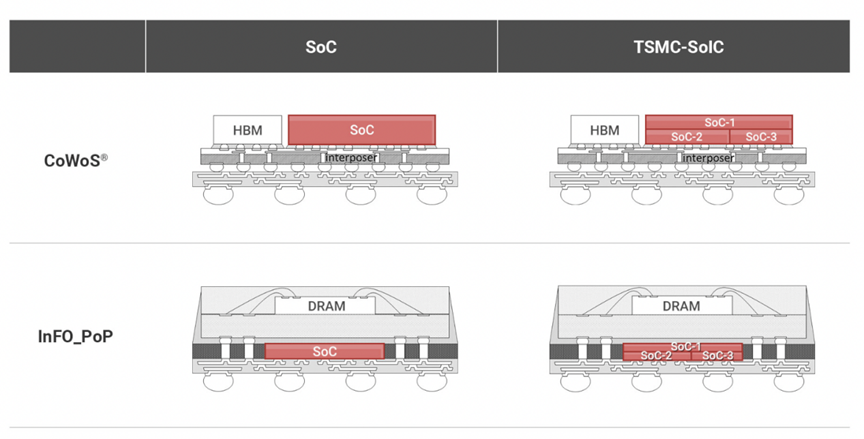

臺積電的CoWoS技術

臺積電的CoWoS技術也是一種2.5D封裝技術。根據中介層的不同可以分為三類,一種是CoWoS_S使用Si襯底作為中介層,另一種是CoWoS_R使用RDL作為中介層,第三種是CoWoS_L使用小芯片(Chiplet)和RDL作為中介層。

臺積電InFO(2D)與CoWoS(2.5D)之間的區別在于,CoWoS針對高端市場,連線數量和封裝尺寸都比較大;InFO針對性價比市場,封裝尺寸較小,連線數量也比較少。

第一代CoWoS主要用于大型FPGA。CoWoS-1的中介層芯片面積高達約800mm2,非常接近掩模版限制。第二代CoWoS通過掩模拼接顯著增加了中介層尺寸。臺積電最初符合1200mm2的要求,此后將中介層尺寸增加到1700mm2。這些大型封裝稱為CoWoS-XL2。

最近,臺積電公布的第五代CoWoS-S的晶體管數量將增加20倍,中介層面積也會提升3倍。第五代封裝技術還將封裝8個128G的HBM2e內存和2顆大型SoC內核。

長電科技XDFOI技術:

與2.5D TSV封裝技術相比,它具有高性能,高可靠性和低成本的特點。這種解決方案可以實現多層布線層而線寬或者線距可達2um。此外,本發明還利用極窄節距凸塊互連技術具有較大封裝尺寸,可以集成多個芯片,高帶寬內存以及無源器件等。

三星的I-Cube

三星的具有的先進封裝包括I-Cube、X-Cube、R-Cube和H-Cube四種方案。其中,三星的I-Cube同樣也屬于2.5D封裝。

3D封裝:

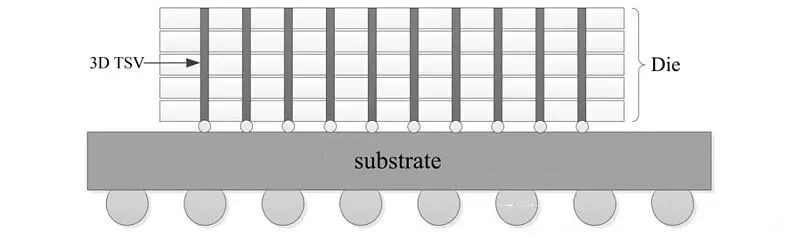

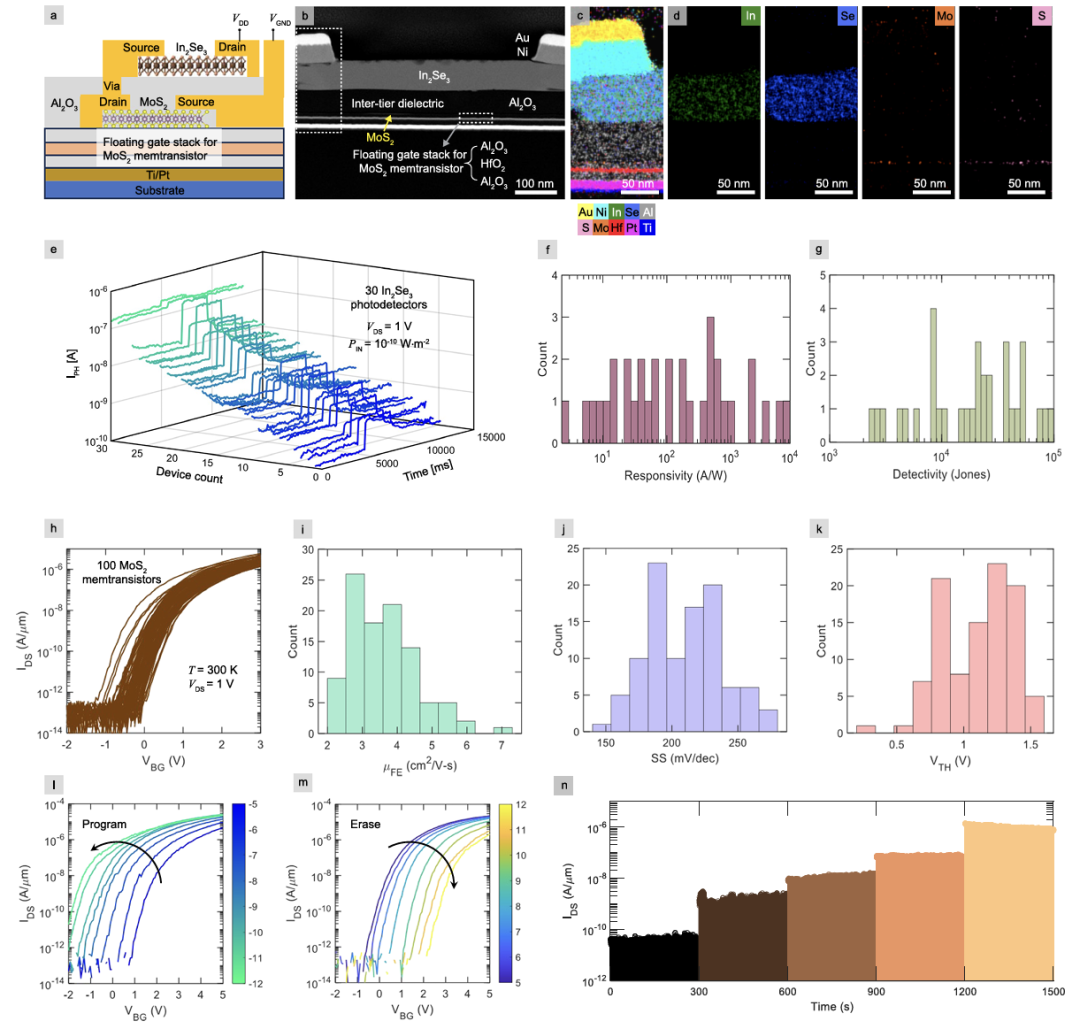

3D封裝和2.5D封裝的主要區別在于:2.5D封裝是在Interposer上進行布線和打孔,而3D封裝是直接在芯片上打孔和布線,電氣連接上下層芯片。3D集成目前在很大程度上特指通過3D TSV的集成。

3D集成和2.5D集成的主要區別在于:2.5D集成是在中介層Interposer上進行布線和打孔,而3D集成是直接在芯片上打孔(TSV)和布線(RDL),電氣連接上下層芯片。

物理結構:所有芯片及無源器件都位于XY平面之上且芯片相互疊合,XY平面之上設有貫穿芯片TSV,XY平面之下設有基板布線及過孔。

電氣連接:芯片采用TSV與RDL直接電連接

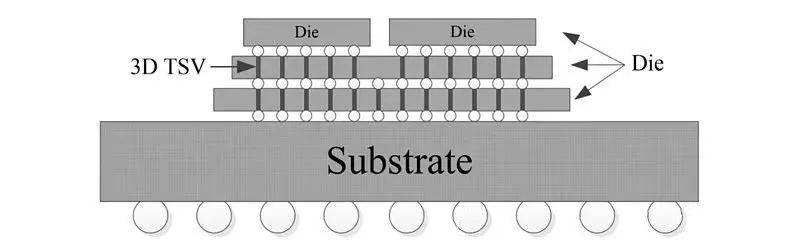

3D集成多適用于同類型芯片堆疊,將若干同類型芯片豎直疊放,并由貫穿芯片疊放的TSV相互連接而成,見下圖。類似的芯片集成多用于存儲器集成,如DRAM Stack和FLASH Stack。

同類芯片的3D集成示意圖:

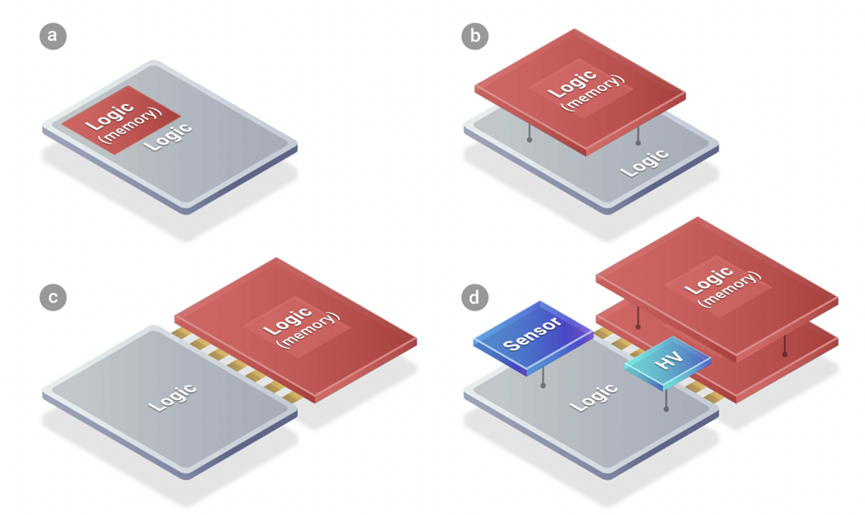

不同類別芯片進行3D集成時,通常會把兩個不同芯片豎直疊放起來,通過TSV進行電氣連接,與下面基板相互連接,有時還需在其表面做RDL,實現上下TSV連接。

臺積電的SoIC技術:

臺積電SoIC技術屬于3D封裝,是一種晶圓對晶圓(Wafer-on-wafer)的鍵合技術。SoIC技術就是利用TSV技術來實現無凸起鍵合結構并將許多不同特性的臨近芯片集成到一起并且其中最為關鍵的、最為神秘的是接合的物質,被稱為機密材料,價值達十億美元。

SoIC技術將同質和異質小芯片集成到單個類似SoC的芯片中,具有更小尺寸和更薄的外形,可以整體集成到先進的WLSI(又名CoWoS和InFO)中。從外觀上看,新集成的芯片就像一個通用的SoC芯片,但嵌入了所需的異構集成功能。

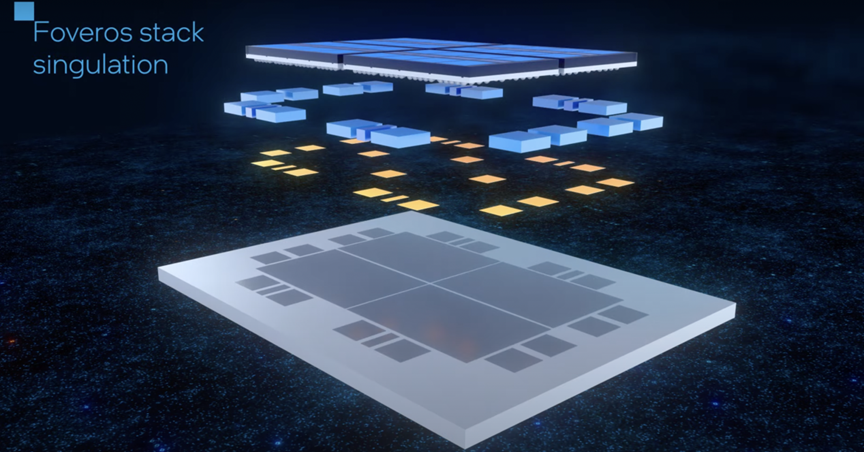

英特爾的Foveros技術:

由3D Foveros結構可知,最下半部分為封裝基底,上面放置有底層芯片作為主動中介層。中介層中存在大量TSV 3D硅穿孔負責聯通上、下層焊料凸起使上層芯片、模塊等與系統進行通訊。

三星的X-Cube 3D封裝技術:

使用TSV工藝,目前三星的X-Cube測試芯片已經能夠做到將SRAM層堆疊在邏輯層之上,通過TSV進行互聯,制程是他們自家的7nm EUV工藝。

長電科技的擴展eWLB:

長電科技以eWLB為核心的中介層可以在成熟低損耗封裝結構下進行高密度互連,從而提供更加有效的散熱以及更加快速的處理。3D eWLB互連(包括硅分割)采用獨特的面對面鍵合方式,不需要昂貴的TSV互連以及高帶寬3D集成。

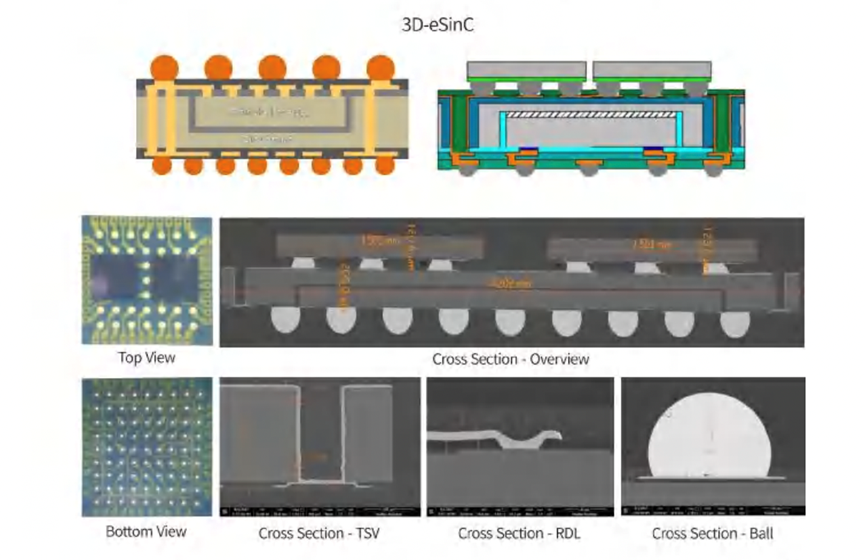

華天科技的3D-eSinC解決方案:

華天科技稱,2022年將開展2.5D Interpose FCBGA、FOFCBGA、3D FOSiP等先進封裝技術,以及基于TCB工藝的3D Memory封裝技術,Double Sidemolding射頻封裝技術、車載激光雷達及車規級12英寸晶圓級封裝等技術和產品的研發。

4D 集成:

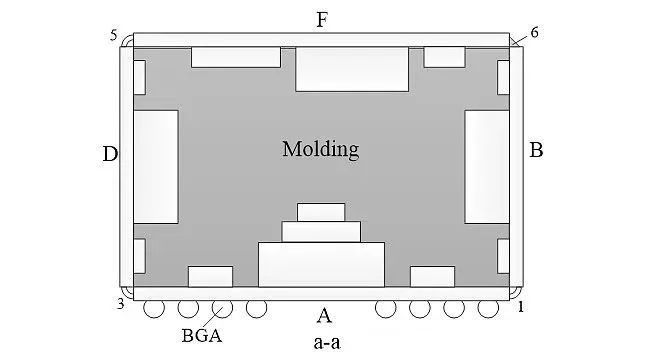

物理結構:多塊基板采用非平行的方式進行安裝,且每一塊基板上均設有元器件,元器件的安裝方式具有多樣化。

電氣連接:基板間采用柔性電路或焊接的方式相連,基板中芯片的電氣連接多樣化。

基于剛柔基板的4D集成示意圖:

4D集成定義主要是關于多塊基板的方位和相互連接方式,因此在4D集成也會包含有2D,2D+,2.5D,3D的集成方式

-

芯片

+關注

關注

463文章

54007瀏覽量

465952 -

封裝

+關注

關注

128文章

9248瀏覽量

148614 -

先進封裝

+關注

關注

2文章

533瀏覽量

1026

發布評論請先 登錄

2D材料3D集成實現光電儲備池計算

2D、2.5D與3D封裝技術的區別與應用解析

洛微科技攜4D FMCW激光雷達與3D感知方案閃耀光博會,引領行業新趨勢

玩轉 KiCad 3D模型的使用

3D封裝的優勢、結構類型與特點

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

生成式 AI 重塑自動駕駛仿真:4D 場景生成技術的突破與實踐

HT 可視化監控頁面的 2D 與 3D 連線效果

【半導光電】先進封裝-從2D,3D到4D封裝

【半導光電】先進封裝-從2D,3D到4D封裝

評論