文章來源:學習那些事

原文作者:前路漫漫

本文介紹了3D封裝的優勢、結構類型與特點。

3D 封裝的優勢與發展背景

近年來,隨著移動通信和便攜式智能設備需求的飛速增長及性能的不斷提升,對半導體集成電路性能的要求日益提高。然而,當集成電路芯片特征尺寸持續縮減至幾十納米,乃至最新量產的 5nm 和 3nm 時,摩爾定律的進一步發展遭遇瓶頸。傳統 2D 封裝因互連長度較長,在速度、能耗和體積上難以滿足市場需求。在此情況下,基于轉接板技術的 2.5D 封裝,以及基于引線互連和 TSV 互連的 3D 封裝等應運而生,并迅速發展起來。

3D 封裝采用與 2D 封裝不同的橫向互連方式,縮短了互連長度,具有諸多優勢:

(1)能有效利用立體空間,提高封裝密度,減小封裝體積。封裝向 Z 方向發展,節省了 XY 平面的封裝面積,與傳統封裝相比,采用 3D 技術可使尺寸縮小,質量減為原來的 1/50-1/40。

(2)可集成多種芯片和微電子機械系統(MEMS)器件等,有利于實現多功能、更大規模的集成。

(3)縮短了引線長度,降低了寄生電容和電感,提高了信號傳輸速度。

(4)寄生電容和電感的降低在提升性能的同時,進一步降低了能耗。

(5)節省了封裝、組裝及系統所需的材料。

3D 封裝的結構類型與特點

從互連結構來看,3D 封裝可分為封裝堆疊、芯片堆疊、芯片埋入、封裝內封裝、雙面封裝、通過轉接板互連等基本實現形式。這些基本形式可以組合,例如堆疊的封裝內某個封裝體內部可由多個芯片堆疊,其封裝基板內也可埋入芯片。

1.封裝堆疊

封裝堆疊包括引線框架堆疊、無引腳陶瓷片式載體堆疊、TAB 引線堆疊、基于焊球互連的堆疊 BGA、柔性載帶折疊封裝、側面圖形互連堆疊等形式。

高密度 3D 堆疊最適用于內存,或底部有高 I/O 數器件(微處理器、DSP、ASIC)的內存。

封裝堆疊的優點是單層封裝經過測試,有助于提高 3D 封裝的良率,且基于現有封裝平臺較易實現。封裝堆疊對單層封裝的要求是厚度較薄,若采用回流方式堆疊,封裝需能承受多次回流的高溫。

由于封裝堆疊需要單個芯片的完整封裝,因此在封裝過程中并未節約成本。

對于周邊引腳類型封裝,堆疊后信號仍需繞經封裝邊緣進行互連,其信號路徑縮短的效果比芯片堆疊等形式差。

2.芯片堆疊

芯片堆疊是指在單個封裝體內部堆疊多顆芯片。其互連方式主要有基于焊線的堆疊、基于倒裝 + 焊線的堆疊、基于硅通孔的芯片堆疊、薄芯片集成、芯片堆疊后埋入等。

芯片堆疊面臨的主要挑戰是芯片良率和熱管理。“已知良好的芯片” 比封裝體測試更困難,且封裝堆疊的產熱密度更高。

手機和其他便攜式產品中的多個芯片堆疊已大量生產,堆疊芯片的數量也呈上升趨勢。隨著芯片變薄,堆疊芯片封裝的厚度并不比傳統單芯片封裝厚。與單獨封裝后再互連相比,芯片堆疊縮短了信號路徑長度。

3.芯片埋入

芯片埋入是指將芯片嵌入封裝基板結構內部,可通過模壓或塑封等方式實現。

模壓芯片埋入的具體工藝過程與 FOWLP 工藝相同。層壓工藝本文不做介紹。塑封芯片埋入采用環氧樹脂模塑料對芯片進行包封,通常用模壓成型工藝進行塑封,模壓芯片埋入后通過再布線、扇出通孔(TIV)實現垂直互連。層壓工藝中使用半固化片,層壓工藝芯片埋入后通過激光鉆孔和布線工藝實現垂直互連。采用埋入方式能進一步提高封裝的集成度,縮小封裝尺寸,大幅縮短互連尺寸并提升器件性能。

4.封裝內封裝

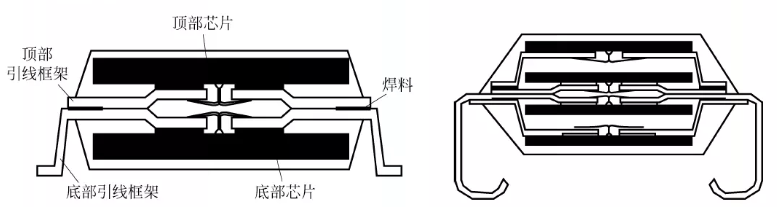

封裝的成品率與已知良好芯片的測試結果密切相關。封裝內封裝(Package in Package,PiP)是把經過預測試的封裝整合到 3D 堆疊結構中的技術。頂部封裝與底部封裝基板的連接采用導線鍵合的方式。2004 年,Flynn Carson 與 Young-Cheol Kim 曾提出 PiP 形式的 3D 封裝結構,其做法是將兩個已完成測試的封裝進行堆疊,上層封裝背面的焊盤與下層封裝基板上的焊盤通過焊線實現互連,之后再進行進一步的塑封和植球操作,最終形成 BGA 或 FPBGA 封裝。上層封裝內部為芯片堆疊結構。

5.雙面封裝

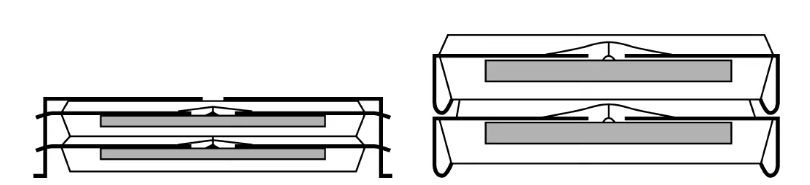

雙面封裝指的是將芯片分別貼裝在同一引線框架或基板正反兩面的封裝結構。采用引線框架的塑料封裝雙面封裝為雙面引線鍵合形式。基板型的雙面封裝則可以有多種形式,包括雙面引線鍵合、雙面倒裝,或者引線鍵合與倒裝相結合的混合形式。

對于雙面塑料封裝,需先完成正面的塑封工作,再進行反面的封裝操作。

6.混合類型 3D 及其他封裝

互連的形式豐富多樣,上述分類可能不夠全面。而且在實際應用中,并非僅采用單一的互連形式,而是會根據實際需求和工藝特點靈活選擇,常常會將多種形式組合使用。

下面對封裝堆疊進行介紹。

封裝堆疊

1.基于引線框架堆疊的 3D 封裝技術

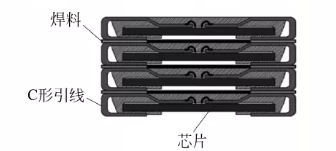

有一種 C 形引腳的引線框架,該結構中,上一層引線框架 C 形引腳(外引腳)的下表面與下一層引線框架 C 形引腳(外引腳)的上表面通過焊料進行焊接。2000 年,Soon-Jin Cho 等人提出了另一種基于 LOC 的雙層堆疊封裝。還有基于 LOC 的四重堆疊結構。這些引線框架的引腳長度和引腳彎曲角度都經過單獨設計,在完成芯片鍵合和引線鍵合后,各引線框架按照各自的朝向進行堆疊,對應引腳之間采用焊料鍵合,隨后進行整體塑封,之后按照常規的引線框架封裝工藝完成后續的制作步驟。

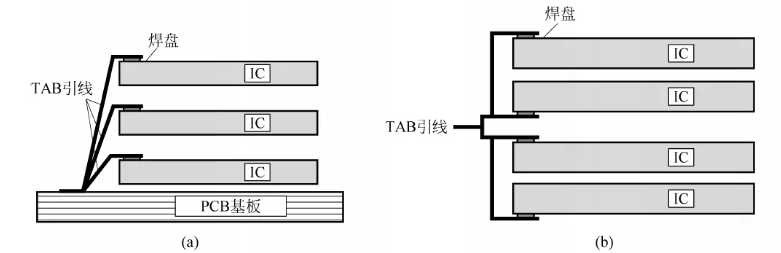

2.TAB 載帶堆疊封裝

TAB 堆疊 CSP 有兩種互連方式:一種是通過熱壓將 TAB 與 PCB 實現鍵合;另一種是直接進行 TAB 引線之間的鍵合。由于堆疊的每個 TAB 需要不同的引腳形狀,因此需要使用不同的模具進行切筋成型。單層 TAB 封裝完成后厚度較薄,所以堆疊后的封裝仍能保持較薄的外形。

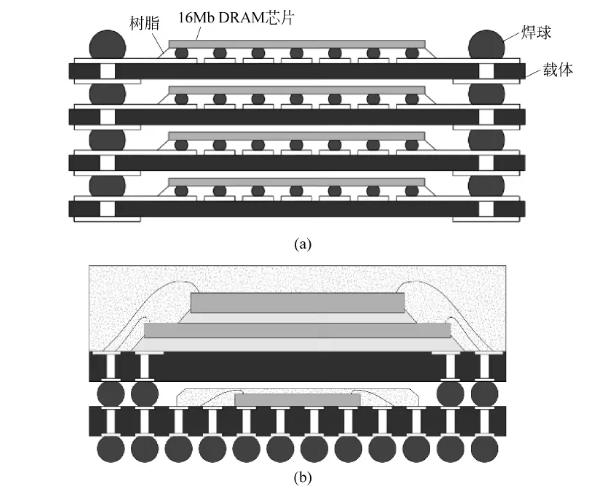

3.基于焊球互連的封裝堆疊

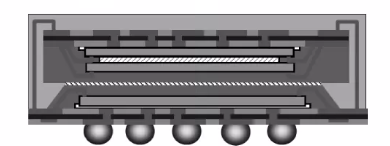

基于焊球互連的封裝堆疊(或稱 BGA 堆疊)存在兩種結構形式。在這種結構中,單個 BGA 封裝內部可以采用倒裝或焊線的連接方式,且單個封裝中芯片所在的面與層間互連的焊球可以處于同一側,也可以分別位于兩側。

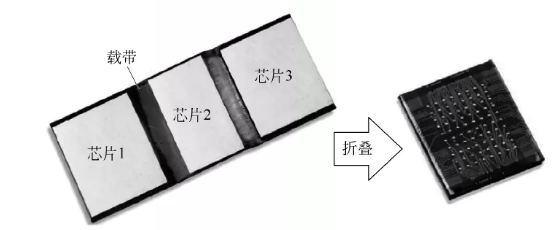

4.柔性載帶折疊封裝

柔性載帶折疊封裝通過折疊工藝,將平面裝配轉化為 3D 裝配形式。采用芯片疊層方式處理不同尺寸的芯片疊層(如 ASIC 與 SRAM)時操作更便捷,而在處理相同或相近尺寸的芯片時,需額外添加一個較厚的中介層,以便為焊線預留足夠空間,這會使成本有所增加。與芯片疊層方法相比,這種折疊方法對各類芯片的尺寸和高度都具有良好的適用性。

5.基于邊緣連接器的堆疊

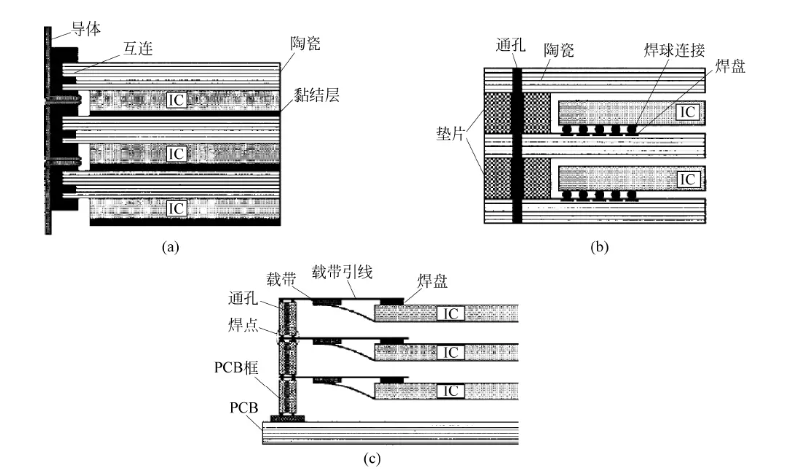

基于邊緣連接器的堆疊技術更貼近 3D 組裝技術,主要包含三種類型:①浸錫式垂直互連金屬框;②封裝基板與墊片通孔的填錫處理;③借助雙面 PCB 框,通過焊料連接上下基板。

6.側面圖形互連堆疊

將多層封裝進行堆疊后,在其側面制作互連圖案,從而實現不同層之間的互連,這一方式被稱為側面互連。該工藝能夠實現更高密度的堆疊封裝。

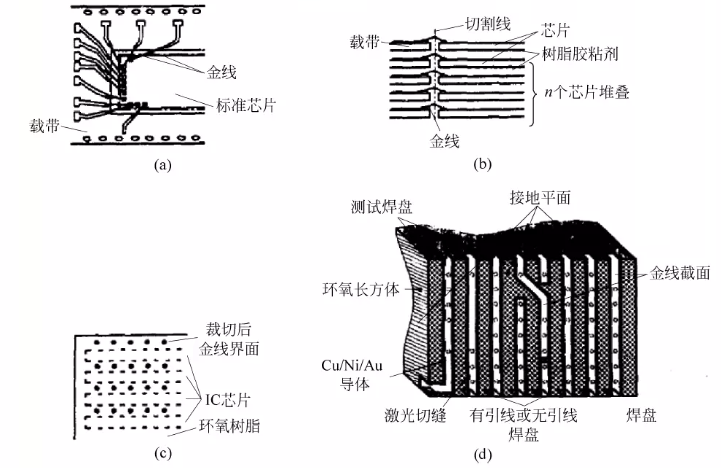

1990 年,Christia Val 與 Thierry Lemoine 提出了一種側面 3D 互連的堆疊封裝結構,其主要工藝流程如下:①在載帶上完成芯片與載帶的一級互連操作;②對單個集成電路進行測試與老化處理;③進行芯片堆疊并采用環氧樹脂膠合;④裁切形成包含多個芯片的長方體;⑤在立方體側面實現芯片間的二級互連,沉積 Cu/Ni/Au 薄膜后,用激光形成圖形;⑥通過焊線或焊料連接方式,將長方體與封裝基板 / 框架鍵合,制作成有引腳或無引腳的封裝體。

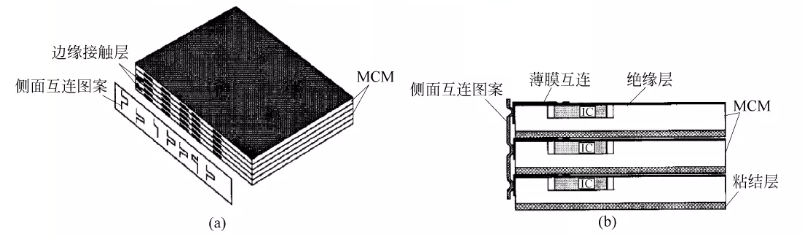

1994 年,GE 公司提出了一種側面互連的高密度多芯片模組(MCM),其單層制作工藝與平面 MCM 工藝相近,獨特之處在于將金屬圖形化工藝延伸至側面,具體包括濺射種金層、借助電泳保形涂覆阻擋層、利用 45° 鏡面反射激光同時對表面和側面的阻擋層進行圖形化處理、通過電鍍工藝增厚互連金屬等步驟;之后將單層層疊黏結,進一步在側面層壓硅聚酰亞胺(SPI),并進行側面開孔與互連制作。

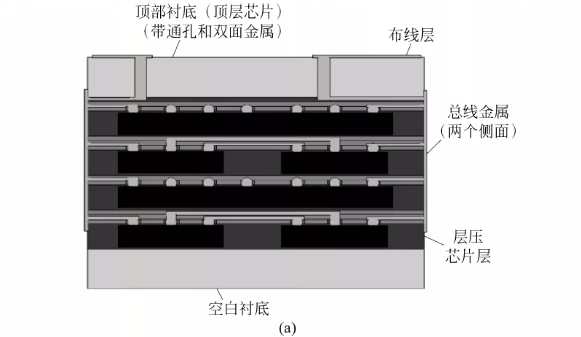

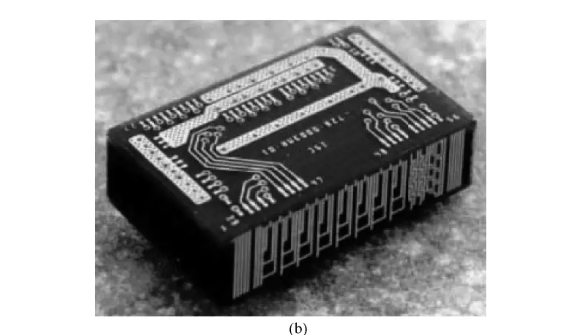

1998 年,IRVINE SENSORS 公司的 Keith D.Gann 等人提出了一種 NEO 堆疊技術,該技術可將不同尺寸或多個芯片的焊盤連接轉移至側邊的晶圓級 NEO 層,能夠在 50 層 NEO 層中,將 200 個大型閃存芯片堆疊在 0.75 英寸 ×1.2 英寸的面積上,高度僅為 0.5 英寸。通過兩個較長的側面總線實現了高水平的互連。

1999 年,IBM 公司也提出了一種側面互連的 3D 疊層存儲器件。該器件的片間層由三層 PI 層和一層再布線層構成,再布線層可同時實現將層內通孔轉移至側面通孔,進而在側面進行再布線和焊球制作,以實現對外連接。

-

封裝技術

+關注

關注

12文章

599瀏覽量

69302 -

3D封裝

+關注

關注

9文章

149瀏覽量

28307

原文標題:3D封裝技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

3D集成電路的結構和優勢

3D封裝的優勢、結構類型與特點

3D封裝的優勢、結構類型與特點

評論