【中國集成電路設計業(yè) 2021 年會暨無錫集成電路產(chǎn)業(yè)創(chuàng)新發(fā)展高峰論壇(ICCAD 2021)】在無錫太湖國際博覽中心圓滿落幕。

為期2天的高峰論壇豐富、氣氛熱烈、亮點紛呈,受到了來自全國各地業(yè)界人士的廣泛關(guān)注和思想碰撞。下面就請跟隨世芯電子一起,共同回顧本屆展會精彩盛況。

世芯電子展臺深受歡迎

直面挑戰(zhàn),永遠創(chuàng)新

在23日的IC與IP設計服務論壇上,世芯電子研發(fā)總監(jiān)溫德鑫結(jié)合了一些Alchip的設計案例,發(fā)表了演講【高性能運算/人工智能設計和2.5D/3D先進封裝】。

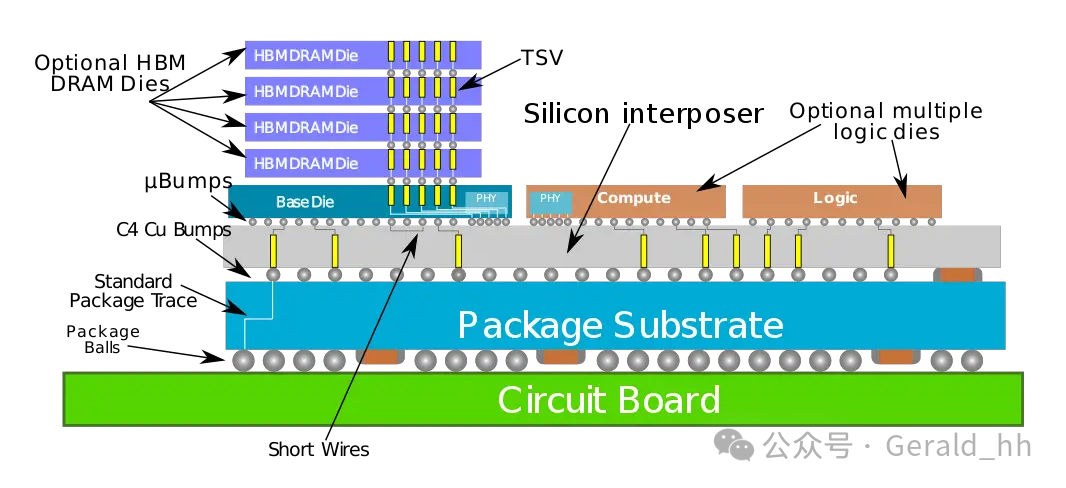

他表示:高性能運算和人工智能產(chǎn)品通常具有超大規(guī)模的邏輯門數(shù)、高主頻、高功耗的特性。隨著時間增長,2.5D的小芯片技術(shù)和3D封裝技術(shù)近年來也變得越來越流行。例如MCM、CoWoS已經(jīng)被2.5D先進封裝技術(shù)廣泛應用,以達到更高的功能、帶寬和能耗比。而這種類型的芯片本身在技術(shù)和項目管理方面都存在巨大的挑戰(zhàn),但世芯電子的創(chuàng)新腳步永不停歇。

在論壇上,溫德鑫還講述了下一代高性能運算及人工智能芯片的發(fā)展趨勢,以及對應設計中的挑戰(zhàn)和應對方法。同時,展示了近年來Alchip完成的2.5D CoWoS 產(chǎn)品,其中多顆CoWoS 產(chǎn)品已經(jīng)或者即將進入量產(chǎn),以及應對于未來chiplet 應用的世芯電子die-to-die IP APLink的成果和未來研發(fā)路線圖。

世芯電子成立以來, 已完成眾多高階制程(16納米以下)及高度復雜SoC案例的成功設計。相信在不久的未來,我們依然能保持初心,砥礪前行,深耕在這片“芯芯向榮”的土地,貢獻自己的能量。

原文標題:ICCAD完美落幕 | 世芯將永遠走在創(chuàng)新路上

文章出處:【微信公眾號:世芯電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

463文章

54009瀏覽量

465969 -

集成電路

+關(guān)注

關(guān)注

5452文章

12571瀏覽量

374523 -

封裝

+關(guān)注

關(guān)注

128文章

9249瀏覽量

148615

原文標題:ICCAD完美落幕 | 世芯將永遠走在創(chuàng)新路上

文章出處:【微信號:gh_81c202debbd4,微信公眾號:世芯電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

先進封裝成破局,博通率先落地3.5D,6000mm2超大集成

先進封裝時代,芯片測試面臨哪些新挑戰(zhàn)?

2D、2.5D與3D封裝技術(shù)的區(qū)別與應用解析

CoWoS產(chǎn)能狂飆下的隱憂:當封裝“量變”遭遇檢測“質(zhì)控”瓶頸

先進封裝市場迎來EMIB與CoWoS的格局之爭

技術(shù)資訊 I 一文速通 MCM 封裝

淺談2D封裝,2.5D封裝,3D封裝各有什么區(qū)別?

臺積電CoWoS技術(shù)的基本原理

Socionext推出3D芯片堆疊與5.5D封裝技術(shù)

HBM技術(shù)在CowoS封裝中的應用

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

普萊信成立TCB實驗室,提供CoWoS、HBM、CPO、oDSP等從打樣到量產(chǎn)的支持

多芯粒2.5D/3D集成技術(shù)研究現(xiàn)狀

分享兩種前沿片上互連技術(shù)

2.5D封裝為何成為AI芯片的“寵兒”?

MCM、CoWoS已被2.5D先進封裝技術(shù)廣泛應用

MCM、CoWoS已被2.5D先進封裝技術(shù)廣泛應用

評論