1 鎖相環(huán)的基本概念

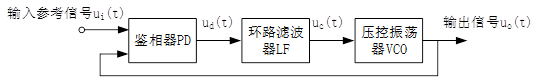

鎖相環(huán)(Phase Locked Loop,PLL)是一個閉環(huán)負反饋相位控制系統(tǒng),至少包含3個基本單元電路:

鑒相器(Phase Detector,PD);

壓控振蕩器(Voltage ControlledOscillator,VCO)。

鎖相環(huán)框圖

2 鎖相環(huán)的基本單元電路

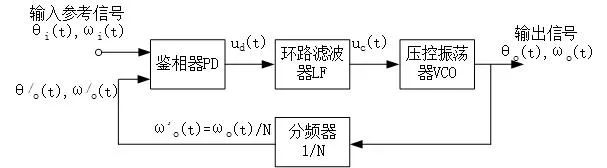

加入分頻器的鎖相環(huán)由鑒相器(Phase Detector,PD)、環(huán)路低通濾波器(Loop Filter,LF)、壓控振蕩器(Voltage Controlled Oscillator,VCO)和分頻器(Frequency Divider)組成。輸入信號的相位和頻率分別為θi(t)和ωi(t),單位分別為rad和rad/s;輸出信號的相位和頻率分別為θo(t)和ωo(t),單位分別為rad和rad/s。

鎖相環(huán)框圖

鑒相器將輸入周期信號的相位與壓控振蕩器輸出信號的相位進行比較,得到相位差θc,PD將θc轉(zhuǎn)換為誤差電壓信號ud(t)輸出。誤差電壓通過環(huán)路濾波器進行濾波,濾除交流成分,濾波的過程即為對誤差電壓信號ud(t)求平均值的過程,輸出直流控制電壓uc(t)。uc(t)控制壓控振蕩器的輸出頻率,以減小輸入信號與壓控振蕩器輸出信號之間的相位誤差。

理想情況下,壓控振蕩器輸出信號的頻率和相位等于輸入?yún)⒖夹盘柕念l率和相位,稱環(huán)路處于鎖定狀態(tài)(同步狀態(tài)、跟蹤狀態(tài))。實際情況下,相差不為零,會存在一個很小且恒定的相位誤差。

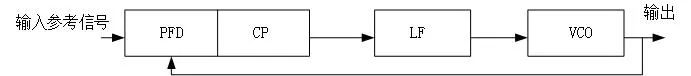

3 電荷泵鎖相環(huán)

電荷泵鎖相環(huán)由鑒頻鑒相器(Phase FrequencyDetector,PFD)、電荷泵(Charge Pump,CP)、環(huán)路低通濾波器(Loop Filter,LF)、壓控振蕩器(Voltage Controlled Oscillator,VCO)組成。

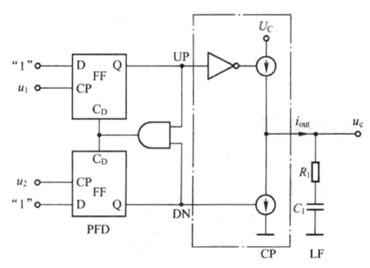

鑒頻鑒相器與電荷泵、一階RC無源環(huán)路濾波器的組合原理圖如下圖。PFD具有UP和DN兩個輸出端,輸出差分信號。UP和DN輸出端與電荷泵相連,控制電荷泵的電流開關(guān)。UP有效時,UP開關(guān)向環(huán)路濾波器提供泵電流Ip,當DN有效時,DN開關(guān)從環(huán)路濾波器吸收泵電流Ip。理想PFD具有第三態(tài),即兩個開關(guān)都斷開,濾波器的輸入端浮空。

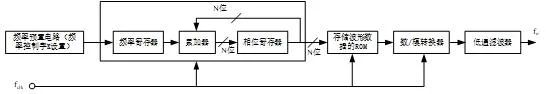

4 直接數(shù)字頻率合成器

DDS 的基本原理框圖如下所示,主要包括頻率預(yù)置電路、相位累加器、儲存波形數(shù)據(jù)的 ROM、數(shù)模轉(zhuǎn)換器及低通濾波器。其中 K 為頻率控制字,N 為相位累加數(shù)的位數(shù),fclk 為輸出時鐘頻率,fo為輸出波形的頻率。

相位累加器的 DDS 的核心,由 N 位加法器和N 位相位寄存器組成。在時鐘脈沖 fclk 的控制下,加法器將頻率寄存器中的頻率控制字K 與相位寄存器輸出的上一次累加的相位結(jié)果相加,以得到本次累加的結(jié)果,該結(jié)果存入相位寄存器。相位寄存器一方面將該結(jié)果反饋到加法器的輸入端,在下一時鐘脈沖的作用下,加法器繼續(xù)與頻率控制字相加;另一方面又將該累加值作為相位地址對波形 ROM 存儲表進行尋址,輸出的數(shù)據(jù)經(jīng)DA轉(zhuǎn)換器和低通濾波器后得到模擬波形。

編輯:lyn

-

鎖相環(huán)

+關(guān)注

關(guān)注

36文章

635瀏覽量

91261 -

壓控振蕩器

+關(guān)注

關(guān)注

10文章

180瀏覽量

30549 -

鑒相器

+關(guān)注

關(guān)注

1文章

62瀏覽量

23906 -

環(huán)路濾波器

+關(guān)注

關(guān)注

3文章

38瀏覽量

13442

原文標題:鎖相技術(shù)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Altera公司鎖相環(huán)IP核介紹

探索CDC516:高性能3.3V鎖相環(huán)時鐘驅(qū)動器

CDC2516:高性能鎖相環(huán)時鐘驅(qū)動器的深度解析

CDC509:高性能3.3V鎖相環(huán)時鐘驅(qū)動器

CDCVF2505 3.3 - V 時鐘鎖相環(huán)時鐘驅(qū)動器:設(shè)計與應(yīng)用指南

CDCVF25081:高性能鎖相環(huán)時鐘驅(qū)動器深度解析

TLC2932A高性能鎖相環(huán)芯片詳解:設(shè)計與應(yīng)用指南

探索TLC2933A高性能鎖相環(huán):特性、應(yīng)用與設(shè)計要點

?CDCVF2510 3.3V鎖相環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

?CDCVF25081 3.3-V 鎖相環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

?CDCVF2510A 3.3V鎖相環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

?TLC2932A 高性能鎖相環(huán)芯片技術(shù)文檔摘要

基于鎖相環(huán)的無軸承同步磁阻電機無速度傳感器檢測技術(shù)

高壓放大器在鎖相環(huán)穩(wěn)定重復(fù)頻率研究中的應(yīng)用

簡述鎖相環(huán)技術(shù)

簡述鎖相環(huán)技術(shù)

評論