CDC2516:高性能鎖相環時鐘驅動器的深度解析

在電子設計領域,時鐘驅動器是確保系統穩定運行的關鍵組件之一。今天,我們就來詳細探討一款高性能的鎖相環時鐘驅動器——CDC2516。

文件下載:cdc2516.pdf

一、CDC2516概述

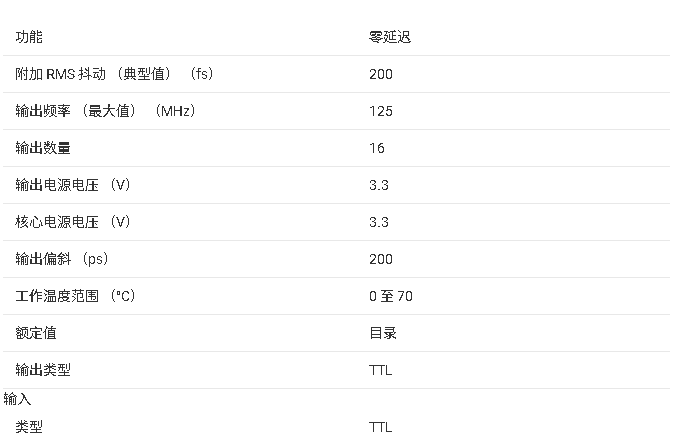

CDC2516是一款高性能、低偏斜、低抖動的鎖相環(PLL)時鐘驅動器,專為同步DRAM應用而設計。它工作在3.3V的VCC電壓下,能將一個時鐘輸入分配到四個輸出組,每組有四個輸出,總共提供16個低偏斜、低抖動的輸入時鐘副本。其輸出信號占空比可獨立于輸入時鐘調整為50%,且每個輸出組都能通過控制輸入單獨啟用或禁用。

嘗試搜索“鎖相環時鐘驅動器在同步DRAM應用中的優勢”時出現網絡問題,未能獲取相關信息。不過我們繼續深入了解CDC2516的特性。

二、關鍵特性

(一)PLL精準同步

CDC2516利用PLL技術,能在頻率和相位上精確地將反饋輸出(FBOUT)與時鐘(CLK)輸入信號對齊。通過外部反饋引腳(FBIN),可將輸出與時鐘輸入同步,確保系統的時鐘信號穩定且準確。大家在設計時,是否考慮過PLL的同步精度對整個系統性能的具體影響呢?

(二)集成阻尼電阻

該驅動器集成了串聯阻尼電阻,無需外部RC網絡,這不僅減少了組件數量,還節省了電路板空間和成本。每個輸出都有集成的25Ω串聯阻尼電阻,非常適合驅動點對點負載。在實際應用中,這種集成設計是否能有效降低設計的復雜度和成本呢?

(三)輸出靈活控制

四個輸出組的每個輸出都有獨立的使能控制(1G、2G、3G和4G),可以根據需要單獨啟用或禁用輸出。當G輸入為高時,輸出與CLK在相位和頻率上同步切換;當G輸入為低時,輸出被禁用為邏輯低狀態。這種靈活的控制方式,在不同的應用場景中能發揮怎樣的優勢呢?

三、電氣參數與性能指標

(一)絕對最大額定值

CDC2516的電源電壓范圍為 -0.5V至4.6V,任何輸出在高電平的電壓范圍為 -0.5V至VCC + 0.5V,存儲溫度范圍為 -65°C至150°C。在使用時,必須嚴格遵守這些額定值,否則可能會對器件造成永久性損壞。大家在實際操作中,有沒有遇到過因超出額定值而導致器件損壞的情況呢?

(二)推薦工作條件

推薦的電源電壓VCC為3V至3.6V,高電平輸入電壓VIH最小為2V,低電平輸入電壓VIL最大為0.8V,輸入電壓VI范圍為0至VCC,工作溫度范圍為0°C至70°C。在設計電路時,確保器件在推薦工作條件下運行,能保證其性能和可靠性。

(三)電氣特性

在推薦的工作條件下,CDC2516的輸入輸出電壓、電流等參數都有明確的規定。例如,VOH在不同輸出電流下有不同的取值,VOL也會隨著輸出電流的變化而變化。這些電氣特性是我們在設計和調試電路時需要重點關注的內容。

(四)時序要求和開關特性

時鐘頻率范圍為25MHz至125MHz,輸入時鐘占空比為40%至60%,PLL獲得相位鎖定所需的穩定時間為1ms。在開關特性方面,相位誤差、抖動、偏斜等參數都有明確的指標,這些參數直接影響著時鐘信號的質量和系統的性能。在實際應用中,如何根據這些參數來優化電路設計呢?

四、封裝與布局

CDC2516采用48引腳的塑料薄收縮小外形封裝(TSSOP),型號為CDC2516DGGR。文檔中還提供了詳細的封裝尺寸、引腳定義、載帶和卷盤信息以及示例電路板布局和鋼網設計等內容。合理的封裝和布局設計對于減少干擾、提高信號完整性至關重要。在進行電路板布局時,大家會遵循哪些原則和技巧呢?

五、總結

CDC2516以其高性能、低偏斜、低抖動以及靈活的輸出控制等特性,成為同步DRAM應用中時鐘驅動的理想選擇。在使用該器件時,我們需要嚴格遵守其電氣參數和工作條件,合理進行封裝和布局設計,以確保系統的穩定運行。希望通過本文的介紹,能讓大家對CDC2516有更深入的了解,在實際設計中充分發揮其優勢。大家在使用類似器件時,是否也有自己獨特的經驗和見解呢?歡迎分享交流。

發布評論請先 登錄

CDC509高性能、低偏斜、低抖動、鎖相環(PLL)時鐘驅動器數據表

CDC2516:高性能鎖相環時鐘驅動器的深度解析

CDC2516:高性能鎖相環時鐘驅動器的深度解析

評論