CDC509:高性能3.3V鎖相環時鐘驅動器

在電子設計領域,時鐘驅動是一項關鍵技術,尤其是在同步DRAM應用中,需要高精度、低抖動的時鐘信號來確保數據的準確傳輸。德州儀器(Texas Instruments)的CDC509就是一款專為同步DRAM應用設計的高性能、低偏斜、低抖動的鎖相環(PLL)時鐘驅動器。今天我們就來深入了解一下這款產品。

文件下載:cdc509.pdf

產品概述

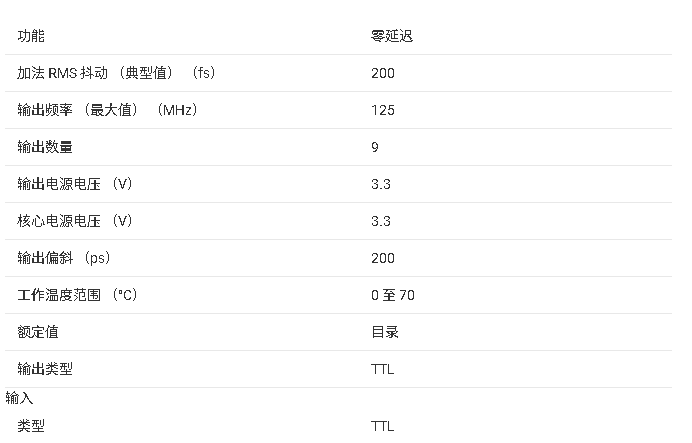

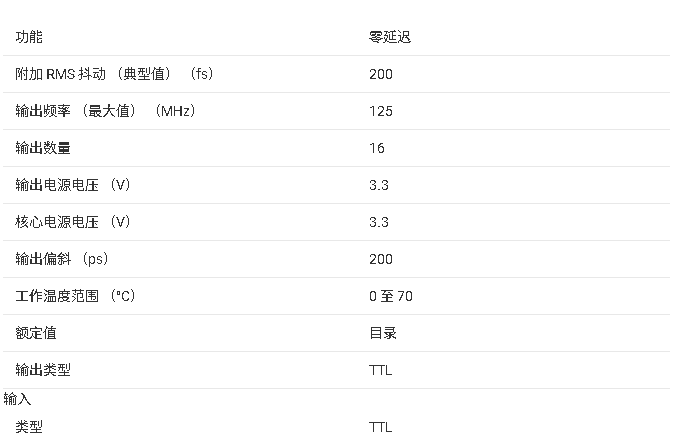

CDC509是一款工作在3.3V電源電壓下的鎖相環時鐘驅動器,它使用PLL技術將反饋(FBOUT)輸出信號在頻率和相位上精確對齊到時鐘(CLK)輸入信號。該產品將一個時鐘輸入分配到一組五個輸出和一組四個輸出,每組輸出都有獨立的使能控制,能夠提供九個低偏斜、低抖動的時鐘信號副本。此外,輸出信號的占空比會被調整為50%,而不受CLK輸入占空比的影響。

產品特性

無需外部RC網絡

與許多包含PLL的產品不同,CDC509不需要外部RC網絡。其PLL的環路濾波器集成在芯片內部,這不僅減少了元件數量,還節省了電路板空間和成本。

獨立輸出使能

每組輸出都可以通過控制輸入(1G和2G)單獨啟用或禁用。當G輸入為高電平時,輸出與CLK在相位和頻率上同步切換;當G輸入為低電平時,輸出被禁用為邏輯低電平狀態。

穩定時間要求

由于基于PLL電路,CDC509需要一定的穩定時間來實現反饋信號與參考信號的鎖相。在電源上電、CLK輸入固定頻率和固定相位信號后,以及PLL參考或反饋信號發生任何變化后,都需要這個穩定時間。為了測試目的,還可以通過將AVCC接地來繞過PLL。

功能引腳

時鐘輸入(CLK)

CLK引腳提供要由CDC509時鐘驅動器分配的時鐘信號,同時為集成的PLL提供參考信號。CLK必須具有固定的頻率和相位,以便PLL實現鎖相。

反饋輸入(FBIN)

FBIN引腳為內部PLL提供反饋信號,必須硬連接到FBOUT以完成PLL。集成的PLL會同步CLK和FBIN,使它們之間的相位誤差接近零。

輸出使能(1G和2G)

1G是輸出1Y(0:4)的使能控制,2G是輸出2Y(0:3)的使能控制。通過控制這兩個引腳的電平,可以獨立啟用或禁用相應的輸出組。

反饋輸出(FBOUT)

FBOUT專門用于外部反饋,其切換頻率與CLK相同。當外部連接到FBIN時,FBOUT完成PLL的反饋回路。

時鐘輸出(1Y(0:4)和2Y(0:3))

這些輸出提供CLK的低偏斜副本。輸出組1Y(0:4)通過1G輸入啟用,輸出組2Y(0:3)通過2G輸入啟用。通過控制相應的使能輸入,可以將這些輸出禁用為邏輯低電平狀態。

模擬電源(AVCC)

AVCC為模擬電路提供電源參考,還可以用于測試目的繞過PLL。當AVCC接地時,PLL被繞過,CLK直接緩沖到設備輸出。

模擬地(AGND)和電源地(GND)

AGND為模擬電路提供接地參考,GND為整個設備提供接地參考。

電源(VCC)

VCC為設備提供電源,推薦的工作電壓范圍為3V至3.6V。

電氣特性

絕對最大額定值

在使用CDC509時,需要注意其絕對最大額定值,如電源電壓范圍、輸入電壓范圍、輸入和輸出鉗位電流等。超過這些額定值可能會導致設備永久性損壞。

推薦工作條件

為了確保設備的正常工作,推薦的工作條件包括電源電壓、輸入電壓、輸出電流和工作溫度范圍等。例如,電源電壓應在3V至3.6V之間,工作溫度范圍為0°C至70°C。

電氣參數

文檔中還提供了詳細的電氣參數,如輸入鉗位電壓、輸出高電平和低電平電壓、輸入電流、電源電流等。這些參數對于電路設計和性能評估非常重要。

時序要求

時鐘頻率和占空比

CDC509的時鐘頻率范圍為25MHz至125MHz,輸入時鐘占空比應在40%至60%之間。

穩定時間

集成的PLL電路需要一定的穩定時間來實現反饋信號與參考信號的鎖相。在獲得鎖相之前,開關特性表中給出的傳播延遲、偏斜和抖動參數規格不適用。

開關特性

在推薦的電源電壓和工作溫度范圍內,文檔提供了開關特性參數,如相位誤差、偏斜、抖動、占空比、上升時間和下降時間等。這些參數對于評估時鐘信號的質量和性能非常關鍵。

典型特性

文檔還給出了一些典型特性曲線,如相位誤差與時鐘頻率的關系、輸出占空比與時鐘頻率的關系、模擬電源電流與時鐘頻率的關系等。這些曲線可以幫助工程師更好地了解CDC509在不同工作條件下的性能表現。

封裝信息

CDC509采用塑料24引腳薄收縮小外形封裝(TSSOP),提供了多種封裝選項,包括不同的訂購編號和相關的包裝信息。此外,文檔還提供了封裝材料信息、磁帶和卷軸尺寸、封裝外形圖、示例電路板布局和示例模板設計等,為工程師的設計和生產提供了便利。

總結

CDC509是一款功能強大、性能優異的鎖相環時鐘驅動器,適用于同步DRAM應用。其無需外部RC網絡、獨立輸出使能等特性,為電路設計帶來了很大的便利。在使用CDC509時,工程師需要注意其絕對最大額定值、推薦工作條件和時序要求等,以確保設備的正常工作和性能表現。你在實際設計中是否使用過類似的時鐘驅動器呢?遇到過哪些問題?歡迎在評論區分享你的經驗和見解。

發布評論請先 登錄

CDC509高性能、低偏斜、低抖動、鎖相環(PLL)時鐘驅動器數據表

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2509 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDC509 3.3V相位鎖定環時鐘驅動器技術文檔總結

CDC509:高性能3.3V鎖相環時鐘驅動器

CDC509:高性能3.3V鎖相環時鐘驅動器

評論