TLC2932A高性能鎖相環芯片詳解:設計與應用指南

在電子設計領域,鎖相環(PLL)是一種至關重要的電路,它能夠實現信號的相位同步和頻率合成,廣泛應用于通信、雷達、儀器儀表等眾多領域。今天要給大家介紹的是德州儀器(TI)推出的TLC2932A高性能鎖相環芯片,它具有出色的性能和豐富的功能,能為工程師們的設計帶來更多便利和可能性。

文件下載:tlc2932a.pdf

一、TLC2932A概述

TLC2932A專為鎖相環系統設計,主要由壓控振蕩器(VCO)和邊沿觸發型鑒相鑒頻器(PFD)組成。它采用CMOS技術,具有高速、穩定的振蕩能力,適合作為高性能鎖相環使用。該芯片采用薄型小外形封裝(14引腳),與TLC2932IPW引腳兼容,方便進行設計替換。

1.1 VCO特性

- 僅需一個外部偏置電阻:VCO只需一個外部偏置電阻(RBIAS)就能構成完整的振蕩器,通過改變RBIAS的值可以設置VCO的振蕩頻率范圍。

- 寬鎖相頻率范圍:在不同的電源電壓和溫度條件下,VCO具有不同的鎖相頻率范圍。例如,在VDD = 3V ± 5%,TA = -20°C至75°C,x1輸出時,鎖相頻率為13 MHz至32 MHz;在VDD = 5V ± 5%,TA = -20°C至75°C,x1輸出時,鎖相頻率為15 MHz至55 MHz。

- 可選輸出頻率:通過SELECT引腳可以選擇VCO的輸出頻率,當SELECT為高電平時,VCO輸出頻率為1/2 fOSC;當SELECT為低電平時,VCO輸出頻率為fOSC。使用1/2 fOSC輸出可以獲得最小的VCO輸出抖動。

- 抑制功能:VCO具有外部可控的抑制功能,當VCO INHIBIT引腳為高電平時,VCO停止振蕩并進入掉電模式,輸出保持低電平。

1.2 PFD特性

- 高速邊沿觸發檢測:PFD是一種高速、邊沿觸發型檢測器,內部集成了電荷泵,能夠檢測參考頻率輸入(FIN - A)和外部計數器輸出頻率輸入(FIN - B)之間的相位差。

- 獨立的掉電模式:PFD和VCO都有獨立的掉電模式,通過PFD INHIBIT引腳可以控制PFD的工作狀態,當PFD INHIBIT為高電平時,PFD輸出處于高阻態,停止相位檢測。

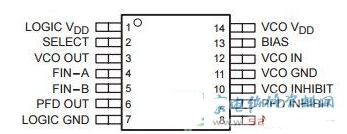

二、引腳功能與連接

| TLC2932A共有14個引腳,每個引腳都有特定的功能,下面為大家詳細介紹: | 引腳名稱 | 引腳編號 | I/O | 描述 |

|---|---|---|---|---|

| LOGIC VDD | 1 | 內部邏輯電路的電源,應與VCO VDD分開,以減少電源之間的交叉耦合。 | ||

| SELECT | 2 | I | VCO輸出頻率選擇,高電平時VCO輸出頻率為1/2 fOSC,低電平時為fOSC。 | |

| VCO OUT | 3 | O | VCO輸出,當VCO INHIBIT為高電平時,VCO輸出為低電平。 | |

| FIN - A | 4 | I | 輸入參考頻率f(REF IN)。 | |

| FIN - B | 5 | I | VCO外部計數器輸出頻率輸入,通常由外部計數器提供。 | |

| PFD OUT | 6 | O | PFD輸出,當PFD INHIBIT為高電平時,PFD輸出處于高阻態。 | |

| LOGIC GND | 7 | 內部邏輯電路的地。 | ||

| TEST | 8 | 連接到地。 | ||

| PFD INHIBIT | 9 | I | PFD抑制控制,高電平時PFD輸出處于高阻態。 | |

| VCO INHIBIT | 10 | I | VCO抑制控制,高電平時VCO停止振蕩并進入掉電模式。 | |

| VCO GND | 11 | VCO的地。 | ||

| VCO IN | 12 | I | VCO控制電壓輸入,通常連接外部環路濾波器的輸出,用于控制VCO的振蕩頻率。 | |

| RBIAS | 13 | I | 偏置電源,通過在VCO VDD和RBIAS之間連接外部電阻(RBIAS)來調整振蕩頻率范圍。 | |

| VCO VDD | 14 | VCO的電源,應與LOGIC VDD分開,以減少電源之間的交叉耦合。 |

在實際設計中,我們需要根據這些引腳的功能進行合理的連接,同時要注意電源的分離和濾波,以確保芯片的穩定工作。

三、電氣特性與性能指標

3.1 絕對最大額定值

在使用TLC2932A時,需要注意其絕對最大額定值,以避免對芯片造成永久性損壞。例如,電源電壓(VDD)最大為7V,輸入電壓范圍(VIN)為 - 0.5V至VDD + 0.5V等。具體的絕對最大額定值請參考數據手冊。

3.2 推薦工作條件

為了保證芯片的正常工作和性能,需要在推薦工作條件下使用。不同的電源電壓(VDD)對應不同的推薦工作參數,如鎖相頻率、偏置電阻等。例如,在VDD = 3V時,鎖相頻率為13 MHz至32 MHz,偏置電阻為2.2 kΩ至5.1 kΩ。

3.3 電氣特性

數據手冊中詳細給出了在不同電源電壓(VDD = 3V、3.3V、5V)和溫度(TA = 25°C)條件下的電氣特性,包括VCO和PFD的各項參數,如輸出電壓、輸入電流、輸入阻抗、電源電流等。這些參數對于我們進行電路設計和性能評估非常重要。

3.4 工作特性

- VCO工作特性:包括振蕩頻率、穩定時間、上升時間、下降時間、占空比、溫度系數、電源電壓系數和抖動等。例如,在VDD = 3V,RBIAS = 3.3 kΩ,VCO IN = 1/2 VDD時,典型振蕩頻率為25 MHz,穩定時間為10 μs。

- PFD工作特性:包括最大工作頻率、輸出禁用時間、輸出啟用時間、上升時間和下降時間等。例如,在VDD = 3V時,PFD的最大工作頻率為17 MHz。

四、典型特性曲線

數據手冊中提供了豐富的典型特性曲線,這些曲線直觀地展示了VCO振蕩頻率與控制電壓、偏置電阻、溫度、電源電壓等因素之間的關系。通過這些曲線,我們可以更好地了解芯片的性能和特性,為電路設計提供參考。

- VCO振蕩頻率與控制電壓關系:不同的電源電壓和偏置電阻下,VCO振蕩頻率隨控制電壓的變化曲線不同。例如,在VDD = 3.0V,Rbias = 2.2 kΩ時,振蕩頻率隨控制電壓的變化呈現出一定的規律。

- VCO振蕩頻率與偏置電阻關系:在不同的電源電壓和溫度條件下,VCO振蕩頻率與偏置電阻的關系也不同。例如,在VDD = 3V,VCOIN = 1.5V,Ta = 25°C時,振蕩頻率隨偏置電阻的增加而減小。

五、應用注意事項

5.1 電源設計

為了減少電源之間的交叉耦合,建議將邏輯電源(LOGIC VDD)和VCO電源(VCO VDD)分開,并使用獨立的濾波電容進行濾波。同時,要確保電源電壓在推薦工作范圍內,避免電壓波動對芯片性能產生影響。

5.2 布局設計

- 合理布線:在PCB布局時,要注意信號線的長度和走向,盡量減少信號干擾。例如,將VCO輸出線和PFD輸出線分開布線,避免相互干擾。

- 接地設計:良好的接地設計對于芯片的穩定工作至關重要。要確保邏輯地(LOGIC GND)和VCO地(VCO GND)的連接良好,避免接地環路的產生。

5.3 抖動性能

抖動性能是鎖相環系統的重要指標之一,TLC2932A的抖動性能高度依賴于電路布局和外部器件特性。在設計時,要盡量采用精心設計的PCB布局,避免使用器件插座,以減少抖動。

六、總結

TLC2932A是一款性能出色的高性能鎖相環芯片,具有寬鎖相頻率范圍、可選輸出頻率、獨立掉電模式等優點。通過合理的引腳連接、電源設計和布局設計,我們可以充分發揮該芯片的性能,滿足不同應用場景的需求。在實際設計過程中,大家要仔細閱讀數據手冊,參考典型特性曲線,結合實際應用需求進行優化設計。希望本文能對大家在使用TLC2932A進行電子設計時有所幫助。

大家在使用TLC2932A芯片的過程中遇到過哪些問題呢?又是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

電子設計

+關注

關注

42文章

1681瀏覽量

49848 -

鎖相環芯片

+關注

關注

0文章

9瀏覽量

8232

發布評論請先 登錄

鎖相環芯片TLC2932電子資料

詳解FPGA數字鎖相環平臺

TLC2932引腳圖及功能_TLC2932應用電路圖

模擬鎖相環和數字鎖相環區別

?TLC2933A 高性能鎖相環 (PLL) 芯片技術文檔摘要

?TLC2932A 高性能鎖相環芯片技術文檔摘要

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

評論