在最近的IEEE國際可靠性物理研討會上,SK海力士分享了其近期和未來的技術目標愿景。SK海力士認為,通過將層數增加到600層以上,可以繼續提高3DNAND的容量。此外,該公司有信心借助極紫外(EUV)光刻技術將DRAM技術擴展到10nm以下,以及將內存和邏輯芯片整合到同一個設備中,以應對不斷增加的工作負載。

SK海力士首席執行官李錫熙說:“我們正在改進DRAM和NAND各個領域的技術發展所需的材料和設計結構,并逐步解決可靠性問題。如果以此為基礎,并取得創新,將來有可能實現10nm以下的DRAM工藝和堆疊600層以上的NAND。”

3DNAND未來將達到600層以上

歷史的經驗早已證明,3DNAND無論是在性能還是在可拓展方面,都是一種非常高效的體系結構,因此,SK海力士將在未來幾年繼續使用它。早在2020年12月,SK海力士就推出了具有1.6Gbps接口的176層3DNAND存儲器,且已經開始和SSD控制器制造商一起開發512GB的176層存儲芯片,預計在2022年會基于新型3DNAND存儲器進行驅動。

就在幾年前,該公司認為可以將3DNAND擴展到500層左右,但是現在它已經有信心可以在不久的將來將其擴展到600層以上。隨著層數的增加,SK海力士以及其他3DNAND生產商不得不讓每一層變得更薄,NAND單元更小,并引入新的電介質材料來保持均勻電荷,從而保持可靠性。

SK海力士已經是原子層沉積領域的領導者之一,因此其下一個目標是實現高深寬比(A/R)接觸(HARC)刻蝕技術。同樣,對于600層以上的3DNAND,可能還需要學會如何將多層晶圓堆疊起來。

行業何時才能有600層以上的3DNAND設備以及如此驚人的層數將帶來的多大的容量,SK海力士沒有給出具體預測,不過該公司僅憑借176層技術就已經著眼于1TB的產品,因此600層以上的產品容量將是巨大的。

DRAM的未來:EUV低于10nm

與美光科技不同,SK海力士認為采用EUV光刻技術是保持DRAM性能不斷提高,同時提高存儲芯片容量、控制功耗最直接的方法。借助DDR5,該公司不得不推出容量超過16GB的存儲設備,數據傳輸速率可達6400GT/s,這些存儲設備將堆疊在一起以構建大容量的DRAM。

由于未來的存儲器產品必須滿足高性能、高容量以及低功耗等要求,因此先進的制造技術變得更加重要。為了成功實施EUV技術,SK海力士正在開發用于穩定EUV圖案和缺陷管理的新材料和光刻膠。另外,該公司正在尋求新的電池結構,同時通過使用由高介電常數材料制成更薄的的電介質來保持其電容。

值得注意的是,SK海力士現在也在尋找減少“用于互連的金屬”電阻的方法,這表明DRAM晶體管的尺寸已經變得非常小,以至于其觸點將成為瓶頸。借助EUV,晶體管將縮小尺寸,提升性能并降低功耗,接觸電阻將成為10nm以下的瓶頸。不同的芯片生廠商用不同的方式來解決這一問題:英特爾決定使用鈷代替鎢,而臺積電和三星則選擇了選擇性鎢沉積工藝。SK海力士未詳細說明其抗接觸電阻的方法,只是表明正在尋求下一代電極和絕緣材料并引入新工藝。

融合處理和內存的近內存處理

除了使DRAM速度更快并提高容量外,SK海力士還期待融合內存和處理技術。如今,用于超級計算機的尖端處理器使用通過插入器連接到它們的高帶寬(HBM),SK海力士將此概念稱之為PNM(近內存處理),并斷言下一步將是處理器和內存存在于單個封裝中的PIM(內存中處理),而該公司最終將尋找CIM(內存中計算),將CPU和內存集成到一起。

SK海力士的CIM在很大程度上與今年2月推出的三星PIM(內存處理)概念相似,并可能滿足HJEDEC定義的工業標準。三星的HBM-PIM將以300MHz運行的32個支持FP16的可編程計算單元(PCU)嵌入到4GB內存裸片中。可以使用常規存儲命令控制PCU,并執行一些基本計算。三星聲稱其HBM-PIM內存已經在領先的AI解決方案提供商的AI加速器中進行了試驗,該技術可以使用DRAM制造工藝制造,對于不需要高精度但可以從數量眾多的簡化內核中受益的AI和其他工作負載意義重大。

目前尚不清楚SK海力士是否將根據三星提出的即將發布的JEDEC標準實施CIM,或者采用專有技術,但可以確定的是,全球最大的DRAM制造商對融合的存儲器和邏輯設備都抱有相似的愿景。

邏輯和內存的融合對于利基應用非常有意義,同時,還有更多常見的應用程序可以從內存,存儲和處理器更緊密的集成中受益。為此,SK海力士正在開發緊密集成異構計算互連封裝技術,這些封裝包含處理IP、DRAM、NAND、微機電系統(MEMS)、射頻識別(RFID)和各種傳感器。不過,該公司尚未提供許多詳細信息。

本文由電子發燒友綜合報道,內容參考自雷鋒網,轉載請注明以上來源。

SK海力士首席執行官李錫熙說:“我們正在改進DRAM和NAND各個領域的技術發展所需的材料和設計結構,并逐步解決可靠性問題。如果以此為基礎,并取得創新,將來有可能實現10nm以下的DRAM工藝和堆疊600層以上的NAND。”

3DNAND未來將達到600層以上

歷史的經驗早已證明,3DNAND無論是在性能還是在可拓展方面,都是一種非常高效的體系結構,因此,SK海力士將在未來幾年繼續使用它。早在2020年12月,SK海力士就推出了具有1.6Gbps接口的176層3DNAND存儲器,且已經開始和SSD控制器制造商一起開發512GB的176層存儲芯片,預計在2022年會基于新型3DNAND存儲器進行驅動。

就在幾年前,該公司認為可以將3DNAND擴展到500層左右,但是現在它已經有信心可以在不久的將來將其擴展到600層以上。隨著層數的增加,SK海力士以及其他3DNAND生產商不得不讓每一層變得更薄,NAND單元更小,并引入新的電介質材料來保持均勻電荷,從而保持可靠性。

SK海力士已經是原子層沉積領域的領導者之一,因此其下一個目標是實現高深寬比(A/R)接觸(HARC)刻蝕技術。同樣,對于600層以上的3DNAND,可能還需要學會如何將多層晶圓堆疊起來。

行業何時才能有600層以上的3DNAND設備以及如此驚人的層數將帶來的多大的容量,SK海力士沒有給出具體預測,不過該公司僅憑借176層技術就已經著眼于1TB的產品,因此600層以上的產品容量將是巨大的。

DRAM的未來:EUV低于10nm

與美光科技不同,SK海力士認為采用EUV光刻技術是保持DRAM性能不斷提高,同時提高存儲芯片容量、控制功耗最直接的方法。借助DDR5,該公司不得不推出容量超過16GB的存儲設備,數據傳輸速率可達6400GT/s,這些存儲設備將堆疊在一起以構建大容量的DRAM。

由于未來的存儲器產品必須滿足高性能、高容量以及低功耗等要求,因此先進的制造技術變得更加重要。為了成功實施EUV技術,SK海力士正在開發用于穩定EUV圖案和缺陷管理的新材料和光刻膠。另外,該公司正在尋求新的電池結構,同時通過使用由高介電常數材料制成更薄的的電介質來保持其電容。

值得注意的是,SK海力士現在也在尋找減少“用于互連的金屬”電阻的方法,這表明DRAM晶體管的尺寸已經變得非常小,以至于其觸點將成為瓶頸。借助EUV,晶體管將縮小尺寸,提升性能并降低功耗,接觸電阻將成為10nm以下的瓶頸。不同的芯片生廠商用不同的方式來解決這一問題:英特爾決定使用鈷代替鎢,而臺積電和三星則選擇了選擇性鎢沉積工藝。SK海力士未詳細說明其抗接觸電阻的方法,只是表明正在尋求下一代電極和絕緣材料并引入新工藝。

融合處理和內存的近內存處理

除了使DRAM速度更快并提高容量外,SK海力士還期待融合內存和處理技術。如今,用于超級計算機的尖端處理器使用通過插入器連接到它們的高帶寬(HBM),SK海力士將此概念稱之為PNM(近內存處理),并斷言下一步將是處理器和內存存在于單個封裝中的PIM(內存中處理),而該公司最終將尋找CIM(內存中計算),將CPU和內存集成到一起。

SK海力士的CIM在很大程度上與今年2月推出的三星PIM(內存處理)概念相似,并可能滿足HJEDEC定義的工業標準。三星的HBM-PIM將以300MHz運行的32個支持FP16的可編程計算單元(PCU)嵌入到4GB內存裸片中。可以使用常規存儲命令控制PCU,并執行一些基本計算。三星聲稱其HBM-PIM內存已經在領先的AI解決方案提供商的AI加速器中進行了試驗,該技術可以使用DRAM制造工藝制造,對于不需要高精度但可以從數量眾多的簡化內核中受益的AI和其他工作負載意義重大。

目前尚不清楚SK海力士是否將根據三星提出的即將發布的JEDEC標準實施CIM,或者采用專有技術,但可以確定的是,全球最大的DRAM制造商對融合的存儲器和邏輯設備都抱有相似的愿景。

邏輯和內存的融合對于利基應用非常有意義,同時,還有更多常見的應用程序可以從內存,存儲和處理器更緊密的集成中受益。為此,SK海力士正在開發緊密集成異構計算互連封裝技術,這些封裝包含處理IP、DRAM、NAND、微機電系統(MEMS)、射頻識別(RFID)和各種傳感器。不過,該公司尚未提供許多詳細信息。

本文由電子發燒友綜合報道,內容參考自雷鋒網,轉載請注明以上來源。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

DRAM

+關注

關注

41文章

2397瀏覽量

189468 -

NAND

+關注

關注

16文章

1761瀏覽量

141230 -

光刻機

+關注

關注

31文章

1199瀏覽量

48976 -

SK海力士

+關注

關注

0文章

1008瀏覽量

41834

發布評論請先 登錄

相關推薦

熱點推薦

SK海力士攜AI存儲器產品亮相NVIDIA GTC 2026

韓國首爾,2026年3月17日——SK海力士(簡稱‘公司’,https://www.skhynix.com)17日宣布,將于3月16日至19日(當地時間)參加在美國加利福尼亞州圣何塞舉行的“英偉達GTC 2026(GPU技術大會)”。

50億美元豪賭AI未來:應用材料聯手美光、SK海力士重塑存儲芯片競賽格局

電子發燒友網綜合報道 3 月 11 日,半導體設備巨頭應用材料正式宣布,與全球存儲芯片領軍企業美光科技、SK 海力士達成戰略合作伙伴關系。三方將聚焦下一代人工智能(AI)與高效能運算(HPC)所需

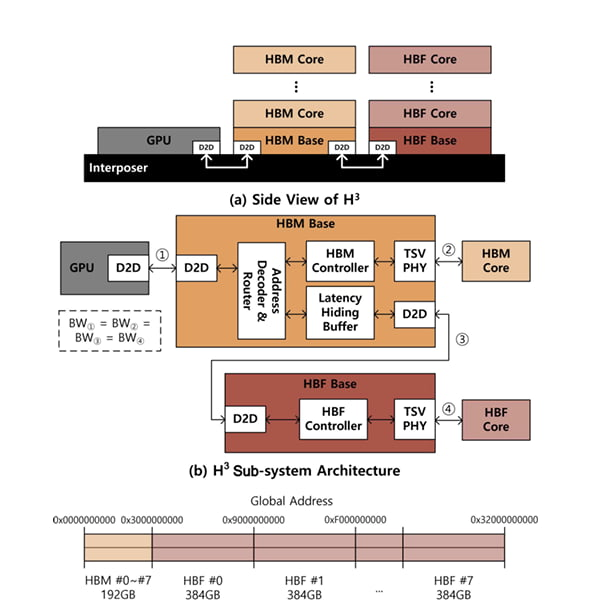

KV緩存黑科技!SK海力士“H3存儲架構”,HBM和HBF技術加持!

據韓國經濟日報報道,SK海力士近日在IEEE(電氣與電子工程師協會)全球半導體大會上發表論文,提出了一種全新的存儲架構。據悉,該架構名為“H3(hybrid semiconductor

SK海力士在CES 2026展示面向AI的下一代存儲器解決方案

SK海力士(或‘公司’)6日宣布,公司將于當地時間1月6日至9日,在美國拉斯維加斯舉辦的“CES 2026”威尼斯人會展中心設立專屬客戶展館,并集中展示面向AI的下一代存儲器解決方案。

SK海力士發布未來存儲路線圖

電子發燒友網綜合報道,近日,韓國首爾舉行的“SK AI Summit 2025”峰會上,SK海力士CEO郭魯正(Kwak Noh-Jung)正式宣布了公司向 “全線AI存儲創造者”(F

SK海力士ZUFS 4.1閃存,手機端AI運行時間縮短47%!

電子發燒友網綜合報道,SK海力士宣布,已正式向客戶供應其全球率先實現量產的移動端NAND閃存解決方案產品ZUFS 4.1。 ? SK海力士通過與客戶的密切合作,于今年6月成功完成了該產

SK海力士宣布量產HBM4芯片,引領AI存儲新變革

在人工智能(AI)技術迅猛發展的當下,數據處理與存儲能力成為制約其進一步飛躍的關鍵因素。2025 年 9 月 12 日,韓國半導體巨頭 SK 海力士宣布,已成功完成面向 AI 的超高性

SK海力士321層4D NAND的誕生

SK海力士致力于成為“全方位面向AI的存儲器供應商(Full Stack AI Memory Provider)”,不僅在DRAM領域持續創新,在NAND閃存(NAND Flash,以下簡稱NAND

SK海力士在微細工藝技術領域的領先實力

SK海力士的成功神話背后,離不開眾多核心技術的支撐,其中最令人矚目的便是“微細工藝”。通過對肉眼難以辨識的微細電路進行更為精細化的處理,SK海力士

SK海力士HBM技術的發展歷史

SK海力士在鞏固其面向AI的存儲器領域領導地位方面,HBM1無疑發揮了決定性作用。無論是率先開發出全球首款最高性能的HBM,還是確立并保持其在面向AI的存儲器市場的領先地位,這些成就的

SK海力士宋清基TL榮庸發明日銅塔產業勛章

SK海力士宣布,5月19日于首爾COEX麻谷會展中心舉行的“第60屆發明日紀念儀式”上,來自HBM開發部門的宋清基TL榮庸銅塔產業勛章。

SK海力士如何成為面向AI的存儲器市場領跑者

近年來,SK海力士屢獲創新成果,這些成就皆得益于“一個團隊”協作精神(One Team Spirit)”。無論是創下歷史最佳業績、開發出全球領先產品,還是躍升成為全球頂級面向AI的存儲器供應商,這些

英偉達供應商SK海力士盈利大增158%

得益于AI需求的有力推動;高帶寬內存(HBM)需求持續暴漲,這帶動了英偉達供應商SK海力士盈利大增158%。 據SK海力士公布的財務業績數據顯示,在2025年第一季度

SK海力士強化HBM業務實力的戰略規劃

隨著人工智能技術的迅猛發展,作為其核心支撐技術的高帶寬存儲器(以下簡稱HBM)實現了顯著的增長,為SK海力士在去年實創下歷史最佳業績做出了不可或缺的重要貢獻。業內普遍認為,

SK海力士預測未來的存儲工藝發展

SK海力士預測未來的存儲工藝發展

評論