本文是關(guān)于在印刷電路板(PCB)開發(fā)階段使用數(shù)字輸入/輸出緩沖信息規(guī)范(IBIS)模擬模型的文章。本文將介紹如何使用一個(gè)IBIS模型來提取一些重要的變量,用于信號(hào)完整性計(jì)算和確定PCB設(shè)計(jì)解決方案。請(qǐng)注意,該提取值是IBIS模型不可或缺的組成部分。

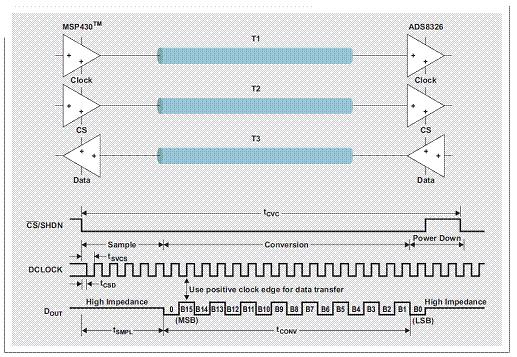

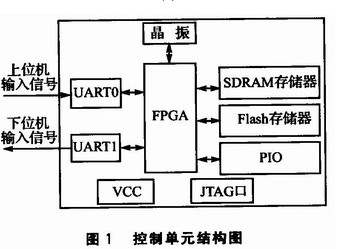

圖 1 錯(cuò)配端接阻抗PCB裝置

信號(hào)完整性問題

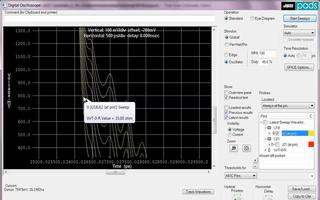

當(dāng)觀察傳輸線兩端的數(shù)字信號(hào)時(shí),設(shè)計(jì)人員會(huì)吃驚于將信號(hào)驅(qū)動(dòng)至某條 PCB 線跡時(shí)出現(xiàn)的結(jié)果。通過相對(duì)較長的距離,相比瞬時(shí)變化信號(hào),電信號(hào)更像行波。描述電路板上電波行為的較好模擬是池中波 (wave in a pool)。紋波穿過池順利傳播,因?yàn)轶w積相同的兩組水具有相同的“阻抗”。然而,池壁的阻抗差異明顯,并以相反方向反射波。注入 PCB 線跡的電信號(hào)也出現(xiàn)相同的現(xiàn)象,其在阻抗錯(cuò)配時(shí)以類似方式反射。圖 1 顯示了錯(cuò)配端接阻抗的一個(gè) PCB 裝置。微控制器即 TI MSP430? 向 TI ADS8326 ADC發(fā)送一個(gè)時(shí)鐘信號(hào),其將轉(zhuǎn)換數(shù)據(jù)發(fā)送回 MSP430。圖 2 顯示了該裝置中阻抗錯(cuò)配所形成的反射。這些反射在傳輸線跡上引起信號(hào)完整性問題。讓一端或者兩端的 PCB 線跡電阻抗相匹配可極大地減少反射。

圖 2 圖 1 中錯(cuò)配端接阻抗促發(fā)反射

要解決系統(tǒng)電阻抗匹配問題,設(shè)計(jì)人員需要理解集成電路 (IC) 的阻抗特性,以及起到傳輸線跡作用的 PCB 線跡的阻抗特性。知道這些特性,讓設(shè)計(jì)人員能夠?qū)⒏鬟B接單元建模為分布式傳輸線跡。

傳輸線跡為各種電路服務(wù),從單端和差分端器件到開漏輸出器件。本文主要介紹單端傳輸線跡,其驅(qū)動(dòng)器有一個(gè)推拉輸出電路設(shè)計(jì)。圖 3 顯示了用于設(shè)計(jì)該舉例傳輸線跡的各組成部分。

圖 3 實(shí)例單端傳輸線電路

另外,還需要如下 IC 引腳規(guī)范:

發(fā)送器輸出電阻 ZT (Ω)

發(fā)送器上升時(shí)間tRise和下降時(shí)間tFall(秒)

接收機(jī)輸入電阻ZR (Ω)

這些規(guī)范一般沒有在 IC 制造廠商的產(chǎn)品說明書中。正如這篇文章將要講到的那樣,所有這些值均可以在設(shè)計(jì) PCB 和使用模型模擬 PCB 傳輸線跡的過程中,通過 IC 的 IBIS 模型獲得。

利用下列參數(shù)定義傳輸線跡:

特性阻抗Z0 (Ω)

傳播延遲 D(ps/英寸)

線跡傳播延遲tD (ps)

線跡長度 LENGTH(英寸)

根據(jù)具體的 PCB 設(shè)計(jì),該變量清單可能會(huì)更長。例如,PCB 設(shè)計(jì)可以有一個(gè)帶多個(gè)傳輸/接收機(jī)點(diǎn)的底板。3所有傳輸線跡值均取決于特定的 PCB。一般而言,F(xiàn)R-4 板的 Z0 范圍為 50 到 75Ω,而 D 的范圍為 140 到 180 ps/英寸。Z0 和 D 的實(shí)際值取決于實(shí)際傳輸線跡的材料和物理尺寸。4特定板的線跡傳播延遲可以計(jì)算為:

tD=D × LENGTH。(1)

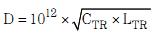

就 FR-4 板而言,線狀線的合理傳播延遲(請(qǐng)參見圖 4)為 178 ps/英寸,并且特性阻抗為 50Ω。通過測(cè)量線跡的導(dǎo)線電感和電容,并將這些值插入到下列方程式中,我們可以在板上驗(yàn)證這一結(jié)果:

(2)

(2)

或者

(3)

(3)

及

(4)

(4)

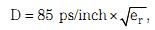

CTR 為法拉/英寸為單位的線跡導(dǎo)線電容;LTR 為享/英寸為單位的線跡導(dǎo)線電感;85 ps/英寸為空氣介電常數(shù);而 er 為材料介電常數(shù)。例如,如果微波傳輸帶-板導(dǎo)線電容為 2.6 pF/英寸,則導(dǎo)線電感為 6.4 nH/英寸,而 D=129 ps/英寸,Z0=49.4Ω。

圖 4 微帶板與帶狀線板橫截面

集總式電路與分布式電路對(duì)比

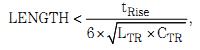

傳輸線一經(jīng)定義,下一個(gè)步驟便是確定電路布局代表集總式系統(tǒng)還是分布式系統(tǒng)。一般而言,集總式系統(tǒng)體積較小,而分布式電路則要求更多的板空間。小型電路具備有效的長度 (LENGTH),其在信號(hào)方面比最快速電氣特性要小。要成為合格的集總式系統(tǒng),PCB 上的電路必須要滿足如下要求:

(5)其中,tRise 為以秒為單位的上升時(shí)間。

在 PCB 上實(shí)施一個(gè)集總式電路以后,端接策略便不是問題了。根本上而言,我們假設(shè)傳送至傳輸導(dǎo)線中的驅(qū)動(dòng)器信號(hào)瞬間到達(dá)接收機(jī)。

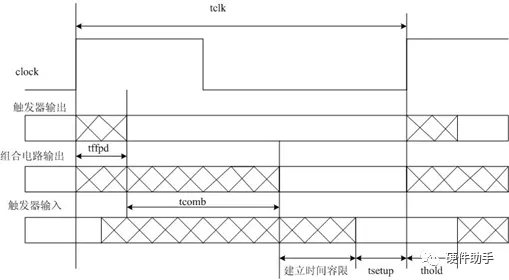

IBIS 模型的數(shù)據(jù)組織結(jié)構(gòu)

根據(jù) IC 的電源電壓范圍,一個(gè) IBIS 模型包括三、六或者九個(gè)角的數(shù)據(jù)。決定這些角的變量為硅工藝1、電源電壓和結(jié)溫。某個(gè)器件模型的具體工藝/電壓/溫度 (PVT) SPICE角對(duì)創(chuàng)建精確的 IBIS 模型至關(guān)重要。額定值不同,硅工藝也各異,創(chuàng)建的模型也有弱有強(qiáng)。設(shè)計(jì)人員根據(jù)組件的電源要求定義電壓設(shè)置,并讓其在額定值、最小值和最大值之間變化。最后,根據(jù)組件的指定溫度范圍、額定功耗和封裝的結(jié)點(diǎn)到環(huán)境熱阻,即 θJA,來確定組件硅結(jié)點(diǎn)的溫度設(shè)置。

表1列舉了一個(gè)例子,其為三 PVT 變量及其與 TI 24 位生物電勢(shì)測(cè)量 ADC ADS129x 系列的 CMOS 工藝關(guān)系。這些變量用于實(shí)施六次SPICE模擬。第一次和第四次模擬均使用額定工藝模型、額定電源電壓和室溫條件下的結(jié)點(diǎn)溫度。第二次和第五次模擬均使用弱工藝模型,低電源電壓和高結(jié)溫。第三次和第六次模擬使用強(qiáng)工藝模型、更高的電源電壓和更低的結(jié)溫。PVT值之間的關(guān)系映射CMOS工藝的最佳角。

表 1 ADS1296 IBIS 模型的 PVT 模擬角

角數(shù)硅工藝電源電壓(V)溫度(°C)

1額定1.827

2弱1.6585

3強(qiáng)2.0-40

4額定3.327

5弱3.085

6強(qiáng)3.6-40

*TI ISIS 模型標(biāo)準(zhǔn)為額定=典型、弱=最小值、強(qiáng)=最大值。

查找和/或計(jì)算發(fā)送器規(guī)范

信號(hào)完整性評(píng)估的規(guī)定發(fā)送器規(guī)范包括輸出阻抗 (ZT) 和升降時(shí)間(分別為tRise和 tFall)。圖 5 顯示了列舉自 IBIS 模型文件的 TI ADS1296 封裝ads129x.ibs。5用于產(chǎn)生阻抗的值顯示在“[Pin]”關(guān)鍵字下面,其也位于緩沖模型(未顯示)中。升降時(shí)間位于 IBIS 模型數(shù)據(jù)列表的瞬態(tài)部分。

圖 5 ADS1296的IBIS 模型封裝列表,包括 L_pin 和 C_pin 值

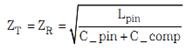

輸入和輸出引腳的阻抗

任何信號(hào)的引腳阻抗均由加至模型阻抗的封裝電感和電容組成。圖 5 中,關(guān)鍵字“[Component]”、“[Manufacturer]”和“[Package]”描述了一個(gè)具體的封裝,即64引腳PBGA(ZXG)。具體引腳的封裝電感和電容可在“[Pin]”關(guān)鍵字下面找到。例如,在引腳 5E 處,信號(hào) GPIO4,可找到 L_pin 和 C_pin 值。該信號(hào)和封裝的 L_pin(引腳電感)和 C_pin(引腳電容)值為 1.4891 nH 和 0.28001 pF。

第二個(gè)重要的電容值為硅電容,即C_comp。C_comp值可在 ads129x.ibs 文件的模型 DIO_33 列表中的“[Model]”關(guān)鍵字下面找到(參見圖 6)。該模型中的C_comp 為 DIO 緩沖器的電容,其電源引腳電壓為 3.3V。“|”符號(hào)表示注釋;因此,該列表的有效C_comp值為3.0727220e-12 F(典型值)、2.3187130e-12 F(最小值)和 3.8529520e-12 F(最大值),PCB 設(shè)計(jì)人員可從中選取。在 PCB傳輸線設(shè)計(jì)階段,3.072722 pF 典型值為正確的選擇。

圖 6 ads129x.ibs 文件 C_comp 值模型 DIO_33 列表

圖 7 端接-校正策略

輸入和輸出阻抗對(duì)信號(hào)傳輸至關(guān)重要。下列方程式定義了 IBIS 模型引腳的特性阻抗:

(6)

(6)

輸出升降時(shí)間

在整個(gè)行業(yè)中,升降時(shí)間規(guī)范的慣例是使用輸出信號(hào)在 10% 和 90% 軌至軌信號(hào)之間擺動(dòng)所需的時(shí)間,其一般為 0 到 DVDD。“IBIS 開放式論壇”的升時(shí)間定義相同,其獲得采用是由于 CMOS 開關(guān)波形尾部較長。

IBIS 模型內(nèi)的輸出、I/O 和三態(tài)模型,有一些位于“[Ramp]”關(guān)鍵字下面的規(guī)范,該關(guān)鍵字針對(duì) R_load (test load)、dV/dt_r (rise time) 和 dV/dt_f (fall time)。升降時(shí)間數(shù)據(jù)范圍為電壓-輸出信號(hào)的 20% 到 80%。如果典型 dV/dt_r 值的分母乘以 0.8/0.6,則升時(shí)間值將在 20%-80% 擺動(dòng)到 10%-90%擺 動(dòng)之間變化。請(qǐng)注意,該數(shù)據(jù)代表一個(gè)電阻性負(fù)載 (R_load) 的緩沖器。ads129x.ibs 文件中,DIO_33 數(shù)據(jù)假設(shè)為一個(gè) 50-Ω 負(fù)載,因此該數(shù)據(jù)未達(dá)到 DVDD。該計(jì)算產(chǎn)生的數(shù)值,為各種傳輸線計(jì)算提供了正確的 tRise 值,例如 fKnee、f3dB 和升沿長度。

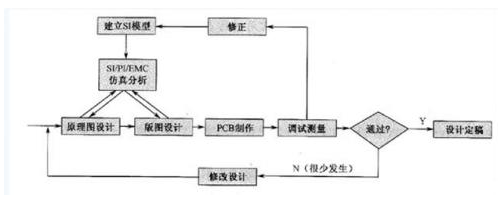

利用 IBIS 設(shè)計(jì)傳輸線

本文以討論一個(gè)錯(cuò)配端接阻抗的 PCB 作為開始。之后,我們通過 IBIS 模型,了解和查找這種傳輸問題的一些關(guān)鍵組成元素。就此而言,這種問題應(yīng)該有解決的方案。圖 7 顯示了端接校正策略,而圖 8 則顯示了校正之后的波形。

圖 8 端接校正的穩(wěn)定信號(hào)

若想設(shè)計(jì) PCB 傳輸線,第一個(gè)步驟便是從產(chǎn)品說明書收集資料。第二個(gè)步驟是檢查 IBIS 模型,找到無法從說明書中獲取的一些參數(shù)—輸入/輸出阻抗、升時(shí)間和輸入/輸出電容。在進(jìn)入到硬件階段,需利用 IBIS 模型找到一些關(guān)鍵的產(chǎn)品規(guī)范,并對(duì)最終設(shè)計(jì)進(jìn)行仿真。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論