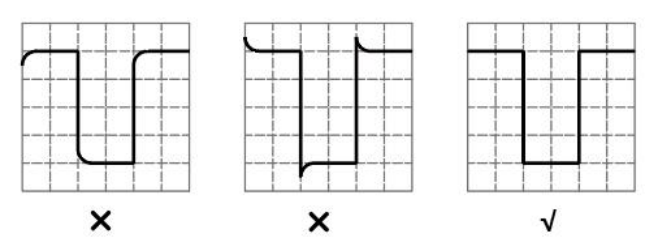

當前要創建高難度的電子產品,需要采取戰略性的方法來解決信號和電源完整性問題。在 Layout 開始之前提前研究敏感信號中存在的信號完整性問題,有助于實施布線策略、端接方法和疊層選擇,并最終減少測試工作量、降低電路板設計遍數、并縮短設計時間。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電子產品

+關注

關注

6文章

1300瀏覽量

61107 -

仿真

+關注

關注

54文章

4483瀏覽量

138278 -

布線

+關注

關注

9文章

821瀏覽量

86145

發布評論請先 登錄

相關推薦

熱點推薦

IDT信號完整性產品:解決高速信號傳輸難題

IDT信號完整性產品:解決高速信號傳輸難題 在當今的電子設備中,隨著計算、存儲和通信應用中信號速度的不斷提高,系統設計師面臨著越來越大的

PK6350無源探頭在高速數字總線信號完整性測試中的應用案例

一、應用背景 在現代電子設備架構中,PCIe、USB 3.0等高速數字總線是實現數據高速傳輸的核心載體,其信號完整性測試已成為保障設備性能穩定性與運行可靠性的關鍵環節。隨著數據傳輸速率的持續攀升

高頻PCB布線“避坑指南”:4大核心技巧讓信號完整性提升90%

一站式PCBA加工廠家今天為大家講講高頻PCB布線設計有什么技巧?高頻PCB設計布線技巧。高頻PCB布線需重點關注信號完整性、抗干擾能力及阻

技術資訊 I 信號完整性與阻抗匹配的關系

本文要點PCB走線和IC走線中的阻抗控制主要著眼于預防反射。防止互連路徑上發生反射,可確保功率傳輸至負載,同時避免其他信號完整性問題。使用集成場求解器的PCB設計軟件可以評估阻抗匹配并提取互連網

深圳 9月12-13日《信號完整性--系統設計及案例分析》公開課,即將開課!

涉及信號完整性問題。仿真或者guideline的確可以解決部分問題,但無法覆蓋全部風險點,對高危風險點失去控制經常導致設計失敗,保證設計成功需要系統化的設計方法。

羅德與施瓦茨示波器RTO2014破解信號完整性難題的全面指南

信號完整性在現代高速數字系統和通信領域中至關重要。隨著數據傳輸速率的不斷提升,信號在傳輸過程中面臨的挑戰也愈加嚴峻,如信號衰減、反射、串擾和

上海 6月20-21日《信號完整性--系統設計及案例分析》公開課,即將開課!

涉及信號完整性問題。仿真或者guideline的確可以解決部分問題,但無法覆蓋全部風險點,對高危風險點失去控制經常導致設計失敗,保證設計成功需要系統化的設計方法。

信號完整性測試基礎知識

在當今快速發展的數字時代,高速傳輸已成為電子設備的基本要求。隨著數據傳輸速率的不斷提升,信號完整性(Signal Integrity,簡稱SI)問題變得越來越重要。信號完整性是高速互連

普源示波器在信號完整性分析中的應用研究

信號完整性(Signal Integrity, SI)是電子工程領域中一個至關重要的概念,它指的是信號在傳輸過程中保持其原始特征的能力。在高速數字電路和通信系統中,

布線前仿真解決設計中存在的信號完整性問題

布線前仿真解決設計中存在的信號完整性問題

評論