使用hyperlynx?可以輕松定位和修復(fù)pcb信號(hào)完整性問題。從PCB布局導(dǎo)出設(shè)計(jì)后,可以在批處理模式下運(yùn)行模擬和/或交互模式以查找信號(hào)完整性問題。內(nèi)置終結(jié)器向?qū)Э梢苑治鐾負(fù)洳⑼扑]最佳終止方式。可以看到終止符直接在boardsim操作中使用快速終止符。您還可以導(dǎo)出信號(hào)或信號(hào)線SIM,以便進(jìn)一步分析。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424231 -

拓?fù)?/span>

+關(guān)注

關(guān)注

4文章

352瀏覽量

30478 -

布局

+關(guān)注

關(guān)注

5文章

272瀏覽量

25840

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

IDT信號(hào)完整性產(chǎn)品:解決高速信號(hào)傳輸難題

IDT信號(hào)完整性產(chǎn)品:解決高速信號(hào)傳輸難題 在當(dāng)今的電子設(shè)備中,隨著計(jì)算、存儲(chǔ)和通信應(yīng)用中信號(hào)速度的不斷提高,系統(tǒng)設(shè)計(jì)師面臨著越來越大的信號(hào)

PK6350無(wú)源探頭在高速數(shù)字總線信號(hào)完整性測(cè)試中的應(yīng)用案例

,信號(hào)反射、串?dāng)_、時(shí)序偏差等信號(hào)完整性問題愈發(fā)凸顯,直接影響設(shè)備的傳輸效率與工作穩(wěn)定性。 因此,對(duì)高速數(shù)字總線的信號(hào)完整性進(jìn)行精準(zhǔn)測(cè)量與深度

技術(shù)資訊 I 信號(hào)完整性與阻抗匹配的關(guān)系

本文要點(diǎn)PCB走線和IC走線中的阻抗控制主要著眼于預(yù)防反射。防止互連路徑上發(fā)生反射,可確保功率傳輸至負(fù)載,同時(shí)避免其他信號(hào)完整性問題。使用集成場(chǎng)求解器的PCB設(shè)計(jì)軟件可以評(píng)估阻抗匹配并

揭秘高頻PCB設(shè)計(jì):體積表面電阻率測(cè)試儀如何確保信號(hào)完整性

在高頻 PCB 的設(shè)計(jì)與應(yīng)用中,信號(hào)完整性是決定設(shè)備性能的核心,無(wú)論是通信基站、雷達(dá)系統(tǒng)還是高端電子設(shè)備,都依賴高頻 PCB 中信號(hào)的穩(wěn)定傳

串?dāng)_如何影響信號(hào)完整性和EMI

歡迎來到 “掌握 PCB 設(shè)計(jì)中的 EMI 控制” 系列的第六篇文章。本文將探討串?dāng)_如何影響信號(hào)完整性和 EMI,并討論在設(shè)計(jì)中解決這一問題的具體措施。

深圳 9月12-13日《信號(hào)完整性--系統(tǒng)設(shè)計(jì)及案例分析》公開課,即將開課!

課程名稱:《信號(hào)完整性--系統(tǒng)化設(shè)計(jì)方法及案例分析》講師:于老師時(shí)間地點(diǎn):深圳9月12-13日主辦單位:賽盛技術(shù)課程特色信號(hào)完整性是內(nèi)嵌于PCB

羅德與施瓦茨示波器RTO2014破解信號(hào)完整性難題的全面指南

的測(cè)試儀器,為解決這些信號(hào)完整性難題提供了強(qiáng)大的支持。以下是利用RTO2014破解信號(hào)完整性難題的詳細(xì)方法。 ? 一、了解信號(hào)

了解信號(hào)完整性的基本原理

作者:Cece Chen 投稿人:DigiKey 北美編輯 隨著支持人工智能 (AI) 的高性能數(shù)據(jù)中心的興起,信號(hào)完整性 (SI) 變得至關(guān)重要,這樣才能以更高的速度傳輸海量數(shù)據(jù)。為確保信號(hào)

上海 6月20-21日《信號(hào)完整性--系統(tǒng)設(shè)計(jì)及案例分析》公開課,即將開課!

課程名稱:《信號(hào)完整性--系統(tǒng)化設(shè)計(jì)方法及案例分析》講師:于老師時(shí)間地點(diǎn):上海6月20-21日主辦單位:賽盛技術(shù)課程特色信號(hào)完整性是內(nèi)嵌于PCB

受控阻抗布線技術(shù)確保信號(hào)完整性

核心要點(diǎn)受控阻抗布線通過匹配走線阻抗來防止信號(hào)失真,從而保持信號(hào)完整性。高速PCB設(shè)計(jì)中,元件與走線的阻抗匹配至關(guān)重要。PCB材料的選擇(如

信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

在當(dāng)今快速發(fā)展的數(shù)字時(shí)代,高速傳輸已成為電子設(shè)備的基本要求。隨著數(shù)據(jù)傳輸速率的不斷提升,信號(hào)完整性(Signal Integrity,簡(jiǎn)稱SI)問題變得越來越重要。信號(hào)完整性是高速互連

技術(shù)資訊 | 信號(hào)完整性測(cè)試基礎(chǔ)知識(shí)

本文重點(diǎn)信號(hào)完整性測(cè)試需要從測(cè)試電路板和原型獲取實(shí)驗(yàn)數(shù)據(jù)并加以分析。在理想的工作流程中,還會(huì)仿真信號(hào)完整性指標(biāo),并將其與實(shí)際測(cè)量值進(jìn)行比較。信號(hào)

普源示波器在信號(hào)完整性分析中的應(yīng)用研究

信號(hào)完整性(Signal Integrity, SI)是電子工程領(lǐng)域中一個(gè)至關(guān)重要的概念,它指的是信號(hào)在傳輸過程中保持其原始特征的能力。在高速數(shù)字電路和通信系統(tǒng)中,信號(hào)

電源完整性理論基礎(chǔ)

隨著 PCB 設(shè)計(jì)復(fù)雜度的逐步提高,對(duì)于信號(hào)完整性的分析除了反射,串?dāng)_以及 EMI 之外,穩(wěn)定可靠的電源供應(yīng)也成為設(shè)計(jì)者們重點(diǎn)研究的方向之一。尤其當(dāng)開關(guān)器件數(shù)目不斷增加,核心電壓不斷減小的時(shí)候,電源

發(fā)表于 03-10 17:15

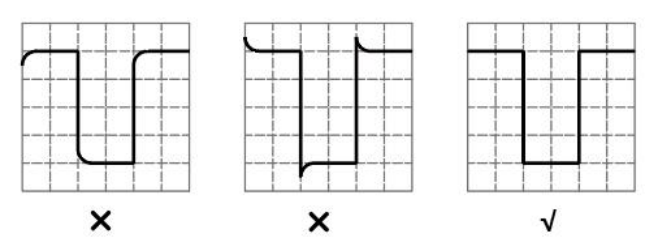

識(shí)別和修復(fù)pcb信號(hào)完整性問題

識(shí)別和修復(fù)pcb信號(hào)完整性問題

評(píng)論