您可以利用 IBIS 模型提取出一些重要的變量,用于進行信號完整性計算和尋找 PCB 設計的解決方案。您從 IBIS 模型提取的各種值是信號完整性設計計算不可或缺的組成部分。

2012-02-06 10:42:48 2276

2276

PCB中信號完整性分析的基礎知識可能不是基本的。信號完整性仿真工具非常適合在原理圖和布局設計期間計算不同網絡中信號的行為,但您仍然需要采取一些步驟來解釋結果。

2023-06-09 10:31:57 1534

1534

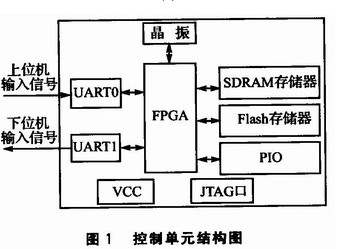

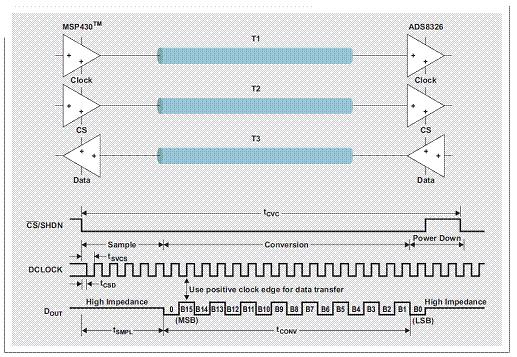

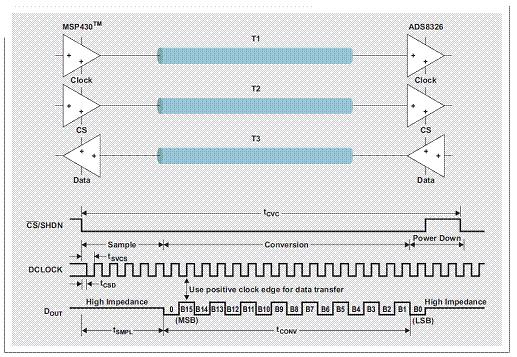

解釋完帶寬這一概念,我們來考慮如何才能通過仿真準確的預測信號完整性。 信號帶寬的確定、器件模型的獲取 當我們確定了要分析的信號的信息(包含速率、接口電平、上升時間等等)、以及驅動器和接收器型號之后

2025-01-22 11:51:07 2575

2575

在您努力想要穩定板上的各種信號時, 信號完整性 問題會帶來一些麻煩。IBIS 模型是解決這些問題的一種簡單方法。您可以利用 IBIS 模型提取出一些重要的變量,用于進行信號完整性計

2012-05-08 09:45:59 2244

2244

阻抗測試原理,典型的TDR 應用和測試;TDR 進行信號完整性建模和分析。分析各種單網絡的拓撲設計、各種單網絡模型分析;互連阻抗臺階、感性、容性突變下的多種反射現象及其匹配補償對策。第六講 有損線帶

2010-12-16 10:03:11

做了電路設計有一段時間,發現信號完整性不僅需要工作經驗,也需要很強的理論指導,壇友能提供一些信號完整性的視頻資料么?非常感謝!

2019-02-14 14:43:52

在altium designer中想進行信號完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

的影響,要求能夠同時執行信號完整性分析和電源完整性分析。驅動器的SPICE模型傳統上用于執行此類分析,但更新的IBIS模型也具有相應的基礎架構,以包括在查找信號完整性時的PDN影響。信號完整性和電源完整性

2019-06-17 10:23:53

信號完整性分析

2013-06-04 14:26:04

信號完整性分析

2013-06-04 14:36:09

信號完整性分析,很不錯的教材可以下載看一看。

2016-06-23 18:45:23

信號完整性資料

2015-09-18 17:26:36

很不錯的一本信號完整性教材。其實EMC、EMI問題最終都是信號完整性問題。

2011-12-09 22:49:23

信號完整性分析與設計信號完整性設計背景???什什么是信號完整D??信信號完整性設計內è??典典型信號完整性問題與對2現在數字電路發展的趨ê??速速率越來越???芯芯片集成度越來越高£PC板板越來越

2009-09-12 10:20:03

高速設計中的信號完整性和電源完整性分析

2021-04-06 07:10:59

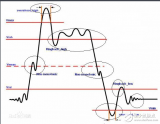

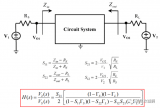

及電源互聯的等效模型。驅動電路和接收電路采用了IBIS模型(也可以用SPICE模型來替代)。利用該仿真電路,可以觀察到一個虛擬系統工作時任一點的信號波形或電源波動狀況。信號完整性通常關心的是時鐘信號的抖動

2015-01-07 11:33:53

信號完整性與電源完整性的仿真分析與設計,不看肯定后悔

2021-05-12 06:40:35

其實電源完整性可做的事情有很多,今天就來了解了解吧。信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領域相關的分析,涉及數字電路正確操作。在信號完整性中,重點是確保傳輸

2021-11-15 07:37:08

信號完整性的定義信號完整性包含哪些內容

2021-03-04 06:09:35

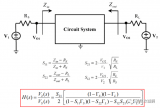

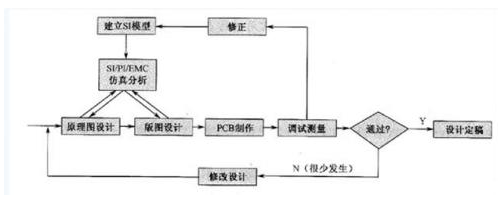

不可避免的。5、為了發現、修正和防止信號完整性問題,必須將物理設計轉化為等效的電路模型并用這個模型來仿真出波形,以便在制造產品之前預測其性能。6、使用三種級別的分析來計算電氣效應一經驗法則、解析近似和數

2015-12-12 10:30:56

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

印制板)和系統的核心技術就是微波背景下的互連設計與信號完整性分析。全世界高速高密度電路的發展表明:互連正在取代器件,躍升為高速電路設計的主角。信號完整性分析是高速互連設計的支撐與保障。要想精通高速

2010-05-29 13:29:11

AD信號完整性分析的資料,需要用到AD信號完整性分析的同學可以下載下來看看,資料講得挺詳細的!

2016-04-19 16:53:48

反射和串擾的分析結果。Altium Designer的信號完整性分析采用IC器件的IBIS模型,通過對版圖內信號線路的阻抗計算,得到信號響應和失真等仿真數據來檢查設計信號的可靠性。Altium

2015-12-28 22:25:04

,而且可以縮短產品開發周期,降低開發成本。在數字系統向高速、高密度方向發展的情況下,掌握這一設計利器己十分迫切和必要。在信號完整性分析的模型及計算分析算法的不斷完善和提高上,利用信號完整性進行計算機

2018-11-27 15:22:34

準確的模型,同時考慮了封裝的寄生參數與ESD結構; 提供比結構化的方法更快的仿真速度;可用于系統板級或多板信號完整性分析仿真。可用IBIS模型分析的信號完整性問題包括:串擾、反射、振蕩、上沖、下沖

2014-11-20 10:31:44

`編輯推薦《國外電子與通信教材系列:信號完整性與電源完整性分析(第二版)》強調直覺理解、實用工具和工程素養。作者以實踐專家的視角指出造成信號完整性問題的根源,并特別給出了設計階段前期的問題解決

2017-09-19 18:21:05

`編輯推薦本書全面論述了信號完整性與電源完整性問題。主要講述信號完整性分析及物理設計概論,6類信號完整性問題的實質含義,物理互連設計對信號完整性的影響,電容、電感、電阻和電導的特性分析,求解信號

2017-08-08 18:03:31

PCB為范例,詳盡講解了IBIS模型的建立、高速PCB的預布局、拓撲結構的提取、反射分析、竄擾分析、時序分析、約束驅動布線、后布線DRC分析、差分對設計等信號完整性分析,以及目標阻抗、電源噪聲、去耦電容器

2017-07-18 18:12:07

什么時候需要進行信號完整性分析

2014-12-10 10:30:11

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

本文是關于在印刷電路板 (PCB) 開發階段使用數字輸入/輸出緩沖信息規范 (IBIS) 模擬模型的文章。本文將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定 PCB

2011-09-13 09:28:36

模型在信號完整性分析工作中的作用也越來越得到重視。 元器件模型通常包括IBIS模型和Spice模型。由于板級仿真只關心輸出管腳經過互聯系統到輸入管腳的信號響應,同時IC廠家不希望泄漏器件內部詳細

2018-09-11 15:19:49

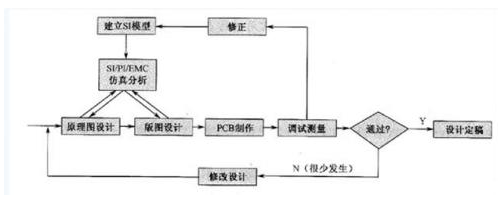

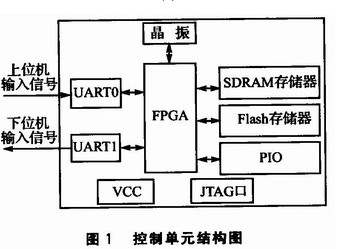

或獲取高速數字信號傳輸系統各個環節的信號完整性模型。 (2)在設計原理圖過程中,利用信號完整性模型對關鍵網絡進行信號完整性預分析,依據分析結果來選擇合適的元器件參數和電路拓撲結構等。 (3)在

2018-09-03 11:18:54

采取有效的控制措施,提高電路設計質量,是必須考慮的問題。借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法

2015-01-07 11:30:40

PCB設計的SI模型 在電子設計中已經有多種可以用于PCB板級信號完整性分析的模型。其中最為常用的有三種,分別是SPICE、IBIS和Verilog-A。 a. SPICE模型 SPICE

2018-08-29 16:28:48

PCB設計的SI模型 在電子設計中已經有多種可以用于PCB板級信號完整性分析的模型。其中最為常用的有三種,分別是SPICE、IBIS和Verilog-A。 a. SPICE模型 SPICE

2008-06-14 09:14:27

摘 要:從信號完整性分析設計規則、完整性分析仿真器、波形分析器等三個方面說明了如何利用Protel 99的信號完整性分析功能進行印刷電路板的設計。 關鍵詞:信號完整性;電磁干擾;波形

2018-08-27 16:13:55

本文是關于在印刷電路板 (PCB) 開發階段使用數字輸入/輸出緩沖信息規范 (IBIS) 模擬模型的文章。本文將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定 PCB 設計解決方案。

2021-04-21 06:10:21

的高速數字系統設計分析不僅能夠有效地提高產品的性能,而且可以縮短產品開發周期,降低開發成本。在數字系統向高速、高密度方向發展的情況下,掌握這一設計利器己十分迫切和必要。在信號完整性分析的模型及計算分析

2018-07-31 17:12:43

何為信號完整性?信號完整性包括哪些?干擾信號完整性的因素有哪些?如何去解決?

2021-05-06 07:00:23

信號完整性分析使用的軟件是Altium Designer ;我設計的PCB是一個連接板,器件包含三個不同型號的連接器,以及若干電容電阻,連接器分別連接了幾個芯片器件;我使用的IBIS模型借鑒于芯片

2019-05-26 15:45:31

信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領域相關的分析,涉及數字電路正確操作。在信號完整性中,重點是確保傳輸的1在接收器中看起來就像 1(對0同樣如此)。在電源

2021-11-15 06:31:24

最近學習信號完整性分析,急需6N137、OP17、SN74LVC4245A、INA128等元件的IBIS模型,在網上瀏覽了幾天一無所獲,跪請大神恩賜

2017-12-06 10:03:53

最近學習信號完整性分析,急需6N137、OP17、SN74LVC4245A、INA128等元件的IBIS模型,在網上瀏覽了幾天一無所獲,跪請大神恩賜

2017-12-06 10:02:09

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

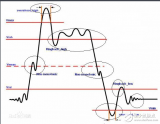

高速電路信號完整性分析與設計—信號完整性仿真仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上升沿從20%~80%VCC的時間,一般是ns級或

2009-09-12 10:31:31

摘要! 介紹了高速+,& 設計中的信號完整性概念以及破壞信號完整性的原因!從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因!并介紹了-&-. 仿真"關鍵詞!

2008-10-15 08:15:02 0

0 高速電路信號完整性分析與設計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 信號完整性原理分析

什么是“信號完整性”?在傳統的定義中“完整性(integrity)”指完整和末受損的意思。因此,具有良好完整性的數字信號應是干凈,

2009-11-04 12:07:06 212

212 針對高速數字電路印刷電路板的板級信號完整性, 分析了IBIS 模型在板級信號完整性分析中的作用。利用ADS 仿真軟件, 采用電磁仿真建模和電路瞬態仿真測試了某個實際電路版

2010-08-23 17:18:04 39

39 什么是信號完整性

信號完整性(Signal Integrity):就是指電路系統中信號的

2009-06-30 10:23:18 5717

5717

本文是關于在印刷電路板 (PCB) 開發階段使用數字輸入/輸出緩沖信息規范 (IBIS) 模擬模型的文章。本文將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定

2011-09-15 10:13:33 1401

1401

為了使設計人員對信號完整性與電源完整性有個全面的了解,文中對信號完整性與電源完整性的問題進行了仿真分析與設計,也從系統的角度對其進行了探討。

2011-11-30 11:12:24 0

0 本專題詳細介紹了信號完整性各部分知識,包括信號完整性的基礎概述,信號完整性設計分析及仿真知識,還有具體應用中的一些小經驗分享等等,充分翔實的向大家描述了信號完整性。

2011-11-30 11:44:35

回流路徑與傳輸線模型建構及信號完整性分析

2011-12-20 17:37:57 53

53 在您努力想要穩定板上的各種信號時,信號完整性問題會帶來一些麻煩。IBIS 模型是解決這些問題的一種簡單方法。您可以利用 IBIS 模型提取出一些重要的變量,用于進行信號完整性計算

2012-01-14 12:58:55 1585

1585

2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:26:07 102

102 2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:21:42 2038

2038 仿真設計可行性和有效性取決于模型的建立,本章在介紹SPICE仿真模型基本原理及其存在的主要問題的基礎上,重點介紹IBIS模型原理和應用。 10.1 SPICE仿真模型原理與使用 10.1.1 SPICE模型

2012-05-29 14:17:45 2539

2539

TI 正在開發一套新的數字輸入/輸出緩沖器信息規范 (IBIS) 仿真模型,旨在滿足各種客戶需求。這種模型(請參見圖 1)可用于仿真環境中,幫助解決諸如板級過沖、欠沖或者串擾等問題

2013-03-19 15:27:12 51

51 信號完整性分析 美國Eric教授著作,李玉山教授編譯

2015-11-11 16:51:55 0

0 本書全面論述了信號完整性問題。主要講述了信號完整性和物理設計概論,帶寬、電感和特性阻抗的實質含義,電阻、電容、電感和阻抗的相關分析,解決信號完整性問題的四個實用技術手段,物理互連設計對信號完整性

2015-11-10 17:36:24 0

0 信號完整性分析(英文版)!資料來源網絡,如有侵權,敬請見諒

2015-11-19 14:51:31 0

0 信號完整性分析基礎知識——很不錯的學習內容

2016-01-06 14:35:06 0

0 信號完整性是指信號在通過一定距離的傳輸路徑后在特定接收端口相對指定發

送端口信號的還原程度。在討論信號完整性設計性能時,如指定不同的收發參考端

口,則對信號還原程度會用不同的指標來描述。

2016-02-19 16:41:51 0

0 信號完整性分析,有需要的朋友可以下來看看

2016-02-19 16:48:21 0

0 電地完整性、信號完整性分析導論,有需要的下來看看

2016-02-22 16:18:01 71

71 Avago Technologies信號完整性分析基礎知識

2016-06-01 17:48:06 0

0 10129@52RD_信號完整性與電源完整性的仿真分析與設計

2016-12-14 21:27:39 0

0 信號完整性是指信號在傳輸路徑上的質量,由于路徑的特性對信號造成的失真。數字電路剛出現的時候,由于傳輸信號速率很低,在電路分析時采用低頻和直流的方法就可以。

2017-11-03 15:52:36 88456

88456

數字信號傳輸系統各個環節的信號完整性模型。 (2)在設計原理圖過程中,利用信號完整性模型對關鍵網絡進行信號完整性預分析,依據分析結果來選擇合適的元器件參數和電路拓撲結構等。 (3)在原理圖設計完成后,結合PCB的疊層設計參數和原理圖

2017-12-04 10:46:30 0

0 本文的主要內容是將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定 PCB 設計解決方案。

2018-05-29 14:10:01 27

27 借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發現信號完整性問題,根據仿真結果在信號完整性相關問題上做出優化的設計,從而達到提高設計質量,縮短設計周期的目的。

2019-01-21 15:13:47 1547

1547

在基于信號完整性計算機分析的PCB設計方法中,最為核心的部分就是pcb板級信號完整性模型的建立,這是與傳統的設計方法的區別之處。SI模型的正確性將決定設計的正確性,而SI模型的可建立性則決定了這種設計方法的可行性。

2019-06-24 15:22:49 5816

5816 本文是關于在印刷電路板(PCB)開發階段使用數字輸入/輸出緩沖信息規范(IBIS)模擬模型的文章。本文將介紹如何使用一個IBIS模型來提取一些重要的變量,用于信號完整性計算和確定PCB設計解決方案。請注意,該提取值是IBIS模型不可或缺的組成部分。

2019-06-20 15:29:31 3101

3101

借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發現信號完整性問題,根據仿真結果在信號完整性相關問題上做出優化的設計,從而達到提高設計質量,縮短設計周期的目的。

2019-05-20 15:25:37 1542

1542

(1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立或獲取高速數字信號傳輸系統各個環節的信號完整性模型。

(2)在設計原理圖過程中,利用信號完整性模型對關鍵網絡進行信號完整性預分析,依據分析結果來選擇合適的元器件參數和電路拓撲結構等。

2019-10-11 14:52:33 2515

2515

信號完整性與電源完整性的仿真(5V40A開關電源技術參數)-信號完整性與電源完整性的仿真分析與設計!!!

2021-09-29 12:11:21 91

91 信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領域相關的分析,涉及數字電路正確操作。在信號完整性中,重點是確保傳輸的1在接收器中看起來就像 1(對0同樣如此)。在電源

2021-11-08 12:20:59 64

64 信號完整性測試-材料熱分析

2021-11-08 18:14:46 80

80 介紹了高速PCB設計中的信號完整性概念以及破壞信號完整性的原因,從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因,并介紹了IBIS仿真。

2021-12-17 13:47:07 1

1 首先我們定義下什么是電源和信號完整性?信號完整性 信號完整性(SI)分析集中在發射機、參考時鐘、信道和接收機在誤碼率(BER)方面的性能。電源完整性(PI)側重于電源分配網絡 (PDN) 提供恒定

2022-01-07 15:34:31 24

24 高速電路信號完整性分析與設計—端接與拓撲

2022-02-10 16:38:28 0

0 高速電路信號完整性分析與設計—時序計算

2022-02-10 17:16:41 0

0 高速電路信號完整性分析與設計—信號完整性仿真

2022-02-10 17:29:52 0

0 定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

2022-11-16 14:56:00 6200

6200 現有產品設計對信號完整性很重視,但對于電源完整性的重視好像不夠,主要是因為,對于低頻應用,開關電源的設計更多靠的是經驗,或者功能級仿真來輔助即可

2023-04-10 09:16:16 3570

3570 何為信號完整性的分析信號完整性包含:波形完整性(Waveformintegrity)時序完整性(Timingintegrity)電源完整性(Powerintegrity)信號完整性分析的目的就是用

2023-08-17 09:29:30 8719

8719

電子發燒友網站提供《信號完整性與電源完整性-電源完整性分析.pdf》資料免費下載

2024-08-12 14:31:17 117

117 電子發燒友網站提供《高速PCB信號完整性分析及應用.pdf》資料免費下載

2024-09-21 14:14:34 7

7 高速PCB信號完整性設計與分析

2024-09-21 11:51:47 4

4 2024年12月20日14:00-16:00中星聯華科技將舉辦“高速信號完整性分析與測試”-“碼”上行動系列線上講堂線上講堂。本期會議我們將為大家介紹高速串行總線傳輸基本框架,什么是信號完整性?高速

2024-12-15 23:33:31 1135

1135

本文聚焦IBIS(I/O Buffer Information Specification)模型中的Corner(Typ/Min/Max)參數處理,系統分析Corner的定義規則及其對信號完整性

2025-04-23 16:10:37 1109

1109

電子發燒友App

電子發燒友App

評論