頻率范圍從50 MHz到高達3 GHz的信號被視為高速信號,例如時鐘信號。理想情況下,時鐘信號是方波,但實際上不可能立即將其“低”電平更改為“高”電平(反之亦然)。它具有特定的上升和下降時間,因此在時域中似乎是梯形的。值得注意的是,時鐘信號的高頻諧波在頻域中的幅度取決于其上升和下降時間。如果上升時間大于諧波的幅度,則諧波的幅度將變小。

為什么在高頻總是會有信號失真?

在低頻(> 1kHz)下,信號保持在數據表征范圍內,并且系統按預期運行。當速度增加時,就會產生更高的頻率影響,從而導致振鈴,串擾,反射,接地反彈和阻抗失配問題。它不僅影響系統的數字屬性,而且還會影響模擬屬性。這些問題更容易增加I / O接口和內存接口的數據速率。實際上,可以通過采用高級PCB設計服務或遵循嚴格的布局指南來避免這些問題。信號布線,端接方案和電源分配技術可以幫助設計人員實現有效的PCB。

在高速PCB設計中,何時需要注意信號完整性?

信號完整性:理想地,在PCB中,信號應不受干擾/不受干擾地從信號源(Tx)傳輸至負載(Rx)。但實際上,這不會發生。信號以一些損耗(阻抗失配,串擾,衰減,反射,開關問題)到達負載。信號完整性(SI)是定義為在高頻狀態下測量這些信號失真的術語。信號完整性通過提供實用的解決方案有助于預測和理解這些關鍵問題。

高速PCB設計要求將跡線可視化為傳輸線,而不是簡單的導線。確定設計中的最高工作頻率有助于確定應視為傳輸線的走線。如果走線超過該頻率波長的大約1/10 ,則可以將其視為傳輸線。這些傳輸線需要數字和模擬分析。

PCB基板:PCB構造期間使用的基板材料會導致信號完整性問題。每個PCB基板具有不同的相對介電常數(εr )值。它決定了將信號走線視為傳輸線的長度,當然,在這種情況下,設計人員需要注意信號完整性威脅。

利用εr值,設計人員可以評估信號流動的速度(V p )和傳播延遲( t PD)。這些參數有助于確定應將走線視為傳輸線的長度。描述了插入損耗如何隨信號頻率增加。對于FR-4(玻璃環氧樹脂)和高頻Rogers RO4350B材料,測量插入損耗(每英寸)。較高的插入損耗可能導致更大的衰減。

克服高速PCB設計中信號完整性問題的技術

設計人員可以在高速PCB中實現以下設計技術:

1.高速PCB設計中的阻抗匹配

此參數對于更快和更長的跟蹤運行很重要。影響阻抗控制的三個因素是基板材料,走線寬度和走線距地面/電源層的高度。

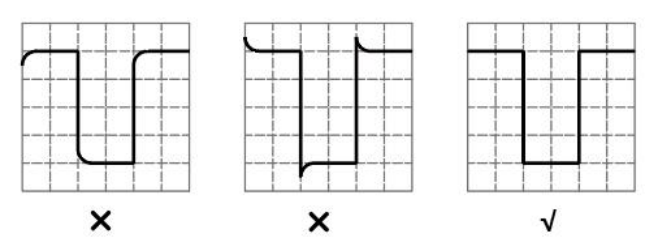

在低頻下,PCB軌跡由其直流特性定義。它可以被認為是理想的電路,沒有電阻,電容和電感。當頻率上升時,與磁場相關的電感和電容開始影響其性能。由于過孔短線導致的走線阻抗不匹配,以及走線中的瑕疵無法使信號在接收器(負載)中被完全吸收。這就是為什么多余的能量會反射到發射器(源)的原因。這個過程一次又一次地重復直到所有能量被吸收為止。在高數據速率下,它會導致信號過沖,下沖和振鈴,從而產生信號錯誤。為了解決該問題,這些傳輸線在其下方設置有接地平面以及終端電阻。

計算線路的阻抗很重要。(它是通過將線的粗細,電路板的介電常數以及線與地平面之間的距離結合起來計算得出的。)有時,傳輸線需要在不同的層之間穿行,因此,線與接地層之間的距離也要經過地平面發生變化。在這種情況下,通過改變線寬可以將線阻抗保持在相同的值。

注意:對于高頻,高速設計,PCB軌跡被視為傳輸線。

高速PCB設計中的阻抗控制措施

阻抗失配可以通過實施適當的端接方案來控制。終止方案的選擇取決于應用。讓我們討論其中的一些。

1.并聯終端方案:在該方案中,終端電阻(RT)等于線路阻抗。該終端電阻放置在盡可能靠近負載的位置,以實現最大效率。在高輸出狀態下,此終端電阻的電流負載最大。

2戴維寧端接方案:這是并行端接方案的替代方案,在該方案中,端接電阻器(RT)分為兩個獨立的電阻器,它們等于線路阻抗(組合時)。該方案減少了從電源汲取的總電流,并增加了從電源汲取的電流,因為電阻器放置在VCC與地之間。

3 有源并聯終端:此處,等于線路阻抗(Z0)的終端電阻放置在偏置電壓路徑中。設置偏置電壓,以便輸出驅動器可以從高電平和低電平信號中提取電流。該技術需要一個單獨的電壓源,該電壓源可以吸收和提供電流以匹配輸出傳輸速率。

4 串聯-RC并聯終端:在該方案中,電阻和電容器(> 100pF)的組合用作終端阻抗。此處,終端電阻(RT)等于Z0,電容器阻隔了低頻信號分量并使高頻分量通過。因此,RT的直流負載效應不會影響驅動器。

5 串聯終端:它匹配信號源上的阻抗,而不是負載上的阻抗。該方案有助于衰減二次反射。線路阻抗根據負載的分布而變化。因此,一個電阻值并不適用于所有情況。這種方法僅在源處需要一個組件,而在每個負載中不需要多個組件,但是通過增加RC時間常數來延遲信號路徑。

6 差分對終端:在接收設備的信號之間需要一個終端電阻。終端電阻必須與差分負載阻抗(通常為100Ω)匹配。

責任編輯:tzh

-

電源

+關注

關注

185文章

18923瀏覽量

264175 -

pcb

+關注

關注

4411文章

23916瀏覽量

425440 -

電阻器

+關注

關注

22文章

4243瀏覽量

65557

發布評論請先 登錄

IDT信號完整性產品:解決高速信號傳輸難題

Samtec高速線纜深入解析:高速信號完整性的關鍵技術

高頻PCB布線“避坑指南”:4大核心技巧讓信號完整性提升90%

技術資訊 I 信號完整性與阻抗匹配的關系

揭秘高頻PCB設計:體積表面電阻率測試儀如何確保信號完整性

深圳 9月12-13日《信號完整性--系統設計及案例分析》公開課,即將開課!

上海 6月20-21日《信號完整性--系統設計及案例分析》公開課,即將開課!

如何克服高速PCB設計中信號完整性問題?

如何克服高速PCB設計中信號完整性問題?

評論