采用電感耦合等離子體刻蝕法對(duì)氮化鎵基發(fā)光二極管結(jié)構(gòu)進(jìn)行干法刻蝕,刻蝕氣體為氯氣,添加氣體為三氯化硼。研究了刻蝕氣體流量、電感耦合等離子體功率、射頻功率和室壓等關(guān)鍵工藝參數(shù)對(duì)氮化鎵基發(fā)光二極管結(jié)構(gòu)刻蝕

2022-04-26 14:07:28 2863

2863

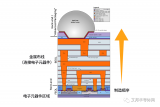

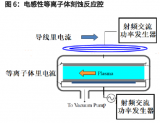

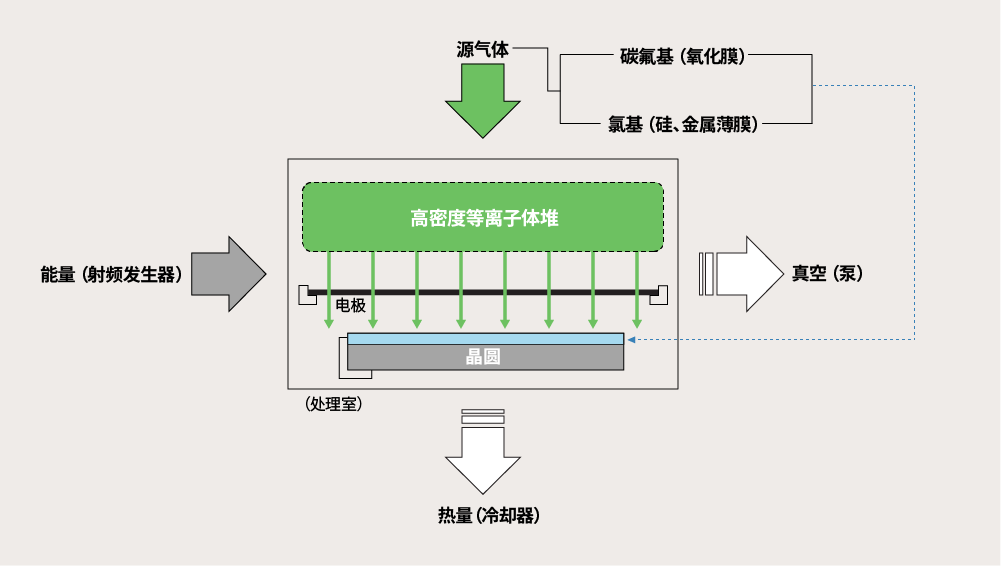

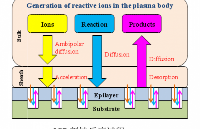

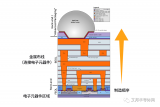

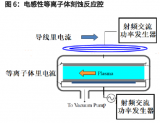

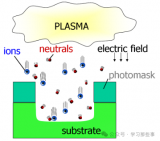

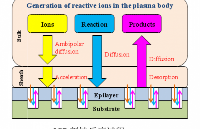

等離子體工藝廣泛應(yīng)用于半導(dǎo)體制造中。比如,IC制造中的所有圖形化刻蝕均為等離子體刻蝕或干法刻蝕,等離子體增強(qiáng)式化學(xué)氣相沉積(PECVD)和高密度等離子體化學(xué)氣相沉積 (HDP CVD)廣泛用于電介質(zhì)

2022-11-15 09:57:31 5641

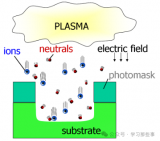

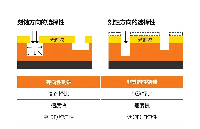

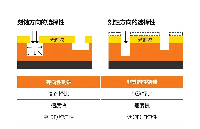

5641 等離子體圖形化刻蝕過(guò)程中,刻蝕圖形將影響刻蝕速率和刻蝕輪廓,稱(chēng)為負(fù)載效應(yīng)。負(fù)載效應(yīng)有兩種:宏觀負(fù)載效應(yīng)和微觀負(fù)載效應(yīng)。

2023-02-08 09:41:26 5131

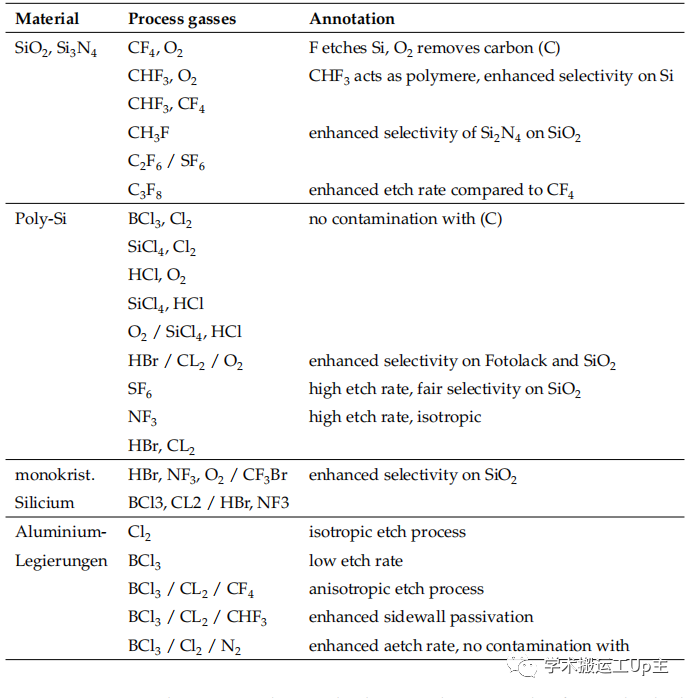

5131 單晶硅刻蝕用來(lái)形成相鄰晶體管間的絕緣區(qū),多晶硅刻蝕用于形成柵極和局部連線(xiàn)。

2023-02-13 11:13:23 12503

12503

在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設(shè)計(jì)好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進(jìn)行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 2105

2105

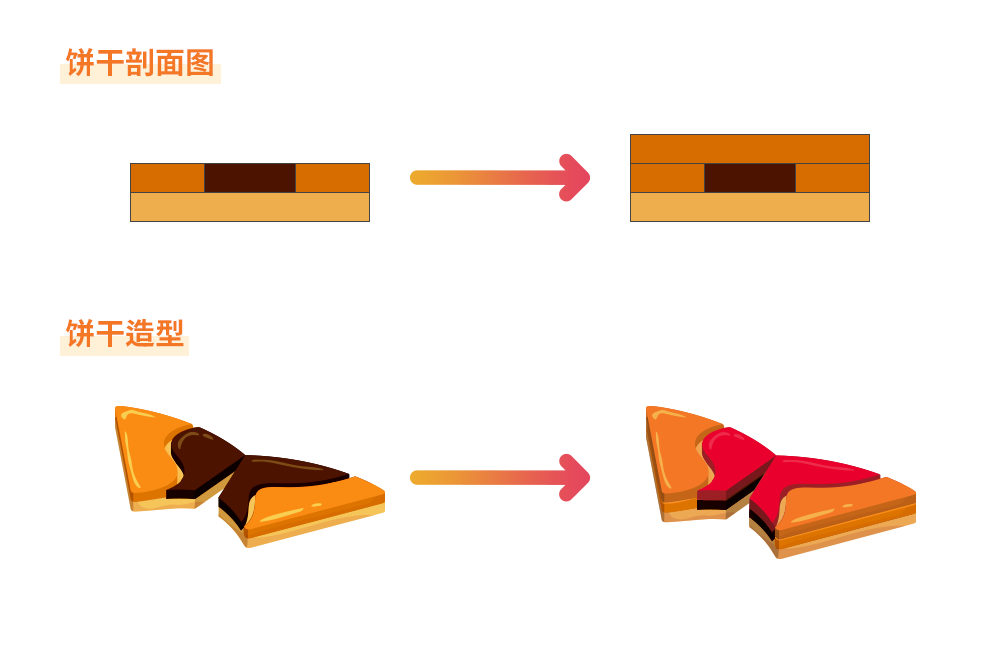

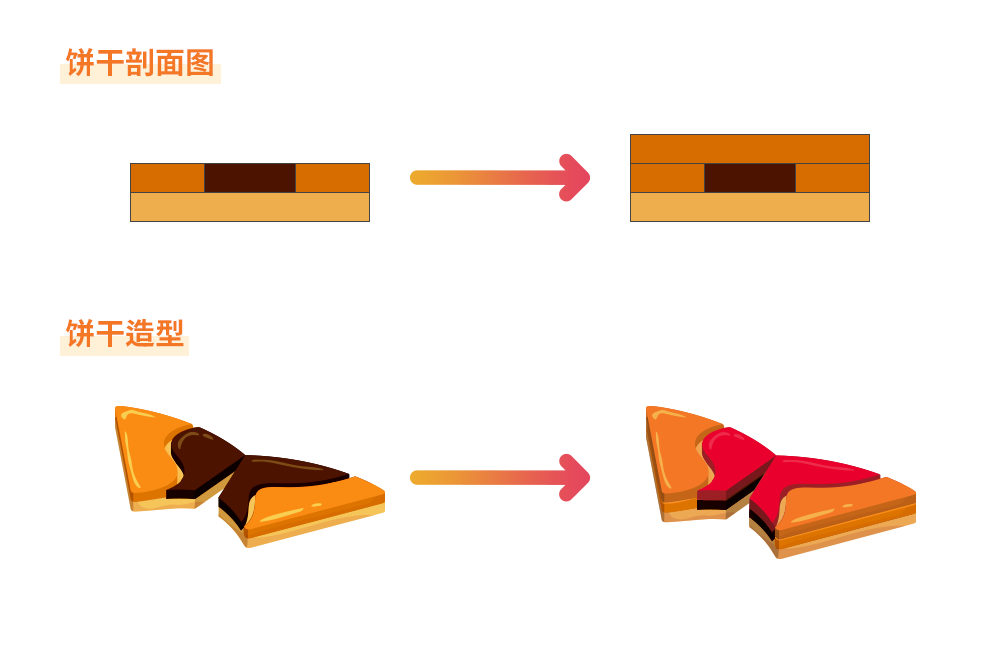

在半導(dǎo)體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來(lái)講講如何采用這個(gè)“餅干模具”印出我們想要的“餅干”。這一步驟的重點(diǎn),在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

2023-08-10 15:06:10 1860

1860 濕法刻蝕由于精度較差,只適用于很粗糙的制程,但它還是有優(yōu)點(diǎn)的,比如價(jià)格便宜,適合批量處理,酸槽里可以一次浸泡25張硅片,所以有些高校和實(shí)驗(yàn)室,還在用濕法做器件,芯片廠(chǎng)里也會(huì)用濕法刻蝕來(lái)顯露表面缺陷(defect),腐蝕背面多晶硅。

2023-08-28 09:47:44 5856

5856

在半導(dǎo)體制程工藝中,有很多不同名稱(chēng)的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說(shuō)“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創(chuàng)建所需的微細(xì)圖案。半導(dǎo)體“刻蝕”工藝所采用的氣體和設(shè)備,在其他類(lèi)似工藝中也很常見(jiàn)。

2023-09-24 17:42:03 4046

4046

但是里面也有幾個(gè)關(guān)鍵的工藝參數(shù)需要控制的。同樣Etch GaAs也可以用ICP干法刻蝕的工藝,比濕法工藝效果要好些,側(cè)壁也垂直很多。

2023-11-14 09:31:29 2561

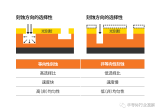

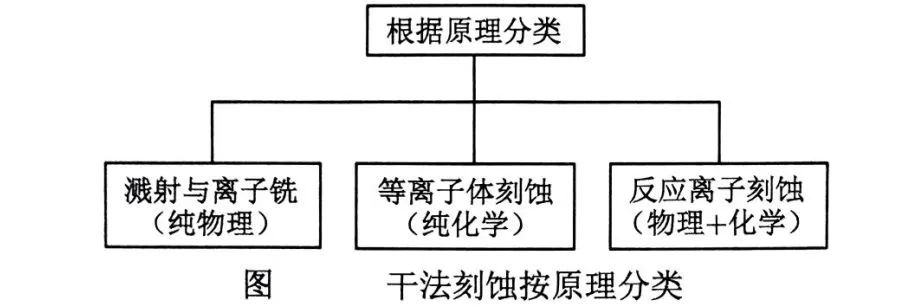

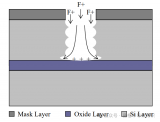

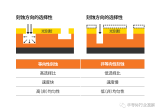

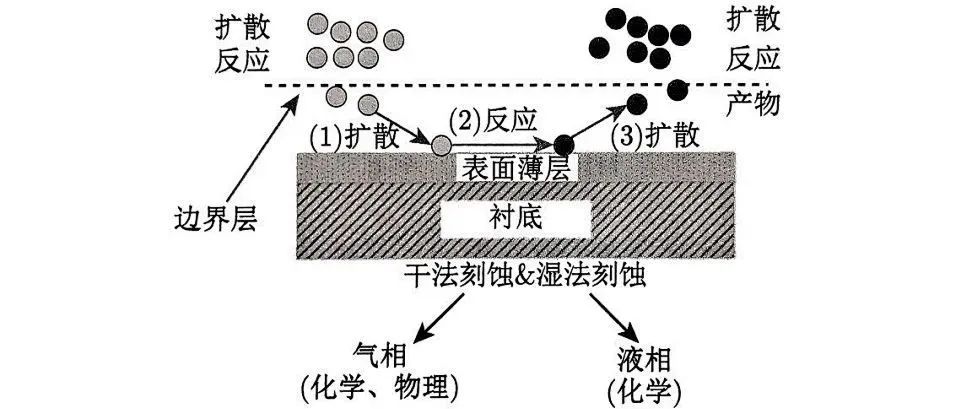

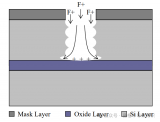

2561 干法刻蝕技術(shù)是一種在大氣或真空條件下進(jìn)行的刻蝕過(guò)程,通常使用氣體中的離子或化學(xué)物質(zhì)來(lái)去除材料表面的部分,通過(guò)掩膜和刻蝕參數(shù)的調(diào)控,可以實(shí)現(xiàn)各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結(jié)構(gòu)

2024-01-20 10:24:56 16124

16124

在半導(dǎo)體加工工藝中,常聽(tīng)到的兩個(gè)詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現(xiàn),有著千絲萬(wàn)縷的聯(lián)系,這一節(jié)介紹半導(dǎo)體刻蝕工藝。

2024-01-26 10:01:58 5925

5925

干法刻蝕技術(shù)作為半導(dǎo)體制造的核心工藝模塊,通過(guò)等離子體與材料表面的相互作用實(shí)現(xiàn)精準(zhǔn)刻蝕,其技術(shù)特性與工藝優(yōu)勢(shì)深刻影響著先進(jìn)制程的演進(jìn)方向。

2025-05-28 17:01:18 3199

3199

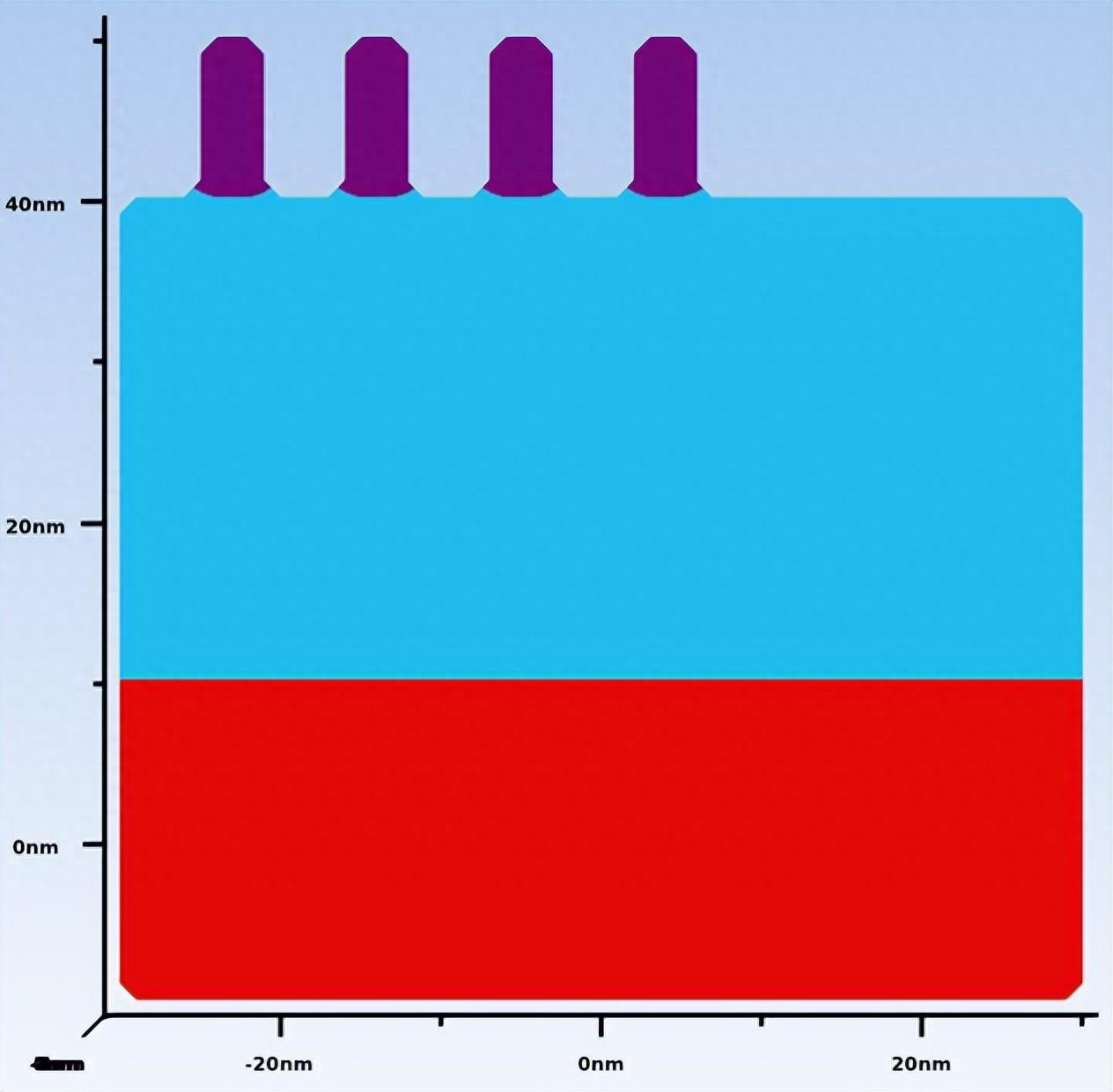

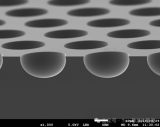

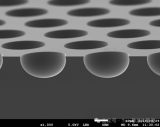

隨著ALD厚度的增加,SiN /基底界面處的孔形狀從方形變?yōu)閳A形,并且逐漸變小。在足夠的ALD厚度下,菱形孔的尖端可視度有限,這會(huì)導(dǎo)致較低的刻蝕速率且刻蝕保持圓形。

2021-11-15 14:34:30 2317

2317

濕法刻蝕作為半導(dǎo)體制造領(lǐng)域的元老級(jí)技術(shù),其發(fā)展歷程與集成電路的微型化進(jìn)程緊密交織。盡管在先進(jìn)制程中因線(xiàn)寬控制瓶頸逐步被干法工藝取代,但憑借獨(dú)特的工藝優(yōu)勢(shì),濕法刻蝕仍在特定場(chǎng)景中占據(jù)不可替代的地位。

2025-05-28 16:42:54 4247

4247

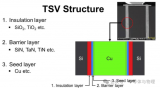

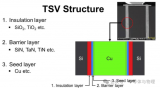

鋁、干法刻蝕鈦、干法刻蝕氮化鈦等)20、 等離子去膠21、 DRIE (硅深槽刻蝕)、ICP、TSV22、 濕法刻蝕23、 膜厚測(cè)量24、 納米、微米臺(tái)階測(cè)量25、 電阻、方阻、電阻率測(cè)量等26、 半導(dǎo)體

2015-01-07 16:15:47

半導(dǎo)體光刻蝕工藝

2021-02-05 09:41:23

30 dBm,增益大于5 dB。關(guān)鍵詞:碳化硅;金屬?半導(dǎo)體場(chǎng)效應(yīng)晶體管;犧牲氧化;干法刻蝕;等平面工藝

2009-10-06 09:48:48

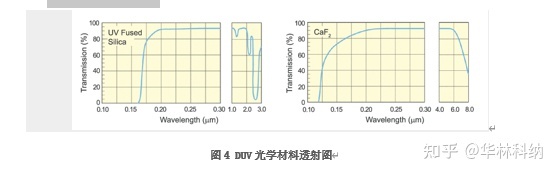

書(shū)籍:《炬豐科技-半導(dǎo)體工藝》文章:GaN 基板的表面處理編號(hào):JFSJ-21-077作者:炬豐科技網(wǎng)址:http://www.wetsemi.com/index.html關(guān)鍵詞: GaN 襯底

2021-07-07 10:26:01

保留半導(dǎo)體電路圖。這一步驟需要借助液體、氣體或等離子體等物質(zhì),通過(guò)濕法刻蝕或干法刻蝕等方法,精確去除選定的多余部分。

薄膜沉積將含有特定分子或原子單元的薄膜材料,通過(guò)一系列技術(shù)手段,如化學(xué)氣相沉積

2024-12-30 18:15:45

新加坡知名半導(dǎo)體晶圓代工廠(chǎng)招聘資深刻蝕工藝工程師和刻蝕設(shè)備主管!此職位為內(nèi)部推薦,深刻蝕工藝工程師需要有LAM 8寸機(jī)臺(tái)poly刻蝕經(jīng)驗(yàn)。刻蝕設(shè)備主管需要熟悉LAM8寸機(jī)臺(tái)。待遇優(yōu)厚。有興趣的朋友可以將簡(jiǎn)歷發(fā)到我的郵箱sternice81@gmail.com,我會(huì)轉(zhuǎn)發(fā)給HR。

2017-04-29 14:23:25

蒸發(fā),所以刻蝕要在一個(gè)裝有冷卻蓋的密封回流容器中進(jìn)行。主要問(wèn)題是光刻膠層經(jīng)不起刻蝕劑的溫度和高刻蝕速率。因此,需要一層二氧化硅或其他材料來(lái)阻擋刻蝕劑。這兩個(gè)因素已導(dǎo)致對(duì)于氮化硅使用干法刻蝕技術(shù)。蒸汽刻蝕

2018-12-21 13:49:20

今日分享晶圓制造過(guò)程中的工藝及運(yùn)用到的半導(dǎo)體設(shè)備。晶圓制造過(guò)程中有幾大重要的步驟:氧化、沉積、光刻、刻蝕、離子注入/擴(kuò)散等。這幾個(gè)主要步驟都需要若干種半導(dǎo)體設(shè)備,滿(mǎn)足不同的需要。設(shè)備中應(yīng)用較為廣泛

2018-10-15 15:11:22

形成電路,而“濕法”刻蝕(使用化學(xué)浴)主要用于清潔晶圓。 干法刻蝕是半導(dǎo)體制造中最常用的工藝之一。 開(kāi)始刻蝕前,晶圓上會(huì)涂上一層光刻膠或硬掩膜(通常是氧化物或氮化物),然后在光刻時(shí)將電路圖形曝光在晶圓

2017-10-09 19:41:52

資料介紹

此文檔是最詳盡最完整介紹半導(dǎo)體前端工藝和后端制程的書(shū)籍,作者是美國(guó)人Michael Quirk。看完相信你對(duì)整個(gè)芯片制造流程會(huì)非常清晰地了解。從硅片制造,到晶圓廠(chǎng)芯片工藝的四大基本類(lèi)

2025-04-15 13:52:11

問(wèn)個(gè)菜的問(wèn)題:半導(dǎo)體(或集成電路)工藝 來(lái)個(gè)人講講 半導(dǎo)體工藝 集成電路工藝 硅工藝 CMOS工藝的概念和區(qū)別以及聯(lián)系吧。查了一下:集成電路工藝(integrated

2009-09-16 11:51:34

、具有半導(dǎo)體器件工藝開(kāi)發(fā)工作經(jīng)歷,3年以上工作經(jīng)驗(yàn),4、具有良好的團(tuán)隊(duì)合作精神和進(jìn)取精神三、半導(dǎo)體刻蝕工藝工程師職責(zé)描述:1、 獨(dú)立負(fù)責(zé)干法、濕法刻蝕工藝,進(jìn)行刻蝕工藝菜單的調(diào)試; 2、優(yōu)化干法刻蝕、濕法

2016-10-26 17:05:04

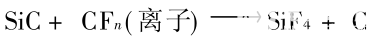

最近需要用到干法刻蝕技術(shù)去刻蝕碳化硅,采用的是ICP系列設(shè)備,刻蝕氣體使用的是SF6+O2,碳化硅上面沒(méi)有做任何掩膜,就是為了去除SiC表面損傷層達(dá)到表面改性的效果。但是實(shí)際刻蝕過(guò)程中總是會(huì)在碳化硅

2022-08-31 16:29:50

本帖最后由 gk320830 于 2015-3-7 11:21 編輯

釋放MEMS機(jī)械結(jié)構(gòu)的干法刻蝕技術(shù)濕法刻蝕是MEMS 器件去除犧牲材料的傳統(tǒng)工藝,總部位于蘇格蘭的Point 35

2013-11-04 11:51:00

摘要 利用Cl2/BCl3/CH4電感應(yīng)耦合等離子體(ICP)干法刻蝕技術(shù),實(shí)現(xiàn)了對(duì)AlGaInAs,InP材料的非選擇性刻蝕。AlGaInAs與InP的刻蝕速率分別為820nm/min與770nm/min,獲得了刻蝕深度為4.9μm,垂直光滑的A

2010-11-30 14:58:45 17

17 釋放MEMS機(jī)械結(jié)構(gòu)的干法刻蝕技術(shù)

濕法刻蝕是MEMS 器件去除犧牲材料的傳統(tǒng)工藝,總部位于蘇格蘭的Point 35 Microstructures在SEMICON C

2009-11-18 09:17:32 1341

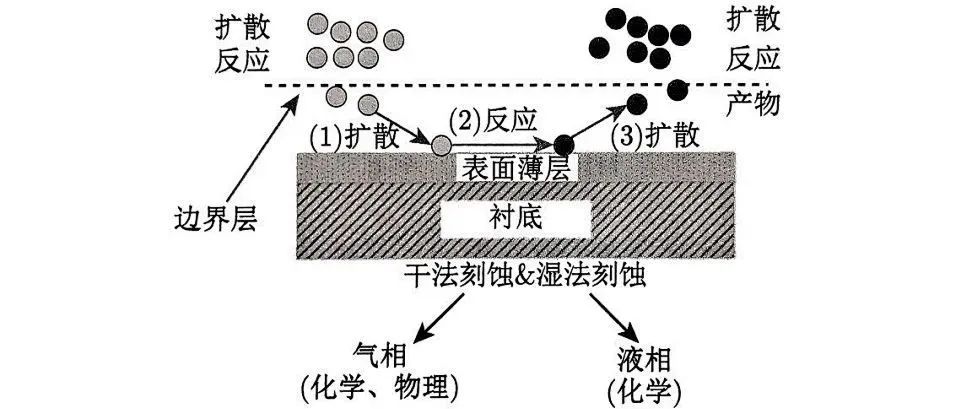

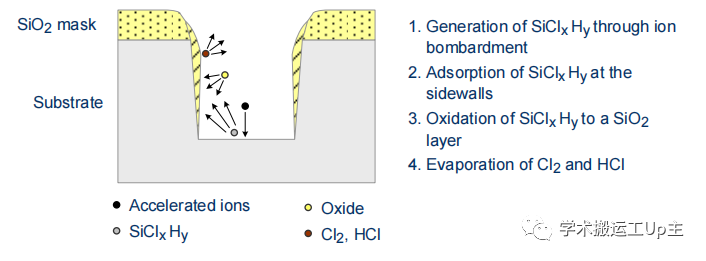

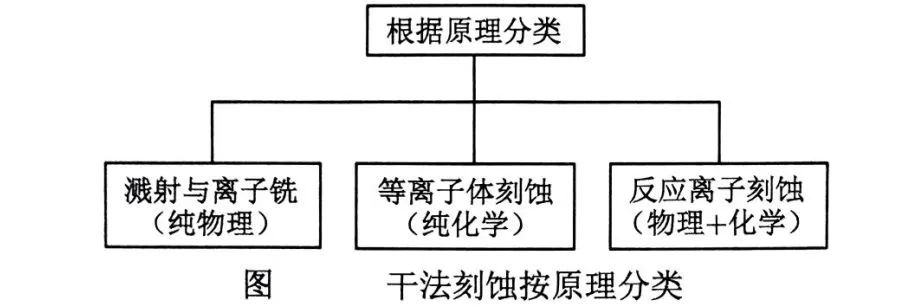

1341 干法刻蝕原理

刻蝕作用:去除邊緣PN結(jié),防止上下短路。干法刻蝕原理:利用高頻輝光放電反應(yīng),使CF4氣體激活成活性粒子,這些活性

2010-07-18 11:28:20 6853

6853 蘋(píng)果設(shè)計(jì)和工程團(tuán)隊(duì)研究出一種新型的鍵盤(pán)刻蝕工藝,利用不同的激光來(lái)制作蘋(píng)果背光鍵盤(pán).

2011-12-16 09:43:20 1075

1075

本文實(shí)現(xiàn)了一種正面開(kāi)口的熱電堆結(jié)構(gòu),采用XeF2作為工作氣體干法刻蝕工藝釋放器件。相對(duì)于刻蝕硅,XeF2氣體對(duì)鋁等材料的刻蝕速率極小,這樣就可以采用標(biāo)準(zhǔn)CMOS工藝中最常用的材料

2012-05-02 17:26:13 4402

4402

晶體硅太陽(yáng)能電池生產(chǎn)線(xiàn)刻蝕工序培訓(xùn) 1、刻蝕的作用及方法;2、刻蝕的工藝設(shè)備、操作流程及常用化學(xué)品;3、主要檢測(cè)項(xiàng)目及標(biāo)準(zhǔn);4、常見(jiàn)問(wèn)題及解決方法;5、未來(lái)工藝的發(fā)展方向;

2017-09-29 10:29:09 25

25 反刻是在想要把某一層膜的總的厚度減小時(shí)采用的(如當(dāng)平坦化硅片表面時(shí)需要減小形貌特征)。光刻膠是另一個(gè)剝離的例子。總的來(lái)說(shuō),有圖形刻蝕和無(wú)圖形刻蝕工藝條件能夠采用干法刻蝕或濕法腐蝕技術(shù)來(lái)實(shí)現(xiàn)。為了復(fù)制硅片表面材料上的掩膜圖形,刻蝕必須滿(mǎn)足一些特殊的要求。

2018-12-14 16:05:27 72478

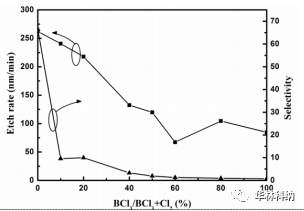

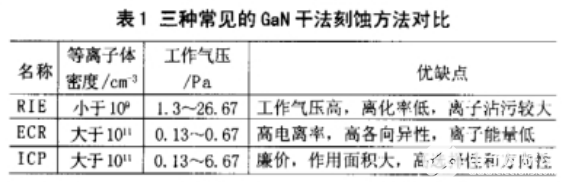

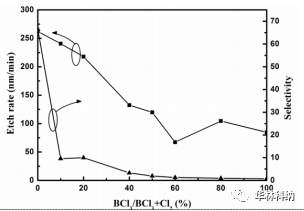

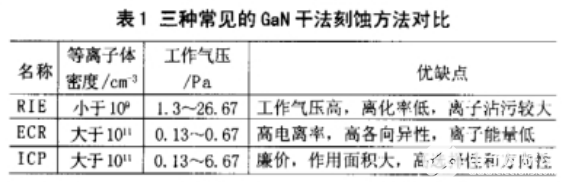

72478 摘要:對(duì)比了RIE,ECR,ICP等幾種GaN7干法刻蝕方法的特點(diǎn)。回顧了GaN1法刻蝕領(lǐng)域的研究進(jìn)展。以ICP刻蝕GaN和AIGaN材料為例,通過(guò)工藝參數(shù)的優(yōu)化,得到了高刻蝕速率和理想的選擇比及

2020-12-29 14:39:29 4598

4598

在集成電路的制造過(guò)程中,刻蝕就是利用化學(xué)或物理方法有選擇性地從硅片表面去除不需要的材料的過(guò)程。從工藝上區(qū)分,刻蝕可以分為濕法刻蝕和干法刻蝕。前者的主要特點(diǎn)是各向同性刻蝕;后者是利用等離子體來(lái)進(jìn)行

2020-12-29 14:42:58 11752

11752

摘要:簡(jiǎn)述了在SiC材料半導(dǎo)體器件制造工藝中,對(duì)SiC材料采用干法刻蝕工藝的必要性.總結(jié)了近年來(lái)SiC干法刻蝕技術(shù)的工藝發(fā)展?fàn)顩r. 半導(dǎo)體器件已廣泛應(yīng)用于各種場(chǎng)合,近年來(lái)其應(yīng)用領(lǐng)域已拓展至許多

2020-12-30 10:30:11 10663

10663

刻蝕速率是指在刻蝕過(guò)程中去除硅片表面材料的速度通常用?/min表示, 刻蝕窗口的深度稱(chēng)為臺(tái)階高度。 為了高的產(chǎn)量, 希望有高的刻蝕速率。 在采用單片工藝的設(shè)備中, 這是一個(gè)很重要的參數(shù)。 刻蝕速率由工藝和設(shè)備變量決定, 如被刻蝕材料類(lèi)型、 蝕機(jī)的結(jié)構(gòu)配置、 使用的刻蝕氣體和工藝參數(shù)設(shè)置。

2022-03-15 13:41:59 4092

4092

刻蝕室半導(dǎo)體IC制造中的至關(guān)重要的一道工藝,一般有干法刻蝕和濕法刻蝕兩種,干法刻蝕和濕法刻蝕一個(gè)顯著的區(qū)別是各向異性,更適合用于對(duì)形貌要求較高的工藝步驟。

2022-06-13 14:43:31 6

6 在 MEMS 制造工藝中,常用的干法刻蝕包括反應(yīng)離子刻蝕 (Reactive lon Etching, RIE)、深反應(yīng)離子刻蝕(Deep Reactive lon Etching, DRIE) 和XerF2各向同性蝕刻。

2022-10-10 10:12:15 6878

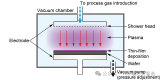

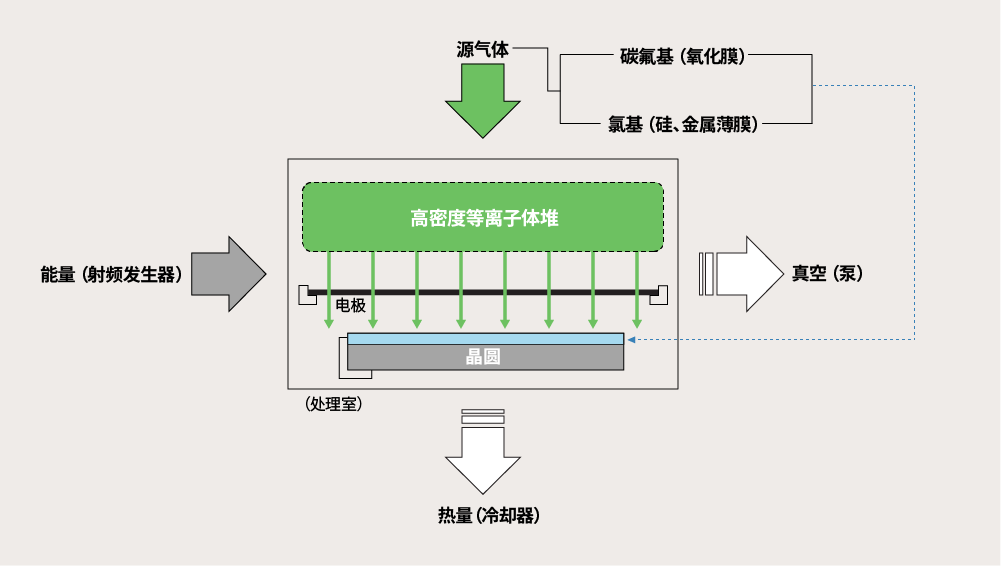

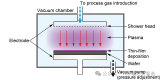

6878 干法刻蝕工藝流程為,將刻蝕氣體注入真空反應(yīng)室,待壓力穩(wěn)定后,利用射頻輝光放電產(chǎn)生等離子體;受高速電子撞擊后分解產(chǎn)生自由基,并擴(kuò)散到圓片表面被吸附。

2022-11-10 09:54:19 9999

9999 濕法刻蝕是集成電路制造工藝最早采用的技術(shù)之一。雖然由于受其刻蝕的各向同性的限制,使得大部分的濕法刻蝕工藝被具有各向異性的干法刻蝕替代,但是它在尺寸較大的非關(guān)鍵層清洗中依然發(fā)揮著重要的作用。

2022-11-11 09:34:18 19992

19992 刻蝕是移除晶圓表面材料,達(dá)到IC設(shè)計(jì)要求的一種工藝過(guò)程。刻蝕有兩種:一種為圖形 化刻蝕,這種刻蝕能將指定區(qū)域的材料去除,如將光刻膠或光刻版上的圖形轉(zhuǎn)移到襯底薄膜 上

2023-02-01 09:09:35 4217

4217 功率半導(dǎo)體分立器件的主要工藝流程包括:在硅圓片上加工芯片(主要流程為薄膜制造、曝光和刻蝕),進(jìn)行芯片封裝,對(duì)加工完畢的芯片進(jìn)行技術(shù)性能指標(biāo)測(cè)試,其中主要生產(chǎn)工藝有外延工藝、光刻工藝、刻蝕工藝、離子注入工藝和擴(kuò)散工藝等。

2023-02-24 15:34:13 6139

6139 嚴(yán)重的離子轟擊將產(chǎn)生大量的熱量,所以如果沒(méi)有適當(dāng)?shù)睦鋮s系統(tǒng),晶圓溫度就會(huì)提高。對(duì)于圖形化刻蝕,晶圓上涂有一層光刻膠薄膜作為圖形屏蔽層,如果晶圓溫度超過(guò)150攝氏度,屏蔽層就會(huì)被燒焦,而且化學(xué)刻蝕速率

2023-03-06 13:52:33 2304

2304 對(duì)于濕法刻蝕,大部分刻蝕的終點(diǎn)都取決于時(shí)間,而時(shí)間又取決于預(yù)先設(shè)定的刻蝕速率和所需的刻蝕厚度。由于缺少自動(dòng)監(jiān)測(cè)終點(diǎn)的方法,所以通常由操作員目測(cè)終點(diǎn)。濕法刻蝕速率很容易受刻蝕劑溫度與濃度的影響,這種影響對(duì)不同工作站和不同批量均有差異,因此單獨(dú)用時(shí)間決定刻蝕終點(diǎn)很困難,一般釆用操作員目測(cè)的方式。

2023-03-06 13:56:03 3705

3705 FinFET三維器件也可以用體硅襯底制作,這需要更好地控制單晶硅刻蝕工藝,如CD、深度和輪廓。

2023-03-30 09:39:18 5704

5704 DRAM柵工藝中,在多晶硅上使用鈣金屬硅化物以減少局部連線(xiàn)的電阻。這種金屬硅化物和多晶硅的堆疊薄膜刻蝕需要增加一道工藝刻蝕W或WSi2,一般先使用氟元素刻蝕鈞金屬硅化合物層,然后再使用氯元素刻蝕多晶硅。

2023-04-07 09:48:16 5091

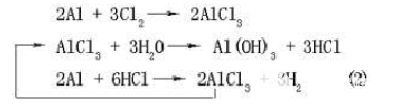

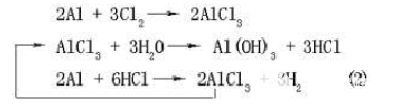

5091 金屬刻蝕具有良好的輪廓控制、殘余物控制,防止金屬腐蝕很重要。金屬刻蝕時(shí)鋁中如果 有少量銅就會(huì)引起殘余物問(wèn)題,因?yàn)镃u Cl2的揮發(fā)性極低且會(huì)停留在晶圓表面。

2023-04-10 09:40:54 6518

6518 壓力主要控制刻蝕均勻性和刻蝕輪廓,同時(shí)也能影響刻蝕速率和選擇性。改變壓力會(huì)改變電子和離子的平均自由程(MFP),進(jìn)而影響等離子體和刻蝕速率的均勻性。

2023-04-17 10:36:43 4532

4532 本篇要講的金屬布線(xiàn)工藝,與前面提到的光刻、刻蝕、沉積等獨(dú)立的工藝不同。在半導(dǎo)體制程中,光刻、刻蝕等工藝,其實(shí)是為了金屬布線(xiàn)才進(jìn)行的。在金屬布線(xiàn)過(guò)程中,會(huì)采用很多與之前的電子元器件層性質(zhì)不同的配線(xiàn)材料(金屬)。

2023-04-25 10:38:49 2938

2938

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。

2023-04-28 11:24:27 3881

3881

集成電路前道工藝及對(duì)應(yīng)設(shè)備主要分八大類(lèi),包括光刻(光刻機(jī))、刻蝕(刻蝕機(jī))、薄膜生長(zhǎng)(PVD-物理氣相沉積、CVD-化學(xué)氣相沉積等薄膜設(shè)備)、擴(kuò)散(擴(kuò)散爐)、離子注入(離子注入機(jī))、平坦化(CMP設(shè)備)、金屬化(ECD設(shè)備)、濕法工藝(濕法工藝設(shè)備)等。

2023-05-30 10:47:12 3372

3372

在半導(dǎo)體制程工藝中,有很多不同名稱(chēng)的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說(shuō)“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創(chuàng)建所需的微細(xì)圖案。半導(dǎo)體“刻蝕”工藝所采用的氣體和設(shè)備,在其他類(lèi)似工藝中也很常見(jiàn)。

2023-06-15 17:51:57 3242

3242

刻蝕在晶圓上完成電路圖的光刻后,就要用刻蝕工藝來(lái)去除任何多余的氧化膜且只留下半導(dǎo)體電路圖。要做到這一點(diǎn)需要利用液體、氣體或等離子體來(lái)去除選定的多余部分。刻蝕的方法主要分為兩種,取決于所使用的物質(zhì)

2022-07-12 15:49:25 3315

3315

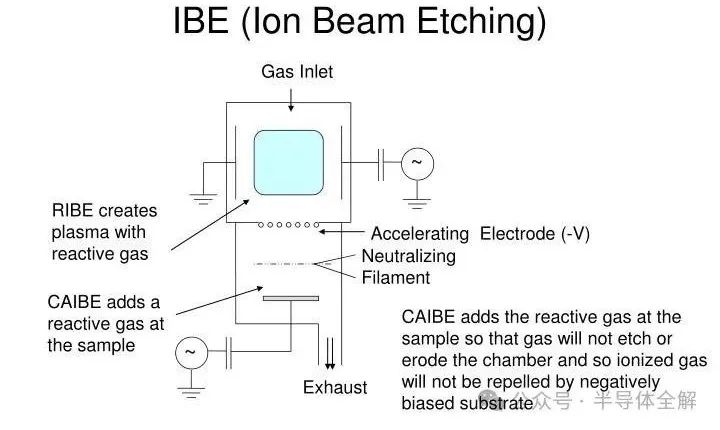

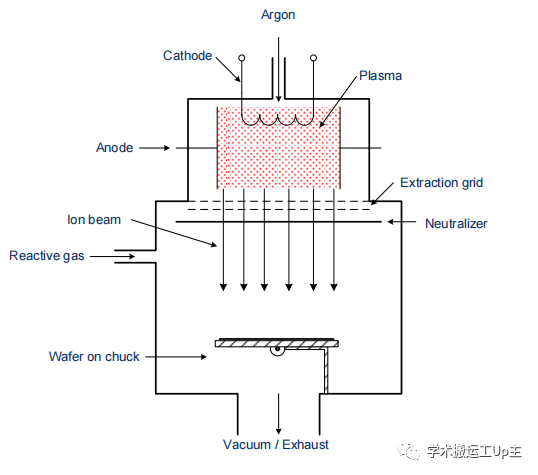

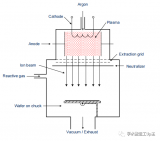

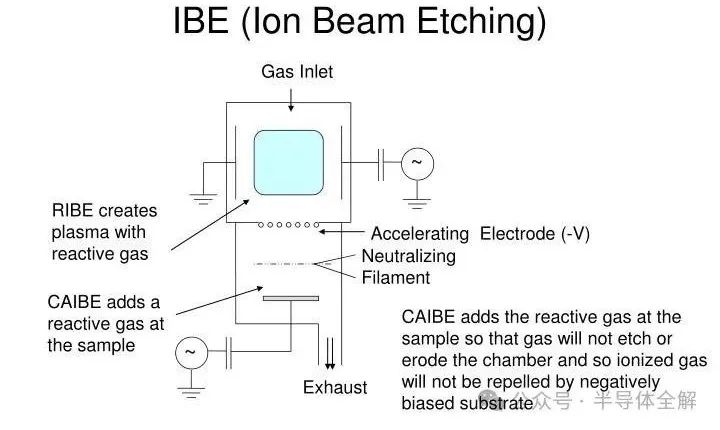

離子束蝕刻 (Ion beam etch) 是一種物理干法蝕刻工藝。由此,氬離子以約1至3keV的離子束輻射到表面上。由于離子的能量,它們會(huì)撞擊表面的材料。晶圓垂直或傾斜入離子束,蝕刻過(guò)程是絕對(duì)

2023-06-20 09:48:56 9250

9250

Dimension, CD)小型化(2D視角),刻蝕工藝從濕法刻蝕轉(zhuǎn)為干法刻蝕,因此所需的設(shè)備和工藝更加復(fù)雜。由于積極采用3D單元堆疊方法,刻蝕工藝的核心性能指數(shù)出現(xiàn)波動(dòng),從而刻蝕工藝與光刻工藝成為半導(dǎo)體制造的重要工藝流程之一。

2023-06-26 09:20:10 3193

3193

在前幾篇文章(點(diǎn)擊查看),我們一直在借用餅干烘焙過(guò)程來(lái)形象地說(shuō)明半導(dǎo)體制程 。在上一篇我們說(shuō)到,為制作巧克力夾心,需通過(guò)“刻蝕工藝”挖出餅干的中間部分,然后倒入巧克力糖漿,再蓋上一層餅干層。“倒入巧克力糖漿”和“蓋上餅干層”的過(guò)程在半導(dǎo)體制程中就相當(dāng)于“沉積工藝”。

2023-06-29 16:56:17 2560

2560

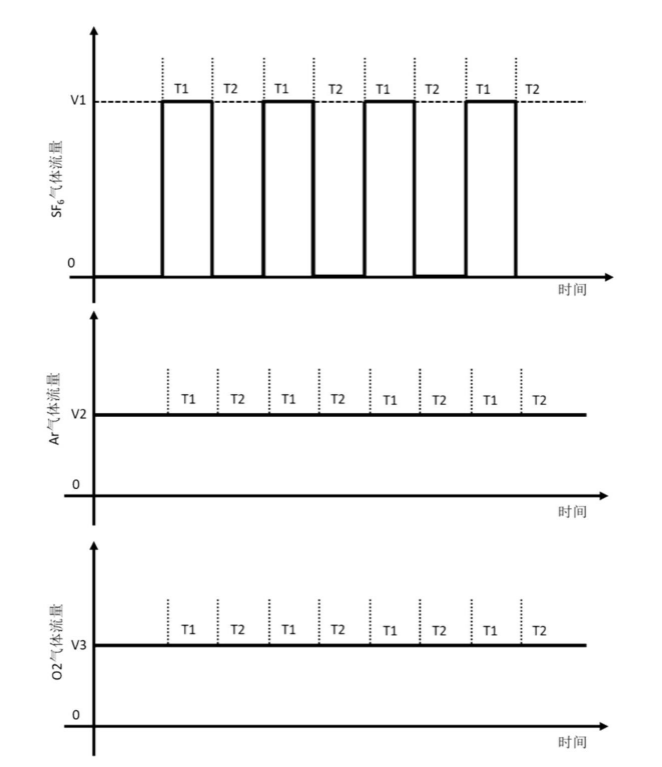

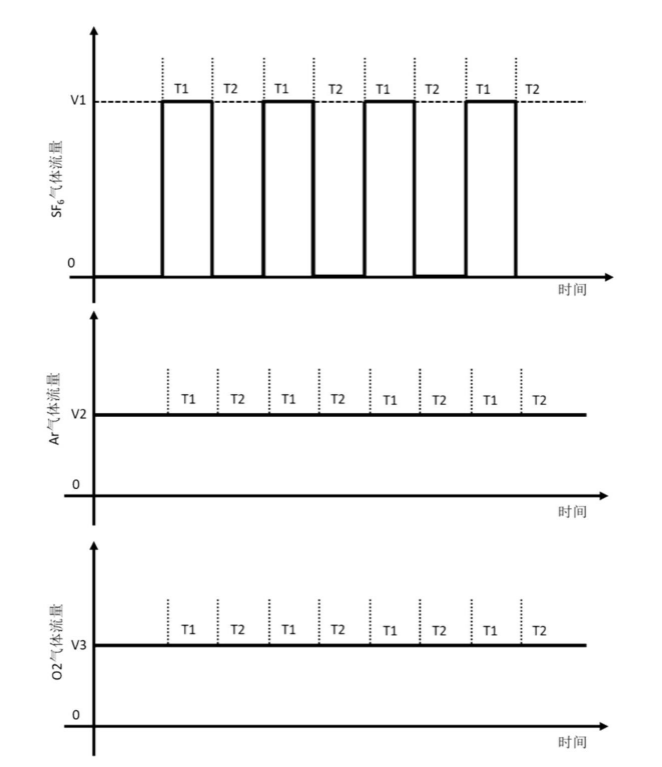

第一種是間歇式刻蝕方法(BOSCH),即多次交替循環(huán)刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 9786

9786

9月17日,北方華創(chuàng)在投資者互動(dòng)平臺(tái)表示,公司前期已經(jīng)發(fā)布了首臺(tái)國(guó)產(chǎn)12英寸CCP晶邊干法刻蝕設(shè)備研發(fā)成功有關(guān)信息,目前已在客戶(hù)端實(shí)現(xiàn)量產(chǎn),其優(yōu)秀的工藝均勻性、穩(wěn)定性贏得客戶(hù)高度評(píng)價(jià)。

2023-09-20 10:09:49 2728

2728 在半導(dǎo)體制造中,刻蝕工序是必不可少的環(huán)節(jié)。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術(shù)各有優(yōu)勢(shì),也各有一定的局限性,理解它們之間的差異是至關(guān)重要的。

2023-09-26 18:21:00 10327

10327

據(jù)工信部網(wǎng)站11月16日消息,工信部公開(kāi)征集了《半導(dǎo)體設(shè)備 集成電路制造用干法刻蝕設(shè)備測(cè)試方法》等196個(gè)行業(yè)標(biāo)準(zhǔn)、1個(gè)行業(yè)標(biāo)準(zhǔn)外文版、38個(gè)推薦性國(guó)家標(biāo)準(zhǔn)計(jì)劃項(xiàng)目的意見(jiàn)。

2023-11-16 17:04:49 1972

1972

半導(dǎo)體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創(chuàng)建所需圖形

2023-11-27 16:54:26 1646

1646

W刻蝕工藝中使用SF6作為主刻步氣體,并通過(guò)加入N2以增加對(duì)光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負(fù)載效應(yīng),避免產(chǎn)生凹坑,并使用對(duì)TiN有高選擇比的化學(xué)氣體進(jìn)行刻蝕。

2023-12-06 09:38:53 12484

12484 該專(zhuān)利詳細(xì)闡述了一種針對(duì)含硅有機(jī)介電層的高效刻蝕方法及相應(yīng)的半導(dǎo)體工藝設(shè)備。它主要涉及到通過(guò)交替運(yùn)用至少兩個(gè)刻蝕步驟來(lái)刻蝕含硅有機(jī)介電層。這兩個(gè)步驟分別為第一刻蝕步驟和第二刻蝕步驟。

2023-12-06 11:58:16 1906

1906

使用SEMulator3D?工藝步驟進(jìn)行刻蝕終點(diǎn)探測(cè) 作者:泛林集團(tuán) Semiverse Solutions 部門(mén)軟件應(yīng)用工程師 Pradeep Nanja 介紹 半導(dǎo)體行業(yè)一直專(zhuān)注于使用先進(jìn)的刻蝕

2024-01-19 16:02:42 1233

1233

刻蝕可以分為濕法刻蝕和干法刻蝕。濕法刻蝕各向異性較差,側(cè)壁容易產(chǎn)生橫向刻蝕造成刻蝕偏差,通常用于工藝尺寸較大的應(yīng)用,或用于干法刻蝕后清洗殘留物等。

2024-04-12 11:41:56 8872

8872

今天我們要一起揭開(kāi)一個(gè)隱藏在現(xiàn)代電子設(shè)備背后的高科技秘密——干法刻蝕工藝。這不僅是一場(chǎng)對(duì)微觀世界的深入探秘,更是一次對(duì)半導(dǎo)體芯片制造藝術(shù)的奇妙之旅。

2024-08-26 10:13:57 4403

4403

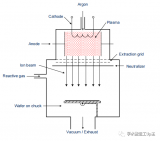

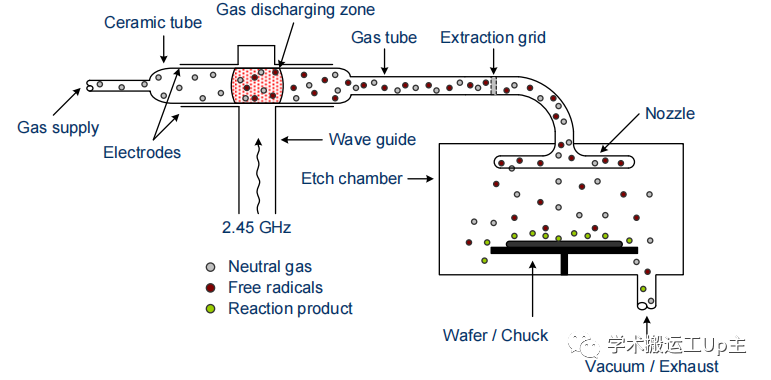

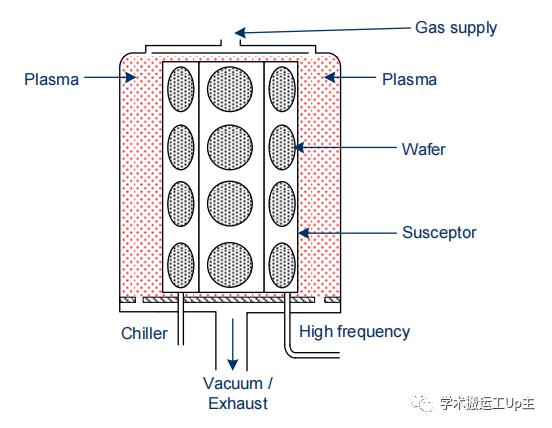

主要介紹幾種常用于工業(yè)制備的刻蝕技術(shù),其中包括離子束刻蝕(IBE)、反應(yīng)離子刻蝕(RIE)、以及后來(lái)基于高密度等離子體反應(yīng)離子的電子回旋共振等離子體刻蝕(ECR)和電感耦合等離子體刻蝕(ICP)。

2024-10-18 15:20:41 3338

3338

Bosch刻蝕工藝作為微納加工領(lǐng)域的關(guān)鍵技術(shù),對(duì)于HBM和TSV的制造起到了至關(guān)重要的作用。

2024-10-31 09:43:12 4272

4272

干法刻蝕去除表面的 ONO,最終多晶硅柵側(cè)面保留一部分二氧化硅。側(cè)墻工藝不需要掩膜版,它僅僅是利用各向異性干法刻蝕的回刻形成的。

2024-11-09 10:02:24 2306

2306

在本篇文章中,我們主要介紹刻蝕工藝評(píng)價(jià)的工藝參數(shù)以及如何做好刻蝕工藝。

一、刻蝕工藝質(zhì)量評(píng)價(jià) 1)刻蝕速率 刻蝕速率是指在蝕刻過(guò)程中被去除的材料的速率,通常以單位時(shí)間內(nèi)的厚度減少量來(lái)

2024-11-15 10:15:31 3878

3878

本文介紹了為什么干法刻蝕又叫低溫等離子體刻蝕。 什么是低溫等離子體刻蝕,除了低溫難道還有高溫嗎?等離子體的溫度?? ? 等離子體是物質(zhì)的第四態(tài),并不是只有半導(dǎo)體制造或工業(yè)領(lǐng)域中才會(huì)有等離子體

2024-11-16 12:53:53 1560

1560

? ? ? 本文介紹了干法刻蝕工藝的不同參數(shù)。 干法刻蝕中可以調(diào)節(jié)的工藝參數(shù)有哪些?各有什么作用? 1,溫度:晶圓表面溫度,溫度梯度 晶圓表面溫度:控制刻蝕表面的化學(xué)反應(yīng)速率和產(chǎn)物的揮發(fā)性 溫度梯度

2024-12-02 09:56:43 2897

2897 本文介紹晶圓表面溫度對(duì)干法刻蝕的影響 表面溫度對(duì)干法刻蝕的影響主要包括:聚合物沉積,選擇性,光刻膠流動(dòng)、產(chǎn)物揮發(fā)性與刻蝕速率,表面形貌等。 ? 聚合物沉積?:工藝過(guò)程中產(chǎn)生的聚合物會(huì)在表面沉積

2024-12-03 10:48:31 1982

1982

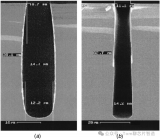

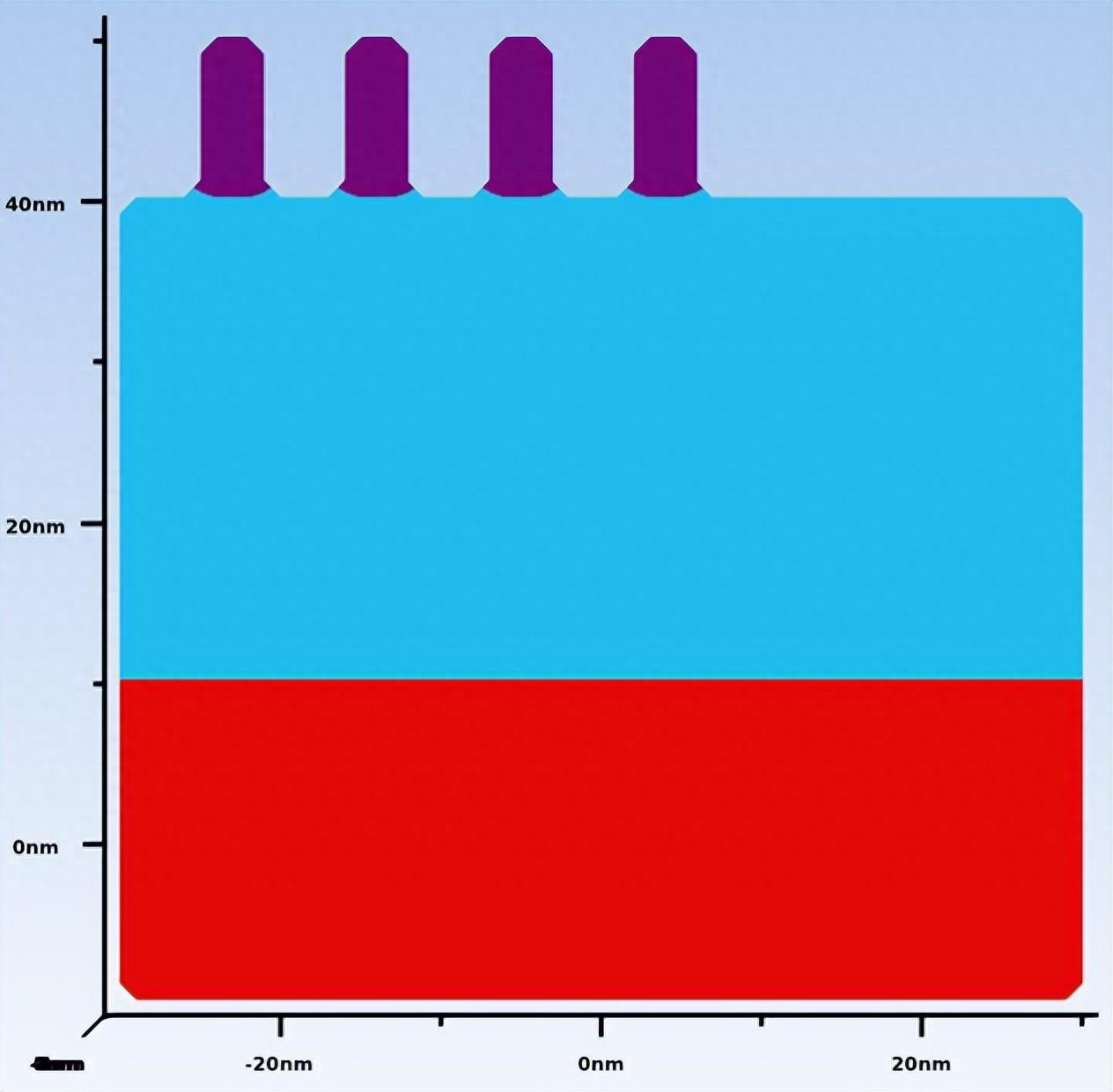

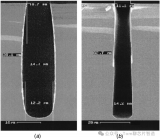

本文介紹了干法刻蝕側(cè)壁彎曲的原因及解決方法。 什么是側(cè)壁彎曲? 如上圖,是典型的干法刻蝕時(shí),側(cè)壁彎曲的樣子,側(cè)壁為凹形或凸形結(jié)構(gòu)。而正常的側(cè)壁幾乎是垂直的,角度接近 90°。 ?什么原因?qū)е铝藗?cè)壁

2024-12-03 11:00:01 1609

1609

本文介紹了刻蝕工藝參數(shù)有哪些。 刻蝕是芯片制造中一個(gè)至關(guān)重要的步驟,用于在硅片上形成微小的電路結(jié)構(gòu)。它通過(guò)化學(xué)或物理方法去除材料層,以達(dá)到特定的設(shè)計(jì)要求。本文將介紹幾種關(guān)鍵的刻蝕參數(shù),包括不完全刻蝕

2024-12-05 16:03:10 2840

2840

本文簡(jiǎn)單介紹了芯片制造過(guò)程中的兩種刻蝕方法 ? 刻蝕(Etch)是芯片制造過(guò)程中相當(dāng)重要的步驟。 刻蝕主要分為干刻蝕和濕法刻蝕。 ①干法刻蝕 利用等離子體將不要的材料去除。 ②濕法刻蝕 利用腐蝕性

2024-12-06 11:13:58 3353

3353

在芯片制造過(guò)程中的各工藝站點(diǎn),有很多不同的工藝名稱(chēng)用于除去晶圓上多余材料,如“清洗”、“刻蝕”、“研磨”等。如果說(shuō)“清洗”工藝是把晶圓上多余的臟污、particle、上一站點(diǎn)殘留物去除掉,“刻蝕

2024-12-16 15:03:06 2431

2431

離子轟擊的不均勻性 干法刻蝕通常是物理作用和化學(xué)作用相結(jié)合的過(guò)程,其中離子轟擊是重要的物理刻蝕手段。在刻蝕過(guò)程中,離子的入射角和能量分布可能不均勻. 如果離子入射角在側(cè)壁的不同位置存在差異,那么

2024-12-17 11:13:12 1469

1469

什么是刻蝕?刻蝕是指通過(guò)物理或化學(xué)方法對(duì)材料進(jìn)行選擇性的去除,從而實(shí)現(xiàn)設(shè)計(jì)的結(jié)構(gòu)圖形的一種技術(shù)。蝕刻是半導(dǎo)體制造及微納加工工藝中相當(dāng)重要的步驟,自1948年發(fā)明晶體管到現(xiàn)在,在微電子學(xué)和半導(dǎo)體領(lǐng)域

2024-12-20 16:03:16 1651

1651

半導(dǎo)體濕法刻蝕殘留物的原理涉及化學(xué)反應(yīng)、表面反應(yīng)、側(cè)壁保護(hù)等多個(gè)方面。 以下是對(duì)半導(dǎo)體濕法刻蝕殘留物原理的詳細(xì)闡述: 化學(xué)反應(yīng) 刻蝕劑與材料的化學(xué)反應(yīng):在濕法刻蝕過(guò)程中,刻蝕劑(如酸、堿或氧化劑

2025-01-02 13:49:32 1181

1181 碳化硅(SiC)作為一種高性能材料,在大功率器件、高溫器件和發(fā)光二極管等領(lǐng)域有著廣泛的應(yīng)用。其中,基于等離子體的干法蝕刻在SiC的圖案化及電子器件制造中起到了關(guān)鍵作用,本文將介紹干法刻蝕的概念、碳硅

2025-01-22 10:59:23 2668

2668

刻蝕工藝的核心機(jī)理與重要性 刻蝕工藝是半導(dǎo)體圖案化過(guò)程中的關(guān)鍵環(huán)節(jié),與光刻機(jī)和薄膜沉積設(shè)備并稱(chēng)為半導(dǎo)體制造的三大核心設(shè)備。刻蝕的主要作用是將光刻膠上的圖形轉(zhuǎn)移到功能膜層,具體而言,是通過(guò)物理及化學(xué)

2025-04-27 10:42:45 2203

2203

半導(dǎo)體BOE(Buffered Oxide Etchant,緩沖氧化物蝕刻液)刻蝕技術(shù)是半導(dǎo)體制造中用于去除晶圓表面氧化層的關(guān)鍵工藝,尤其在微結(jié)構(gòu)加工、硅基發(fā)光器件制作及氮化硅/二氧化硅刻蝕中廣

2025-04-28 17:17:25 5516

5516 ICP(Inductively Coupled Plasma,電感耦合等離子體)刻蝕技術(shù)是半導(dǎo)體制造中的一種關(guān)鍵干法刻蝕工藝,廣泛應(yīng)用于先進(jìn)集成電路、MEMS器件和光電子器件的加工。以下是關(guān)于ICP

2025-05-06 10:33:06 3902

3902 在MEMS制造工藝中,干法刻蝕是通過(guò)等離子體、離子束等氣態(tài)物質(zhì)對(duì)薄膜材料或襯底進(jìn)行刻蝕的工藝,其評(píng)價(jià)參數(shù)直接影響器件的結(jié)構(gòu)精度和性能。那么干法刻蝕有哪些評(píng)價(jià)參數(shù)呢?

2025-07-07 11:21:57 1625

1625

在MEMS中,玻璃因具有良好的絕緣性、透光性、化學(xué)穩(wěn)定性及可鍵合性(如與硅陽(yáng)極鍵合),常被用作襯底、封裝結(jié)構(gòu)或微流體通道基板。玻璃刻蝕是制備這些微結(jié)構(gòu)的核心工藝,需根據(jù)精度要求、結(jié)構(gòu)尺寸及玻璃類(lèi)型選擇合適的方法,玻璃刻蝕主要分為濕法腐蝕和干法刻蝕兩大類(lèi)。

2025-07-18 15:18:01 1491

1491 在半導(dǎo)體制造中,溝槽刻蝕工藝的臺(tái)階高度直接影響器件性能。臺(tái)階儀作為接觸式表面形貌測(cè)量核心設(shè)備,通過(guò)精準(zhǔn)監(jiān)測(cè)溝槽刻蝕形成的臺(tái)階參數(shù)(如臺(tái)階高度、表面粗糙度),為工藝優(yōu)化提供數(shù)據(jù)支撐。Flexfilm費(fèi)

2025-08-01 18:02:17 845

845

濕法刻蝕SC2工藝在半導(dǎo)體制造及相關(guān)領(lǐng)域中具有廣泛的應(yīng)用,以下是其主要應(yīng)用場(chǎng)景和優(yōu)勢(shì):材料選擇性去除與表面平整化功能描述:通過(guò)精確控制化學(xué)溶液的組成,能夠?qū)崿F(xiàn)對(duì)特定材料的選擇性去除。例如,它能

2025-08-06 11:19:18 1198

1198

濕法刻蝕的工藝指標(biāo)是確保半導(dǎo)體制造過(guò)程中圖形轉(zhuǎn)移精度和器件性能的關(guān)鍵參數(shù),主要包括以下幾個(gè)方面:刻蝕速率定義與意義:指單位時(shí)間內(nèi)材料被去除的厚度(如μm/min或nm/s),直接影響生產(chǎn)效率和成本

2025-09-02 11:49:32 765

765

刻蝕是半導(dǎo)體制造中最常用的工藝之一, 上海伯東日本 Atonarp Aston 質(zhì)譜儀適用于等離子體刻蝕過(guò)程及終點(diǎn)監(jiān)測(cè) (干法刻蝕終點(diǎn)檢測(cè)), 通過(guò)持續(xù)監(jiān)控腔室工藝化學(xué)氣體, 確保半導(dǎo)體晶圓生產(chǎn)

2024-10-18 13:33:02

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論