01光“堆疊”可不行

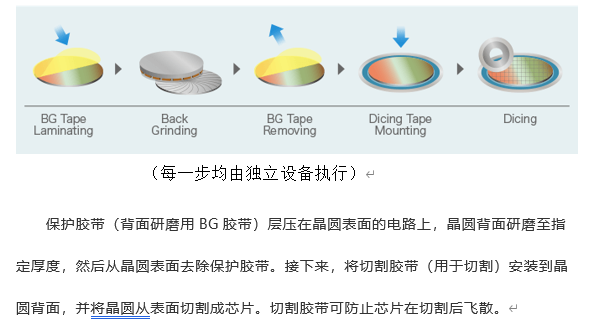

在半導(dǎo)體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來講講如何采用這個(gè)“餅干模具”印出我們想要的“餅干”。這一步驟的重點(diǎn),在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

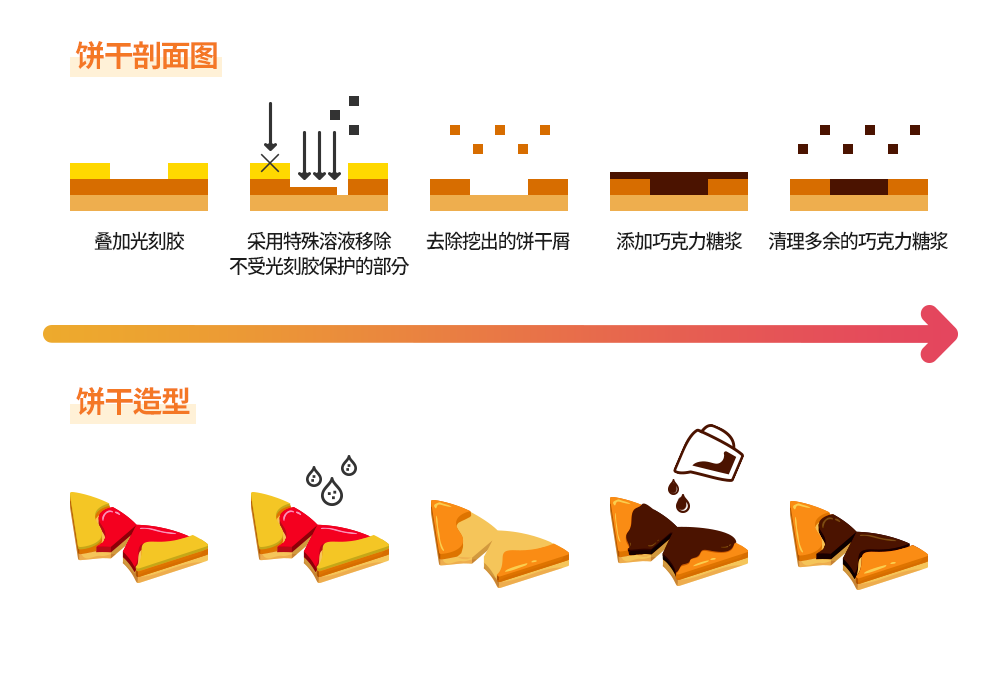

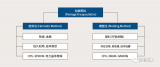

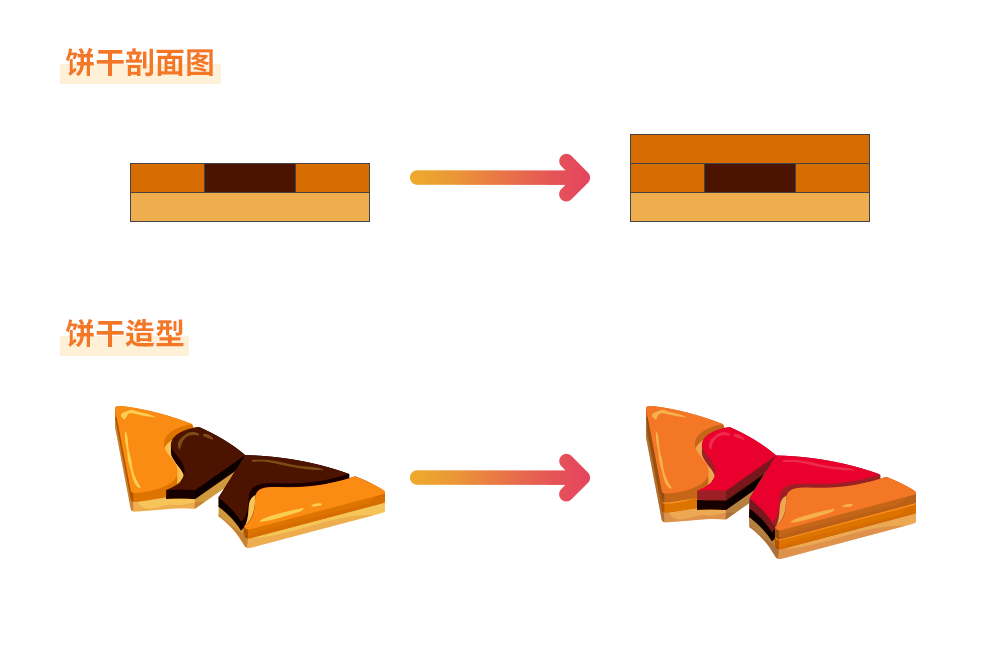

▲ 圖1: 移除餅干中間部分,再倒入巧克力糖漿

讓我們?cè)賮砘叵胍幌律弦黄獌?nèi)容中制作餅干的過程。如果想在“幸福之翼”造型餅干中加一層巧克力夾心,要怎么做呢?最簡(jiǎn)單的方法就是把餅干中間部分挖出來,再倒入巧克力糖漿。挖出餅干的這一過程,在半導(dǎo)體制程中就叫做“刻蝕”,即在“幸福之翼”餅干上疊加中間被挖空的黃色模具(光刻膠),再噴灑只與餅干裸露部分產(chǎn)生反應(yīng)的溶液,使其未受模具保護(hù)的部分被溶解腐蝕。隨后便應(yīng)移去模具,倒入巧克力糖漿。最后,清理殘余的巧克力糖漿,再蓋上一層餅干層,巧克力夾心餅干就制成了。

在半導(dǎo)體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創(chuàng)建所需的微細(xì)圖案。半導(dǎo)體“刻蝕”工藝所采用的氣體和設(shè)備,在其他類似工藝中也很常見。

02刻蝕工藝的特性

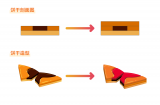

“刻蝕”工藝具有很多重要的特性。所以,在了解具體工藝之前,有必要先梳理一下刻蝕工藝的重要術(shù)語,請(qǐng)見下圖:

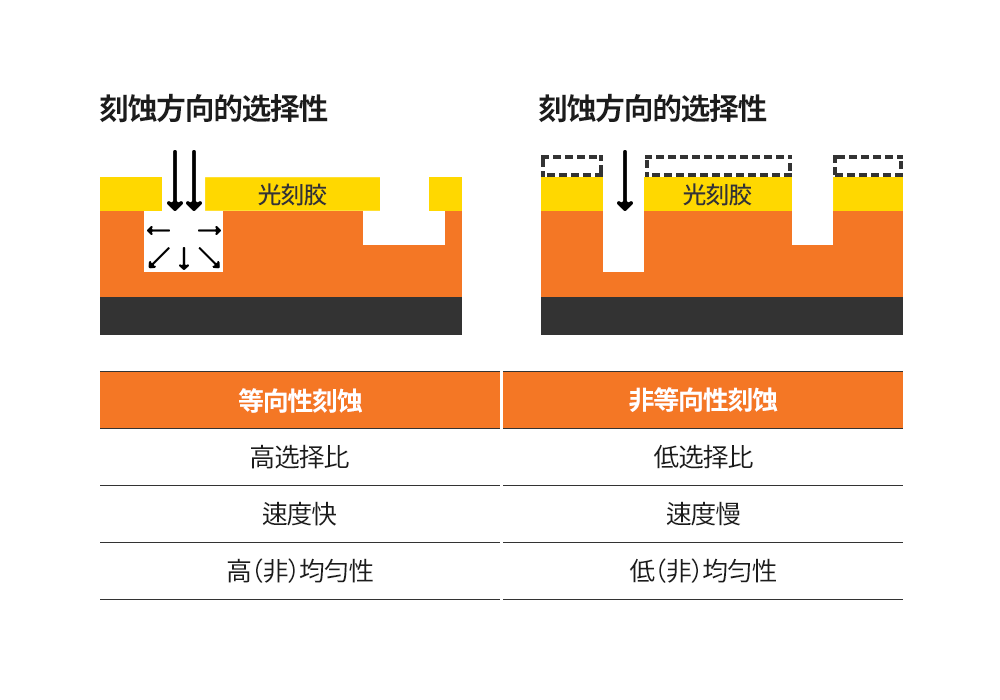

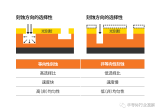

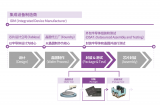

▲ 圖2: 等向性刻蝕與非等向性刻蝕的特點(diǎn)

第一個(gè)關(guān)鍵術(shù)語就是“選擇比”,該參數(shù)用于衡量是否只刻蝕了想刻蝕的部分。在反應(yīng)過程中,一部分光刻膠也會(huì)被刻蝕,因此在實(shí)際的刻蝕工藝中,不可能100%只刻蝕到想移除的部分。一個(gè)高選擇比的刻蝕工藝,便是只刻蝕了該刻去的部分,并盡可能少地刻蝕到不應(yīng)該刻蝕材料的工藝。

第二個(gè)關(guān)鍵詞,就是“方向的選擇性”。顧名思義,方向的選擇性是指刻蝕的方向。該性質(zhì)可分為等向性(Isotropic)和非等向性(Anisotropic)刻蝕兩種:等向性刻蝕沒有方向選擇性, 除縱向反應(yīng)外,橫向反應(yīng)亦同時(shí)發(fā)生;非等向性刻蝕則是借助具有方向性的離子撞擊來進(jìn)行特定方向的刻蝕,形成垂直的輪廓。試想一個(gè)包裹糖果的包裝袋漏了一道口子,如果把整塊糖連包裝袋一起放入水中,一段時(shí)間后,糖果就會(huì)被溶解。可如果只向破口處照射激光,糖果就會(huì)被燒穿,形成一個(gè)洞,而不是整塊糖果被燒沒。前一現(xiàn)象就好比等向性刻蝕,而后一現(xiàn)象就如同非等向性刻蝕。

第三個(gè)關(guān)鍵詞,就是表明刻蝕快慢的“刻蝕速率(Etching Rate)”。如果其他參數(shù)不變,當(dāng)然速率越快越好,但一般沒有又快又準(zhǔn)的完美選擇。在工藝研發(fā)過程中,往往需要在準(zhǔn)確度等參數(shù)與速率間權(quán)衡。比如,為提高刻蝕的非等向性,需降低刻蝕氣體的壓力,但降壓就意味著能夠參與反應(yīng)的氣體量變少,這自然就會(huì)帶來刻蝕速率的放緩。

最后一個(gè)關(guān)鍵詞就是“均勻性”。均勻性是衡量刻蝕工藝在整片晶圓上刻蝕能力的參數(shù),反映刻蝕的不均勻程度。刻蝕與曝光不同,它需要將整張晶圓裸露在刻蝕氣體中。該工藝在施加反應(yīng)氣體后去除副產(chǎn)物,需不斷循環(huán)物質(zhì),因此很難做到整張晶圓的每個(gè)角落都是一模一樣。這就使晶圓不同部位出現(xiàn)了不同的刻蝕速率。

03刻蝕的種類:濕刻蝕(Wet Etching)

與干刻蝕(Dry Etching)

刻蝕也像氧化工藝一樣,分為濕刻蝕(Wet Etching)和干刻蝕(Dry Etching)。還記得上一篇我們說到,取名“濕法”氧化的原因是因?yàn)椴捎昧怂魵馀c晶圓反應(yīng),而刻蝕中的“濕”則意味著將晶圓“浸入液體后撈出”。濕刻蝕的優(yōu)點(diǎn)是刻蝕速率相當(dāng)快,且只采用化學(xué)方法,所以“選擇比”較高。但其問題是只能進(jìn)行等向性(Isotropic)刻蝕。如果把晶圓浸入液體中,液體就會(huì)自由流動(dòng)與材料發(fā)生反應(yīng),光刻膠背面的受保護(hù)部分也會(huì)與液體發(fā)生反應(yīng),被快速溶解腐蝕,準(zhǔn)確度較差。而且,如果光刻膠破口很小,液體刻蝕劑將受自身表面張力影響,無法穿過破口。用***繪制了微細(xì)的圖形后,若不能照?qǐng)D形制成電路,也只是徒勞。因此,如今在制作半導(dǎo)體核心層時(shí),一般不采用濕刻蝕的方法。

▲ 圖3:?在光刻膠破口內(nèi)自由流動(dòng)的液體刻蝕劑

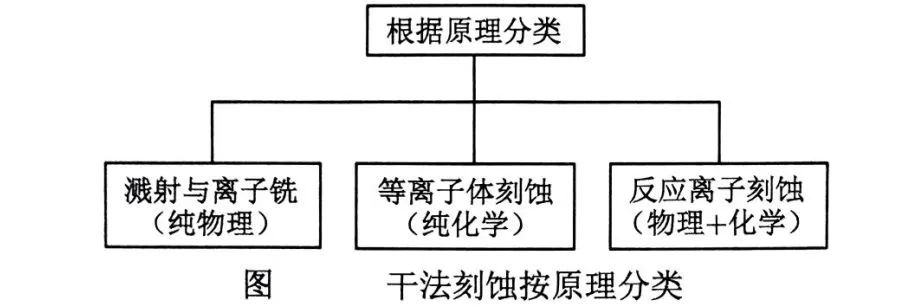

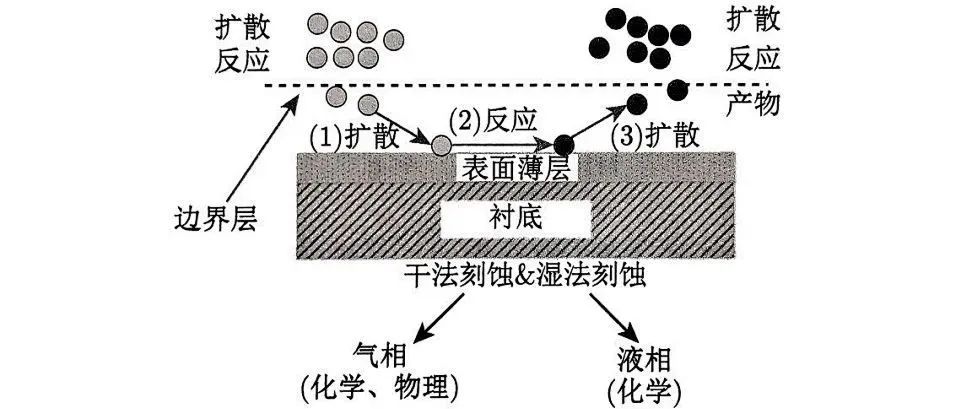

干刻蝕則泛指采用氣體進(jìn)行刻蝕的所有工藝,即在晶圓上疊加光刻膠“模具”后,將其裸露于刻蝕氣體中的工藝。干刻蝕可分為等離子刻蝕、濺射刻蝕和反應(yīng)性離子刻蝕(RIE, Reactive Ion Etching)。與濕刻蝕不同,這些干刻蝕工藝采用各種不同的方式來刻蝕材料,所以,可以一目了然地說明非等向性和等向性刻蝕的特點(diǎn)。例如,采用化學(xué)反應(yīng)的干刻蝕為等向性刻蝕,采用物理反應(yīng)的刻蝕則為非等向性刻蝕。最近,隨著RIE(非等向性高、刻蝕速率高的一種干刻蝕方法)成為主流,干刻蝕具有非等向性的認(rèn)識(shí)已成了一種共識(shí)(RIE的具體工藝請(qǐng)見下面的詳述內(nèi)容)。

04刻蝕的種類:按去除材料的方法劃分

去除晶圓上材料的方法大致可分為化學(xué)方法和物理方法兩種:

化學(xué)方法就是采用與指定材料易反應(yīng)的物質(zhì)進(jìn)行化學(xué)反應(yīng)。光刻膠下面有許多要去除的物質(zhì),如在氧化工藝中生成的氧化膜或在沉積工藝中涂敷的一些其他物質(zhì)等。化學(xué)方法就是采用易與想去除的材料產(chǎn)生反應(yīng),卻不與光刻膠發(fā)生反應(yīng)的物質(zhì),有針對(duì)性地去除材料。當(dāng)然,根據(jù)要去除的材料,所使用的刻蝕劑(氣體或液體)也不同。常用刻蝕劑有以氟或氯為基礎(chǔ)的化合物等。化學(xué)方法的優(yōu)點(diǎn)是“高選擇比”,可以只去除想去除的材料。

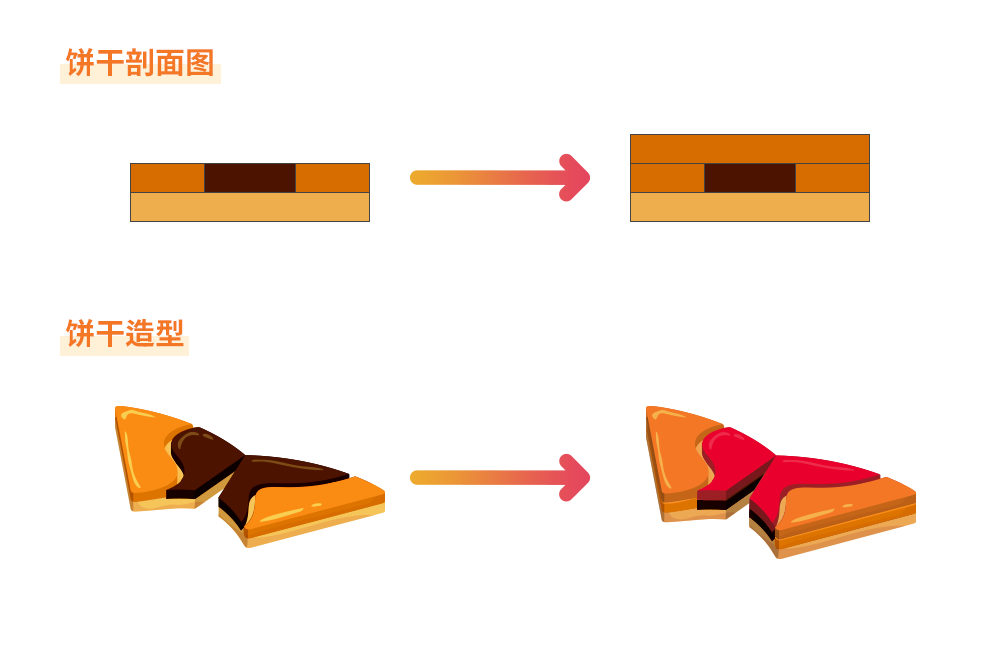

物理方法是借助具有高能量的離子撞擊晶圓表面,以去除材料,這種方法叫濺射刻蝕(Sputtering)。該方法先把氣體(主要使用惰性氣體)氣壓降低,再賦予高能量,使氣體分解為原子(+)與電子(-)。此時(shí),朝晶圓方向施加電場(chǎng),原子就會(huì)在電場(chǎng)作用下加速與晶圓發(fā)生沖撞。

這種方法的原理很簡(jiǎn)單,但在實(shí)際工藝中,僅憑這一原理很難達(dá)成目的。低氣壓意味著參加反應(yīng)的氣體量少,刻蝕速率當(dāng)然就會(huì)慢下來。而且,采用物理方法時(shí),會(huì)移除較大面積的本不該去除的材料。物理方法采用強(qiáng)行用力刻出材料的方法,發(fā)生沖撞時(shí)不會(huì)區(qū)分“應(yīng)該”還是“不應(yīng)該”去除的材料。(在后續(xù)介紹沉積工藝的沉積氣體時(shí)也會(huì)說到濺射方法,大家不妨記住,有助于下文的理解。)

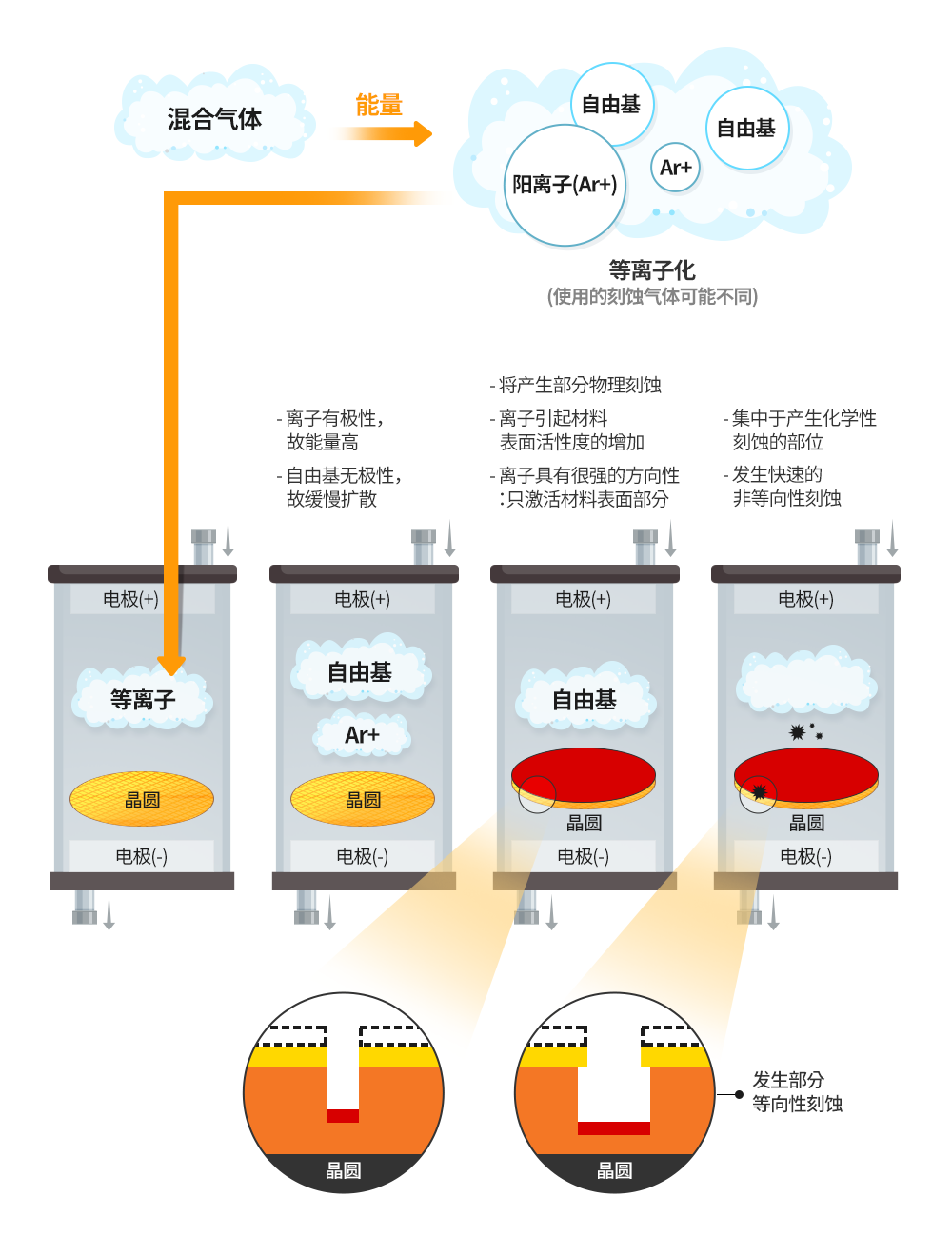

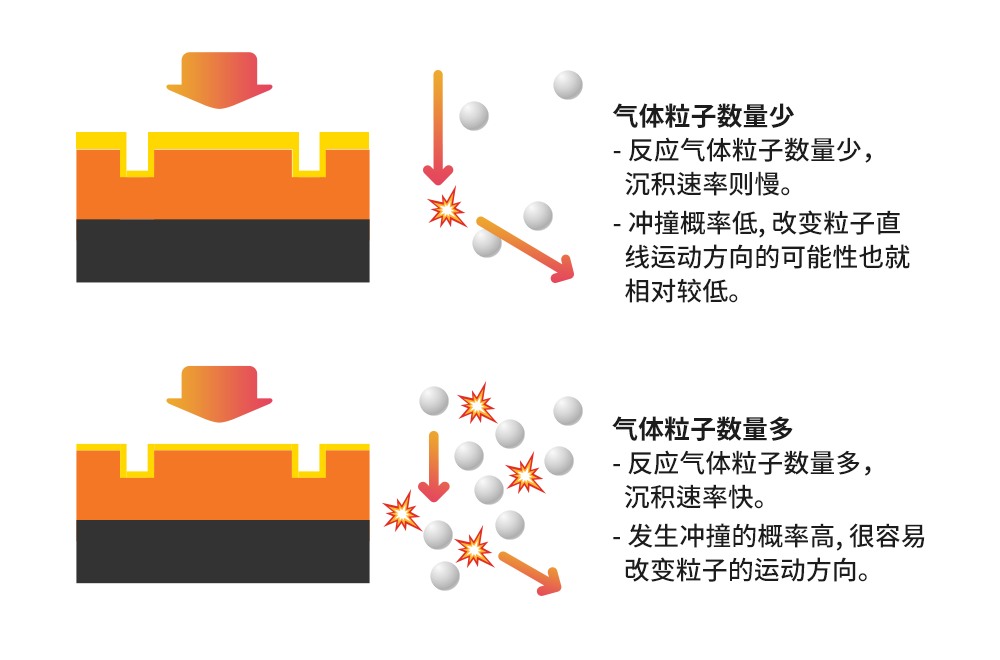

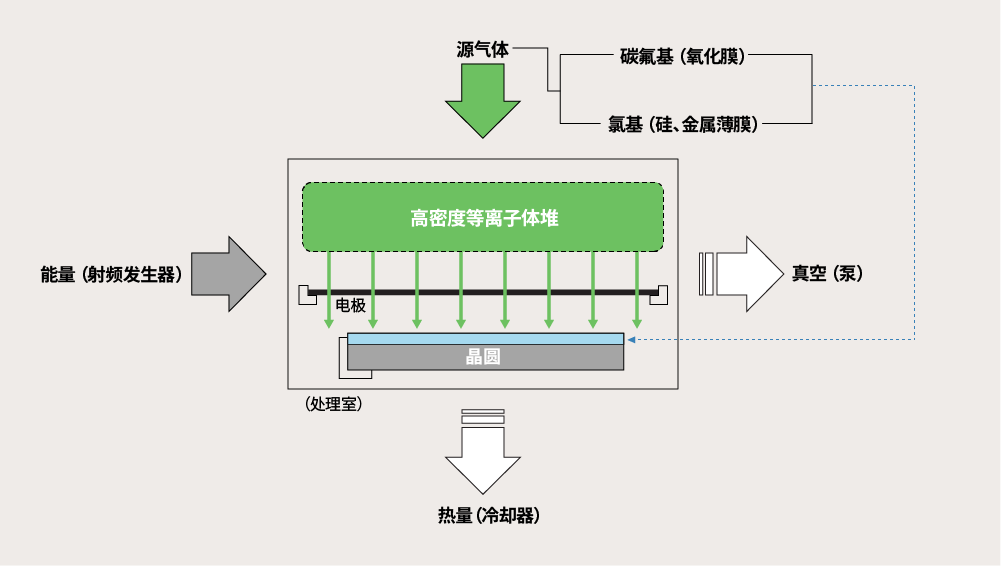

因此,在實(shí)際的刻蝕工藝中,我們主要采用將化學(xué)和物理方法相結(jié)合的反應(yīng)性離子刻蝕(RIE, Reactive Ion Etching)。RIE屬于干刻蝕的一種,它將刻蝕氣體變成等離子,以進(jìn)行刻蝕。具體而言,這種方法在設(shè)備內(nèi)投入混合氣體(反應(yīng)氣體與惰性氣體)后,賦予氣體高能量,使其分解為電子(Electron)、陽離子(Positive Ion)和自由基(Radical)*。質(zhì)量較輕的電子基本上起不了什么作用,而在電場(chǎng)中向陽離子施加沖向晶圓方向的加速度,就會(huì)發(fā)生物理刻蝕。陽離子具有正電荷,在電場(chǎng)中加速時(shí)方向性很強(qiáng)。到這里,是不是與物理方法沒什么兩樣呢?

* 自由基:指氣體具有不成對(duì)電子等高反應(yīng)性的狀態(tài)。

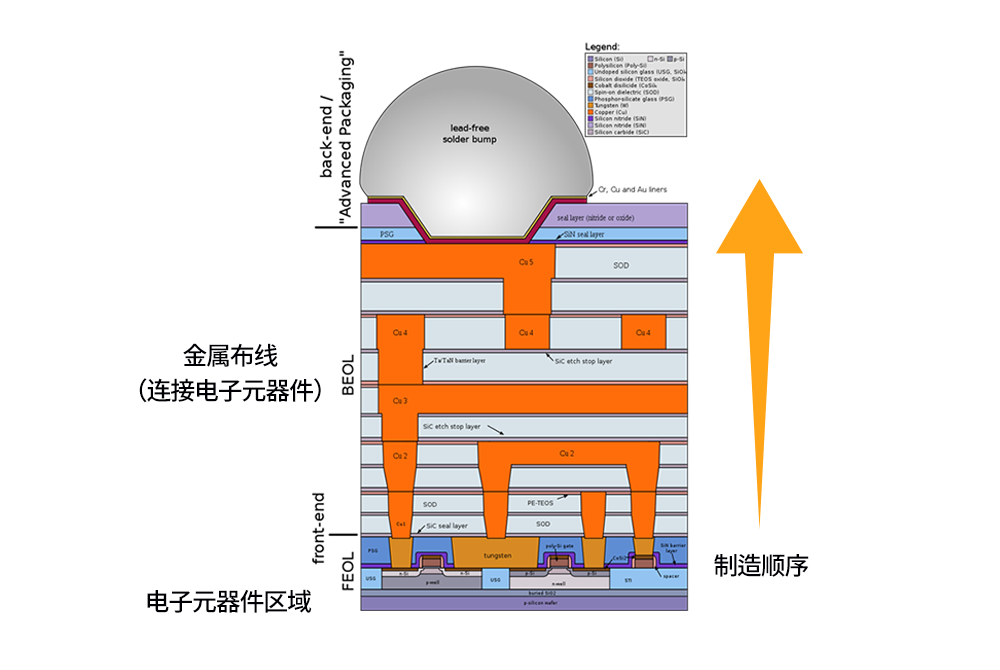

▲ 圖4: RIE工藝概要

然而,在這一過程中,陽離子還會(huì)起到一個(gè)作用:弱化被撞擊材料的化學(xué)鍵。電場(chǎng)使陽離子徑直向前發(fā)射出去,會(huì)集中撞到圖4所示的紅色部分。側(cè)壁化學(xué)鍵穩(wěn)固,而正面化學(xué)鍵因撞擊被弱化。隨后接觸具有極高化學(xué)活性的自由基,正面材料便會(huì)有更高的刻蝕速率,最終造就非等向性很高的刻蝕。

可見,等離子刻蝕技術(shù)可謂是“一舉三得”:① 生成陽離子,產(chǎn)生物理性刻蝕;② 使被刻蝕材料的化學(xué)鍵變?nèi)酰虎?還能提高刻蝕氣體的反應(yīng)性。既取了化學(xué)刻蝕之長(zhǎng) —— “高選擇比”,又不失物理刻蝕的優(yōu)點(diǎn) ——“非等向性刻蝕”。

當(dāng)然,即便采用RIE,僅憑刻蝕工藝也很難100%得到所需的圖形。如果要解決其他問題,還需要改變氣體組合、采用硬掩模(Hard Mask)*的其他工藝或新材料的幫助。

* 硬掩膜(Hard Mask):為防止因圖形微細(xì)化而造成光刻膠上的圖形被破壞,在其下方額外添加的掩模版

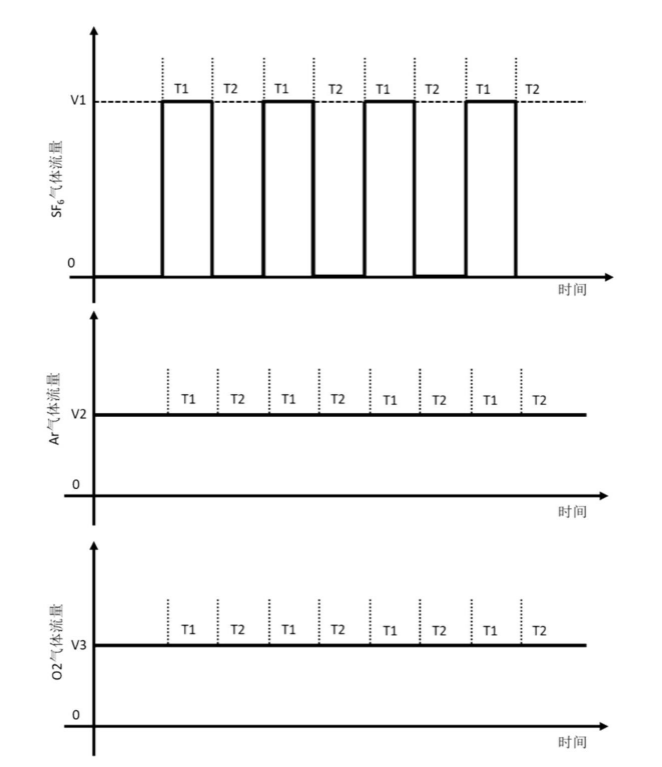

05刻蝕氣體與附加氣體

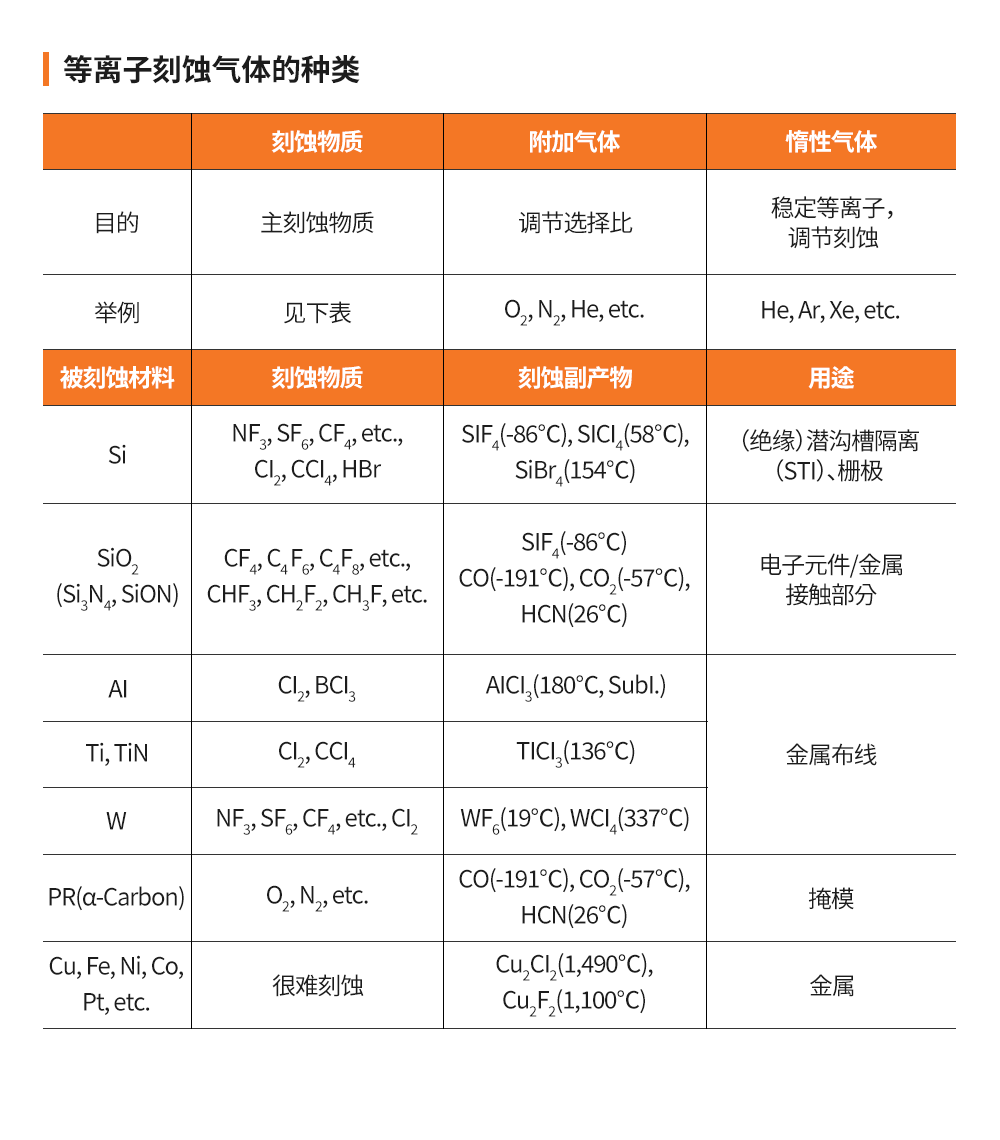

刻蝕工藝中所使用的氣體非常重要。從上述內(nèi)容中可以看出,刻蝕工藝的核心就是化學(xué)反應(yīng)。所以,我們要根據(jù)想去除的材料,選擇相應(yīng)的刻蝕劑(Etchant)進(jìn)行刻蝕。選擇刻蝕氣體時(shí),要衡量反應(yīng)生成的副產(chǎn)物是否容易被去除、刻蝕選擇比是否夠高和刻蝕速率是否足夠快等因素。經(jīng)常采用的刻蝕氣體有氟(F)、氯(CI)、溴(Br)等鹵族元素化合物。

▲ 圖5: 等離子刻蝕氣體的種類(摘自:(株)圖書出版HANOL出版社[半導(dǎo)體制造技術(shù)的理解443p])

在半導(dǎo)體的制程中,晶圓表面會(huì)涂敷各種物質(zhì)。因此,從理論上來講,要刻蝕的材料有無數(shù)種。我們主要舉幾個(gè)代表性的例子。比如,硅(Si)系列元素采用氟系氣體可以輕易去除。硅遇氟立即反應(yīng)生成很容易被氣化的氟化硅。SiF4就是氟化硅的一種,在標(biāo)準(zhǔn)大氣壓下,其熔點(diǎn)為-90.3℃。也就是說,反應(yīng)后生成的SiF4將立即氣化成氣體消散,即在晶體表面發(fā)生刻蝕的同時(shí)立刻變成氣體。

常用作絕緣或保護(hù)膜的二氧化硅(SiO2)也很容易被含氟氣體去除。與純硅不同,二氧化硅已經(jīng)是硅元素與氧結(jié)合形成的穩(wěn)定化合物(硅燃燒后的粉塵),所以需要使用發(fā)熱的氣體才能將其去除。氟與碳(C)結(jié)合的氣體便是常用于去除二氧化硅的刻蝕氣體。通過發(fā)熱反應(yīng),該氣體可奪取與氧氣結(jié)合的硅原子。

HKMG*、BEOL*等工藝則需要刻蝕金屬性材料。金屬性材料一般易與鹵族元素(氯、氟等)發(fā)生反應(yīng),但其副產(chǎn)物的熔點(diǎn)非常高,所以很難去除。以銅為例,銅與氣體反應(yīng)產(chǎn)生的副產(chǎn)物熔點(diǎn)在1,000℃以上。也就是說,銅遇到刻蝕氣體后,晶圓表面就會(huì)像生了銹一樣,想去除這層“銹”,需要向晶圓施加1,000℃的高溫,但這樣一來其他重要的電子元件就很有可能被燒毀。因此,即便銅具有非常出色的電氣特性,它卻在鋁的電氣特性逼近物理極限時(shí)才被引進(jìn)作為材料。而且,為了克服銅的這種“缺陷”,還需引進(jìn)名為鑲嵌(Damascene)*的新工藝。所以,大家要時(shí)刻記住,重點(diǎn)并不在于新材料本身是否具有良好的物理特性,而是在于與其一同引進(jìn)的新工藝是否與已有工藝相匹配,可以實(shí)現(xiàn)量產(chǎn)。

其實(shí),在實(shí)際工藝中,我們很難根據(jù)要去除的材料挑選出完美的刻蝕氣體。例如,對(duì)去除硅奏效的氣體對(duì)去除二氧化硅也同樣奏效(反之亦然)。如果硅與二氧化硅同在,但想更多地去除其中一種材料怎么辦?這時(shí),如何制作混合氣體成了關(guān)鍵。例如,調(diào)高氟氣中的碳比例,發(fā)熱反應(yīng)就會(huì)更加激烈, SiO2的選擇比自然就會(huì)變高。

附加氣體也很重要。我們可以通過在刻蝕氣體添加氧氣(O2)、氮?dú)猓∟2)和氫氣(H2)等各種其他附加氣體,使刻蝕氣體具有某種特性。例如,在去除硅時(shí)附加氫氣,可生成提高非等向性刻蝕的內(nèi)壁。此外,還可添加部分惰性氣體。其中,氖氣(Ne)就是非常典型的惰性氣體之一,它在可調(diào)節(jié)刻蝕氣體濃度的同時(shí),還可提供物理性刻蝕的效果。

* HKMG(High-K Metal Gate): 可有效減少電流泄露的新一代MOSFET柵極;是一種以金屬代替?zhèn)鹘y(tǒng)的多晶硅(Polysilicon)柵極并以高介電(High-K)取代氧化硅絕緣膜的晶體管。

* 后端工藝(BEOL,Back End Of the Line):通過細(xì)微的金屬布線在多達(dá)數(shù)十億個(gè)電子元器件之間形成連接的工藝

* 鑲嵌(Damascene):為使用銅作為金屬布線材料所需的工藝。該工藝先刻蝕金屬布線的位置,隨后沉積金屬,再通過物理方法去除多余的部分。

06結(jié)論:提高密度的另一個(gè)抓手

一言以蔽之,刻蝕工藝就是結(jié)合物理和化學(xué)方法以形成微細(xì)圖案的半導(dǎo)體制程工藝的核心。刻蝕雖然不能像***一樣,直接繪制精密的圖形,但可通過調(diào)節(jié)氣體比例、溫度、電場(chǎng)強(qiáng)度和氣壓等各種參數(shù),使晶圓的數(shù)千億個(gè)晶體管具有相同的圖形。

近來,以進(jìn)一步升級(jí)***來提高密度的方法已達(dá)到了瓶頸。刻蝕工藝的重要性自然更加突顯。CPU和AP等產(chǎn)品中的鰭式場(chǎng)效電晶體(FinFET)*就是很好的一個(gè)案例。

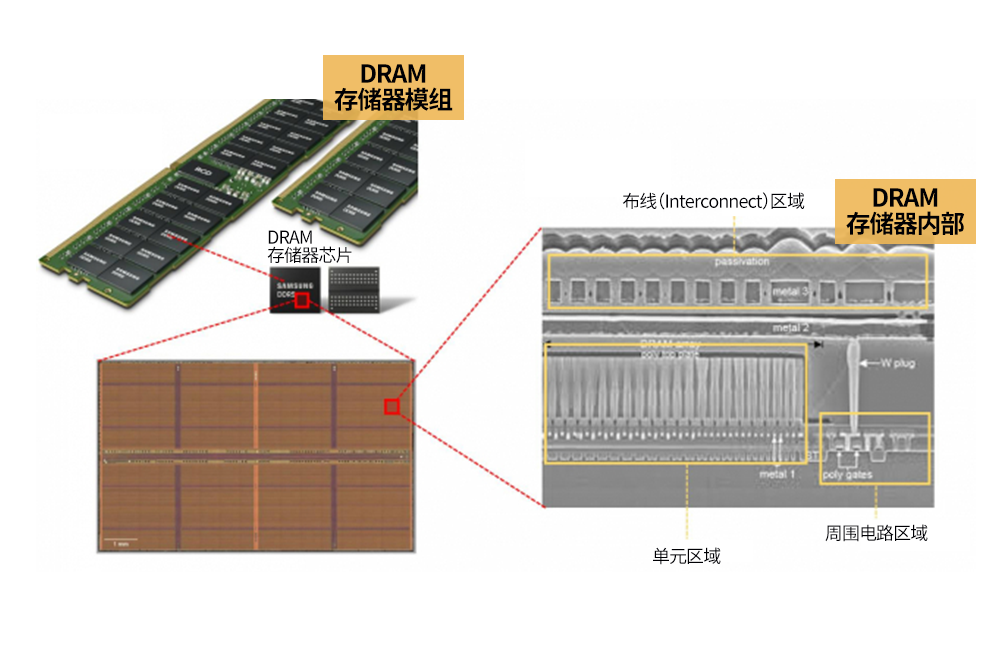

尤其對(duì)于SK海力士這種半導(dǎo)體存儲(chǔ)器制造商來說,動(dòng)態(tài)隨機(jī)存儲(chǔ)器(DRAM)和閃存(NAND)等主打產(chǎn)品對(duì)刻蝕工藝的依存度非常高。比如,DRAM中裝載數(shù)據(jù)的電容(Capacitor)要堆疊得更高,而NAND則需要先實(shí)現(xiàn)三維化,一次刻蝕就要穿透100多層。由于這些產(chǎn)品必然會(huì)不斷拉高深寬比(Aspect Ratio)*,為確保可靠度,開始刻蝕的部分與底邊直徑要相差無幾。可見刻蝕工藝有待解決的問題仍然很多。

* 鰭式場(chǎng)效電晶體(FinFET,F(xiàn)in Field-Effect Transistor):三維MOSFET的一種,因電晶體的形狀與魚鰭相似而得名。

* 深寬比(Aspect Ratio,也稱縱橫比):刻蝕高度與寬度的比值。深寬比越高就表示穿透得越深。

▲ 圖6: DRAM的內(nèi)部結(jié)構(gòu);單元區(qū)域內(nèi)許多纖細(xì)縱向的結(jié)構(gòu)即為電容?

相信讀者們可以從本篇刻蝕工藝介紹中再一次體會(huì)到半導(dǎo)體制程工藝間緊密相連并相互影響。上文也說到,硅與二氧化硅遇氟可立即氣化成氣體揮發(fā)。但如果把晶圓材質(zhì)變成鍺(Ge)等其他材料,即便本身具有很好的物理特性,但只要它們無法經(jīng)刻蝕、沉積等工藝加工,便沒有意義。

如今,制造技術(shù)的突破變得愈發(fā)艱難,筆者希望直接或間接從事半導(dǎo)體領(lǐng)域工作的人員們也能清楚地認(rèn)識(shí)到這一事實(shí)。為了攻克剩下的障礙,我們對(duì)上下游相關(guān)工藝也要非常了解,還要與相關(guān)部門密切溝通。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論