隨著現(xiàn)代數(shù)字電子系統(tǒng)突破1 GHz的壁壘,PCB板級(jí)設(shè)計(jì)和IC封裝設(shè)計(jì)必須都要考慮到信號(hào)完整性和電氣性能問(wèn)題。 凡是介入物理設(shè)計(jì)的人都可能會(huì)影響產(chǎn)品的性能。所有的設(shè)計(jì)師都應(yīng)該了解設(shè)計(jì)如何影響信號(hào)完整性,至少能夠和信號(hào)完整性專業(yè)的工程師進(jìn)行技術(shù)上的溝通。 當(dāng)快速地得到粗略的結(jié)果比以后得到精確的結(jié)果更重要時(shí),我們就使用經(jīng)驗(yàn)法則。

經(jīng)驗(yàn)法則只是一種大概的近似估算,它的設(shè)計(jì)目的是以最小的工作量,以知覺(jué)為基礎(chǔ)找到一個(gè)快速的答案。經(jīng)驗(yàn)法則是估算的出發(fā)點(diǎn),它可以幫助我們區(qū)分5或50,而且它能幫助我們?cè)谠O(shè)計(jì)的早期階段就對(duì)設(shè)計(jì)有較好的整體規(guī)劃。

下面是具有40年研究經(jīng)驗(yàn)的國(guó)際大師Eric Bogatin給出的100條估計(jì)信號(hào)完整性效應(yīng)的經(jīng)驗(yàn)法則。

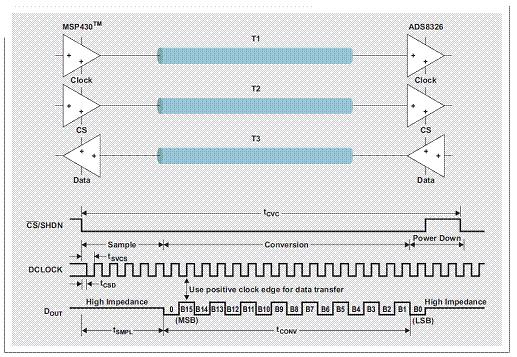

1、信號(hào)上升時(shí)間約是時(shí)鐘周期的10%,即1/10x1/Fclock。例如100MHZ 使中的上升時(shí)間大約是1NS.

2、理想方波的N 次諧波的振幅約是時(shí)鐘電壓副值的2/(N 派)倍。例如,1V時(shí)鐘信號(hào)的第一次諧波幅度約為0.6V,第三次諧波的幅度約是0.2V。

3、信號(hào)的帶寬和上升時(shí)間的關(guān)系為:BW=0.35/RT。例如,如果上升時(shí)間是1NS,

則帶寬是350MHZ。如果互連線的帶寬是3GHZ,則它可傳輸?shù)淖疃躺仙龝r(shí)間約為0.1NS。

4、如果不知道上升時(shí)間,可以認(rèn)為信號(hào)帶寬約是時(shí)鐘頻率的5 倍。

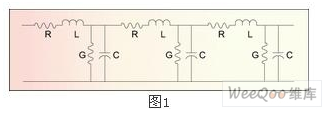

5、LC 電路的諧振頻率是5GHZ/sqrt(LC),L 的單位為NH,C 的單位為PF。

6、在400MHZ 內(nèi),軸向引腳電阻可以看作理想電阻;在2GHZ 內(nèi),SMT0603電阻可看作理想電阻。

7、軸向引腳電阻的ESL(引腳電阻)約為8NH,SMT 電阻的ESL 約是1.5NH。

8、直徑為1MIL 的近鍵合線的單位長(zhǎng)度電阻約是1 歐姆/IN。

9、24AWG 線的直徑約是20MIL,電阻率約為25 毫歐姆/FT。

10、 1 盎司桶線條的方塊電阻率約是每方塊0.5 豪歐姆。

11、 在10MHZ 時(shí),1 盎司銅線條就開始具有趨膚效應(yīng)。

12、 直徑為1IN 球面的電容約是2PF。

13、 硬幣般大小的一對(duì)平行板,板間填充空氣時(shí),他們間的電容約為1PF。

14、 當(dāng)電容器量板間的距離與板子的寬度相當(dāng)時(shí),則邊緣產(chǎn)生的電容與平行板形成的產(chǎn)生的電容相等。例如,在估算線寬為10MIL、介質(zhì)厚度為10MIL的微帶線的平行板電容時(shí),其估算值為1PF/IN,但實(shí)際的電容約是上述的兩倍,也就是2PF/IN。

15、 如果問(wèn)對(duì)材料特性一無(wú)所知,只知道它是有機(jī)絕緣體,則認(rèn)為它的介電

常數(shù)約為4。

16、 1 片功率為1W 的芯片,去耦電容(F)可以提供電荷使電壓降小于小于

5%的時(shí)間(S)是C/2。

17、 在典型電路板鐘,當(dāng)介質(zhì)厚度為10MIL 時(shí),電源和地平面間的耦合電容

是100PF/IN 平方,并且它與介質(zhì)厚度成反比。

18、 如果50 歐姆微帶線的體介電常數(shù)為4,則它的有效介電常數(shù)為3。

19、 直徑為1MIL 的圓導(dǎo)線的局部電感約是25NH/IN 或1NH/MM。

20、 由10MIL 厚的線條做成直徑為1IN 的一個(gè)圓環(huán)線圈,它的大小相當(dāng)于拇

指和食指圍在一起,其回路電感約為85NH。

21、 直徑為1IN 的圓環(huán)的單位長(zhǎng)度電感約是25NH/IN 或1NH/MM。例如,如

果封裝引線是環(huán)形線的一部分,且長(zhǎng)為0.5IN,則它的電感約是12NH。

22、 當(dāng)一對(duì)圓桿的中心距離小于它們各自長(zhǎng)度的10%時(shí),局部互感約是各自

的局部互感的50%。

23、 當(dāng)一對(duì)圓桿中心距與它們的自身長(zhǎng)度相當(dāng)時(shí),它們之間的局部互感比它

們各自的局部互感的10%還要少。

24、 SMT 電容(包括表面布線、過(guò)孔以及電容自身)的回路電感大概為2NH,

要將此數(shù)值降至1NH 以下還需要許多工作。

25、 平面對(duì)上單位面積的回路電感是33PHx 介質(zhì)厚度(MIL)。

26、 過(guò)孔的直徑越大,它的擴(kuò)散電感就越低。一個(gè)直徑為25MIL 過(guò)孔的擴(kuò)散電感約為50PH。

27、 如果有一個(gè)出沙孔區(qū)域,當(dāng)空閑面積占到50%時(shí),將會(huì)使平面對(duì)間的回路電感增加25%。

28、 銅的趨膚深度與頻率的平方跟成反比。1GHZ 時(shí),其為2UM。所以,10MHZ 時(shí),銅的趨膚是20UM。

29、 在50 歐姆的1 盎司銅傳輸線中,當(dāng)頻率約高于50MHZ 時(shí),單位長(zhǎng)度回路電感為一常數(shù)。這說(shuō)明在頻率高于50MHZ 時(shí),特性阻抗時(shí)一常數(shù)。

30、 銅中電子的速度極慢,相當(dāng)于螞蟻的速度,也就是1CM/S。

31、 信號(hào)在空氣中的速度約是12IN/NS。大多數(shù)聚合材料中的信號(hào)速度約為6IN/NS。

32、 大多數(shù)輾壓材料中,線延遲1/V 約是170PS/IN。

33、 信號(hào)的空間延伸等于上升時(shí)間X 速度,即RTx6IN/NS。

34、 傳輸線的特性阻抗與單位長(zhǎng)度電容成反比。

35、 FR4 中,所有50 歐姆傳輸線的單位長(zhǎng)度電容約為3.3PF/IN。

36、 FR4 中,所有50 歐姆傳輸線的單位長(zhǎng)度電感約為8.3NH/IN。

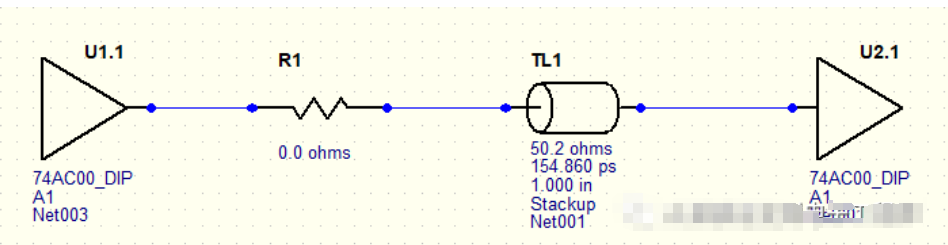

37、 對(duì)于FR4 中的50 歐姆微帶線,其介質(zhì)厚度約是線寬的一半。

38、 對(duì)于FR4 中的50 歐姆帶狀線,其平面間的間隔時(shí)信號(hào)線線寬的2 倍。

39、 在遠(yuǎn)小于信號(hào)的返回時(shí)間之內(nèi),傳輸線的阻抗就是特性阻抗。例如,當(dāng)驅(qū)動(dòng)一段3IN 長(zhǎng)的50 歐姆傳輸線時(shí),所有上升時(shí)間短與1NS 的驅(qū)動(dòng)源在沿線傳輸并發(fā)生上升跳變時(shí)間內(nèi)感受到的就是50 歐姆恒定負(fù)載。

40、 一段傳輸線的總電容和時(shí)延的關(guān)系為C=TD/Z0。

41、 一段傳輸線的總回路電感和時(shí)延的關(guān)系為L(zhǎng)=TDxZ0。

42、 如果50 歐姆微帶線中的返回路徑寬度與信號(hào)線寬相等,則其特性阻抗比返回路徑無(wú)限寬時(shí)的特性阻抗高20%。

43、 如果50 歐姆微帶線中的返回路徑寬度至少時(shí)信號(hào)線寬的3 倍,則其特性阻抗與返回路徑無(wú)限寬時(shí)的特性阻抗的偏差小于1%。

44、 布線的厚度可以影響特性阻抗,厚度增加1MIL,阻抗就減少2 歐姆。

45、 微帶線定部的阻焊厚度會(huì)使特性阻抗減小,厚度增加1MIL,阻抗減少2歐姆。

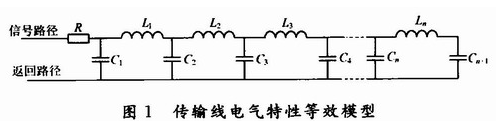

46、 為了得到精確的集總電路近似,在每個(gè)上升時(shí)間的空間延伸里至少需要有3.5 個(gè)LC 節(jié)。

47、 單節(jié)LC 模型的帶寬是0.1/TD。

48、 如果傳輸線時(shí)延比信號(hào)上升時(shí)間的20%短,就不需要對(duì)傳輸線進(jìn)行端接。

49、 在50 歐姆系統(tǒng)中,5 歐姆的阻抗變化引起的反射系數(shù)是5%。

50、 保持所有的突變(IN)盡量短于上升時(shí)間(NS)的量值。

51、 遠(yuǎn)端容性負(fù)載會(huì)增加信號(hào)的上升時(shí)間。10-90 上升時(shí)間約是(100xC)PS,其中C 的單位是PF。

52、 如果突變的電容小于0.004XRT,則可能不會(huì)產(chǎn)生問(wèn)題。

53、 50 歐姆傳輸線中拐角的電容(Ff)是線寬(MIL)的2 倍。

54、 容性突變會(huì)使50%點(diǎn)的時(shí)延約增加0.5XZ0XC。

55、 如果突變的電感(NH)小于上升時(shí)間(NS)的10 倍,則不會(huì)產(chǎn)生問(wèn)題。

56、 對(duì)上升時(shí)間少于1NS 的信號(hào),回路電感約為10NH 的軸向引腳電阻可能會(huì)產(chǎn)生較多的反射噪聲,這時(shí)可換成片式電阻。

57、 在50 歐姆系統(tǒng)中,需要用4PF 電容來(lái)補(bǔ)償10NH 的電感。

58、 1GHZ 時(shí),1 盎司銅線的電阻約是其在DC 狀態(tài)下電阻的15 倍。

59、 1GHZ 時(shí),8MIL 寬的線條的電阻產(chǎn)生的衰減與介質(zhì)此材料產(chǎn)生的衰減相當(dāng),并且介質(zhì)材料產(chǎn)生的衰減隨著頻率變化得更快。

60、 對(duì)于3MIL或更寬的線條而言,低損耗狀態(tài)全是發(fā)生在10MHZ頻率以上。在低損耗狀態(tài)時(shí),特性阻抗以及信號(hào)速度與損耗和頻率無(wú)關(guān)。在常見的級(jí)互連中不存在由損耗引起的色散現(xiàn)象。

61、 -3DB 衰減相當(dāng)于初始信號(hào)功率減小到50%,初始電壓幅度減小到70%。

62、 -20DB 衰減相當(dāng)于初始信號(hào)功率減小到1%,初始電壓幅度減小到10%。

63、 當(dāng)處于趨膚效應(yīng)狀態(tài)時(shí),信號(hào)路徑與返回路徑的單位長(zhǎng)度串聯(lián)約是(8/W)Xsqrt(f)(其中線寬W:MIL;頻率F:GHZ)。

64、 50 歐姆的傳輸線中,由導(dǎo)體產(chǎn)生的單位長(zhǎng)度衰減約是36/(Wz0)DB/IN。

65、 FR4 的耗散因子約是0.02。

66、 1GHZ 時(shí),F(xiàn)R4 中由介質(zhì)材料產(chǎn)生的衰減約是0.1DB/IN,并隨頻率線性增加。

67、 對(duì)于FR4 中的8MIL 寬、50 歐姆傳輸線,在1GHZ 時(shí),其導(dǎo)體損耗與介質(zhì)材料損耗相等。

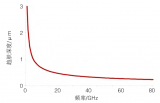

68、 受損耗因子的制約,F(xiàn)R4 互連線(其長(zhǎng)是LEN)的帶寬約是30GHZ/LEN。

69、 FR4 互連線可以傳播的最短時(shí)間是10PS/INxLEN。

70、 如果互連線長(zhǎng)度(IN)大于上升時(shí)間(NS)的50 倍,則FR4 介質(zhì)板中由損耗引起的上升邊退化是不可忽視的。

71、 一對(duì)50 歐姆微帶傳輸線中,線間距與線寬相等時(shí),信號(hào)線間的耦合電容約占5%。

72、 一對(duì)50 歐姆微帶傳輸線中,線間距與線寬相等時(shí),信號(hào)線間的耦合電感約占15%。

73、 對(duì)于1NS 的上升時(shí)間,F(xiàn)R4 中近端噪聲的飽和長(zhǎng)度是6IN,它與上升時(shí)間成比例。

74、 一跟線的負(fù)載電容是一個(gè)常數(shù),與附近其他線條的接近程度無(wú)關(guān)。

75、 對(duì)于50 歐姆微帶線,線間距與線寬相等時(shí),近端串?dāng)_約為5%。

76、 對(duì)于50 歐姆微帶線,線間距是線寬的2 倍時(shí),近端串?dāng)_約為2%。

77、 對(duì)于50 歐姆微帶線,線間距是線寬的3 倍時(shí),近端串?dāng)_約為1%。

78、 對(duì)于50 歐姆帶狀線,線間距與線寬相等時(shí),近端串?dāng)_約為6%。

79、 對(duì)于50 歐姆帶狀線,線間距是線寬的2 倍時(shí),近端串?dāng)_約為2%。

80、 對(duì)于50 歐姆帶狀線,線間距是線寬的3 倍時(shí),近端串?dāng)_約為0.5%。

81、 一對(duì)50 歐姆微帶傳輸線中,間距與線寬相等時(shí),遠(yuǎn)端噪聲是4%Xtd/rt。如果線時(shí)延是1ns,上升時(shí)間時(shí)0.5ns,則遠(yuǎn)端噪聲是8%。

82、 一對(duì)50 歐姆微帶傳輸線中,間距是線寬的2 倍時(shí),遠(yuǎn)端噪聲是2%Xtd/rt。如果線時(shí)延是1ns,上升時(shí)間時(shí)0.5ns,則遠(yuǎn)端噪聲是4%。

83、 一對(duì)50歐姆微帶傳輸線中,間距是線寬的3 倍時(shí),遠(yuǎn)端噪聲是1.5%Xtd/rt。如果線時(shí)延是1ns,上升時(shí)間時(shí)0.5ns,則遠(yuǎn)端噪聲是4%。

84、 帶狀線或者完全嵌入式微帶線上沒(méi)有遠(yuǎn)端噪聲。

85、 在50 歐姆總線中,不管是帶狀線還是微帶線,要使最懷情況下的遠(yuǎn)端噪聲低于5%,就必須保持線間距大于線寬的2 倍。

86、 在50 歐姆總線中,線間距離等于線寬時(shí),受害線上75%的竄擾來(lái)源于受害線兩邊鄰近的那兩跟線。

87、 在50 歐姆總線中,線間距離等于線寬時(shí),受害線上95%的竄擾來(lái)源于受害線兩邊距離最近的每邊各兩根線條。

88、 在50 歐姆總線中,線間距離是線寬的2 倍時(shí),受害線上100%的竄擾來(lái)源于受害線兩邊鄰近的那兩根線條。這是忽略與總線中其他所有線條間的耦合。

89、 對(duì)于表面布線,加大相鄰信號(hào)線間的距離使之足以添加一個(gè)防護(hù)布線,串?dāng)_常常就會(huì)減小到一個(gè)可以接受的水平,而且這是沒(méi)必要增加防護(hù)布線。添加終端短接的防護(hù)布線可將串?dāng)_減小到50%。

90、 對(duì)于帶狀線,使用防護(hù)線可以使串?dāng)_減小到不用防護(hù)線時(shí)的10%。

91、 為了保持開關(guān)噪聲在可以接受的水平,必須時(shí)互感小于2.5nhx 上升時(shí)間(ns)。

92、 對(duì)于受開關(guān)噪聲限制的接插件或者封裝來(lái)說(shuō),最大可用的時(shí)鐘頻率是

250MHZ/(NxLm)。其中,Lm 是信號(hào)/返回路徑對(duì)之間的互感(nh),N 是同時(shí)開館的數(shù)量。

93、 在LVDS 信號(hào)中,共模信號(hào)分量是比差分信號(hào)分量達(dá)2 倍以上。

94、 如果之間沒(méi)有耦合,差分對(duì)的差分阻抗是其中任意一個(gè)單端線阻抗的2倍。

95、 一對(duì)50 歐姆微帶線,只要其中一跟線的電壓維持在高或低不變,則另一跟線的單端特性阻抗就與鄰近線的距離完全無(wú)關(guān)。

96、 在緊耦合差分微帶線中,與線寬等于線間距時(shí)的耦合相比,線條離得很遠(yuǎn)而沒(méi)有耦合時(shí),差分特性阻抗僅會(huì)降低10%左右。

97、 對(duì)于寬邊耦合差分對(duì),線條間的距離應(yīng)至少比線寬大,這么做的目的是為了獲得可高達(dá)100 歐姆的查分阻抗。

98、 FCC的B級(jí)要求是,在100MHZ 時(shí),3M遠(yuǎn)處的遠(yuǎn)場(chǎng)強(qiáng)度要小于150UV/M.

99、 鄰近的單端攻擊次線在強(qiáng)耦合差分對(duì)上產(chǎn)生的差分信號(hào)串?dāng)_比弱耦合差分對(duì)上的少30%。

100、 鄰近的單端攻擊次線在強(qiáng)耦合差分對(duì)上產(chǎn)生的共模信號(hào)串?dāng)_比弱耦合差分對(duì)上的多30%。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論