上篇文章,使用嵌套switch-case法的狀態(tài)機(jī)編程,實(shí)現(xiàn)了一個(gè)炸彈拆除小游戲。本篇,繼續(xù)介紹狀態(tài)機(jī)編程的第二種方法:狀態(tài)表法,來實(shí)現(xiàn)炸彈拆除小游戲的狀態(tài)機(jī)編程。

2023-06-20 09:05:05 3563

3563

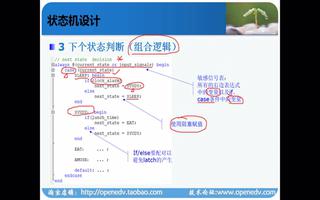

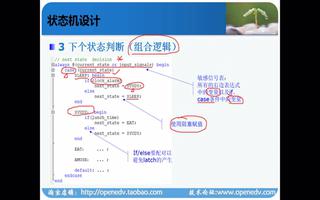

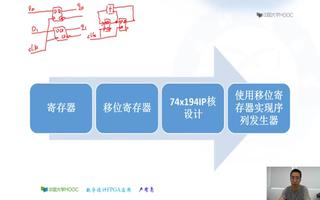

安全高效的狀態(tài)機(jī)設(shè)計(jì)對(duì)于任何使用FPGA的工程師而言都是一項(xiàng)重要技能。選擇Moore狀態(tài)機(jī)、Mealy狀態(tài)機(jī)還是混合機(jī)取決于整個(gè)系統(tǒng)的需求。無論選擇哪種類型的狀態(tài)機(jī),充分掌握實(shí)現(xiàn)方案所需的工具和技巧,將確保您實(shí)現(xiàn)最佳解決方案。本文主要介紹如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

2013-03-29 15:02:57 14152

14152

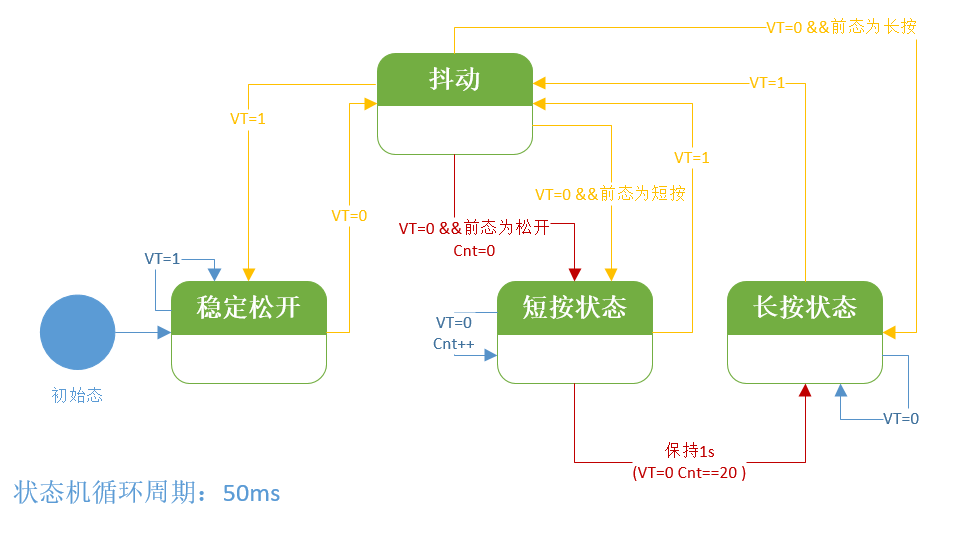

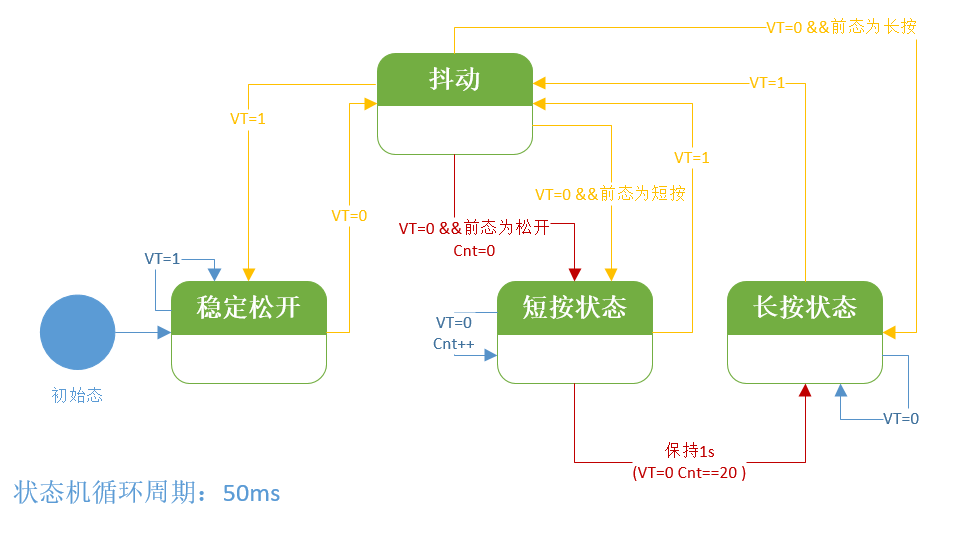

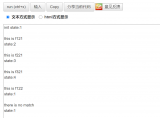

本篇介紹了嵌入式軟件開發(fā)中常用的狀態(tài)機(jī)編程實(shí)現(xiàn),并通過按鍵消抖實(shí)例,以常用的switch-case形式,實(shí)現(xiàn)了對(duì)應(yīng)的狀態(tài)機(jī)編程代碼實(shí)現(xiàn),并通過測(cè)試,串口打印對(duì)應(yīng)狀態(tài),分析狀態(tài)機(jī)的狀態(tài)跳轉(zhuǎn)過程。

2022-09-02 21:54:12 5846

5846

本篇在前兩篇按鍵狀態(tài)機(jī)的基礎(chǔ)上,繼續(xù)介紹增加按鍵的雙擊功能,并解決之前狀態(tài)存在的兩個(gè)問題,通過實(shí)測(cè)驗(yàn)證,演示短按、長(zhǎng)按、雙擊的使用效果。最后對(duì)代碼結(jié)構(gòu)進(jìn)行優(yōu)化,使其更符合實(shí)際開發(fā)應(yīng)用。

2022-09-04 17:05:11 3047

3047

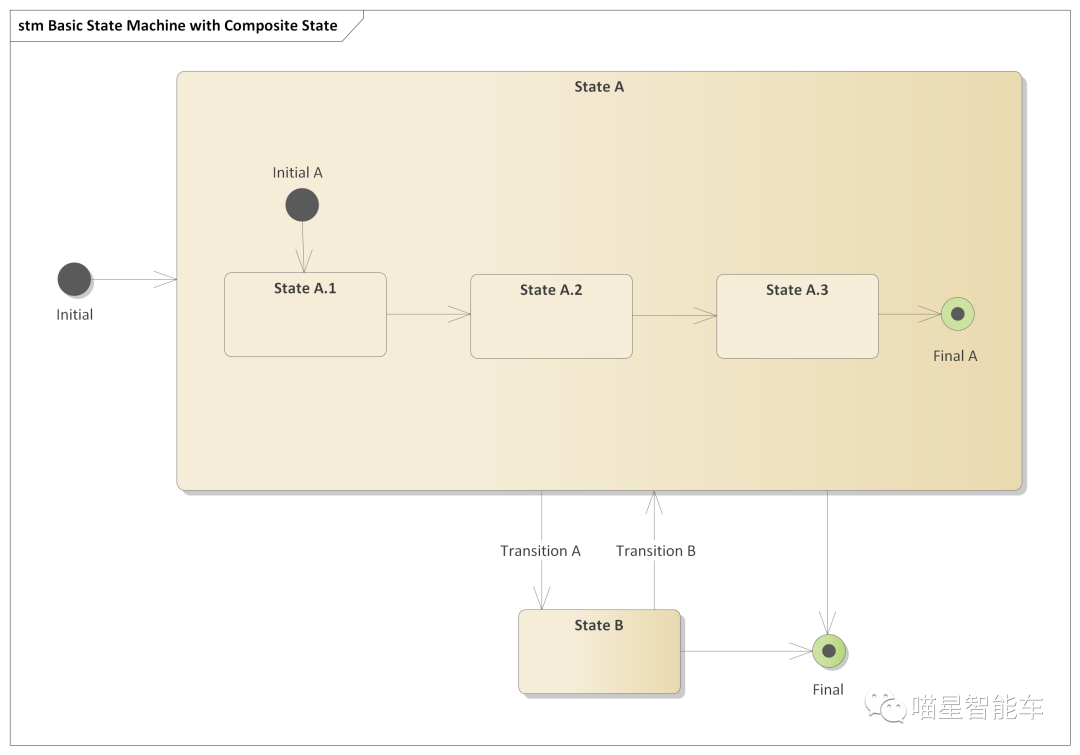

本編介紹了狀態(tài)機(jī)編程的第3種方法——面向?qū)ο蟮?b class="flag-6" style="color: red">狀態(tài)設(shè)計(jì)模式,通過C++的繼承特性,以及類指針,實(shí)現(xiàn)炸彈拆除小游戲中的狀態(tài)機(jī)功能。

2023-06-28 09:04:41 2914

2914

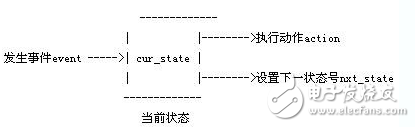

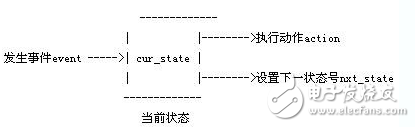

關(guān)于狀態(tài)機(jī),基礎(chǔ)的知識(shí)點(diǎn)可以自行理解。本文主要講解的是一個(gè)有限狀態(tài)機(jī)FSM通用的寫法,目的在于更好理解,移植,節(jié)省代碼閱讀與調(diào)試時(shí)間,體現(xiàn)出編程之美。

2023-09-13 09:28:42 1594

1594

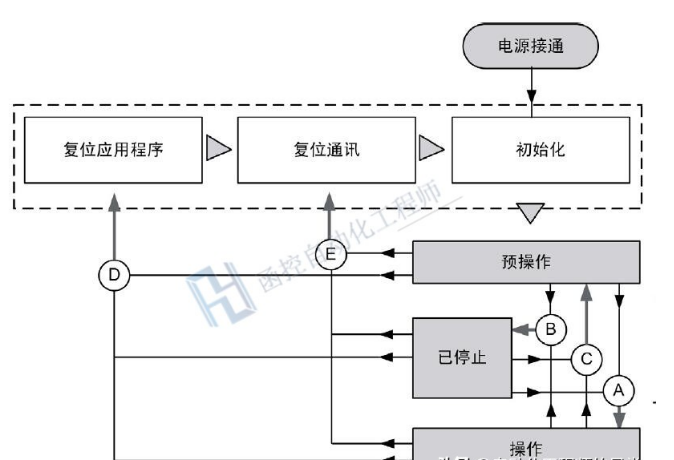

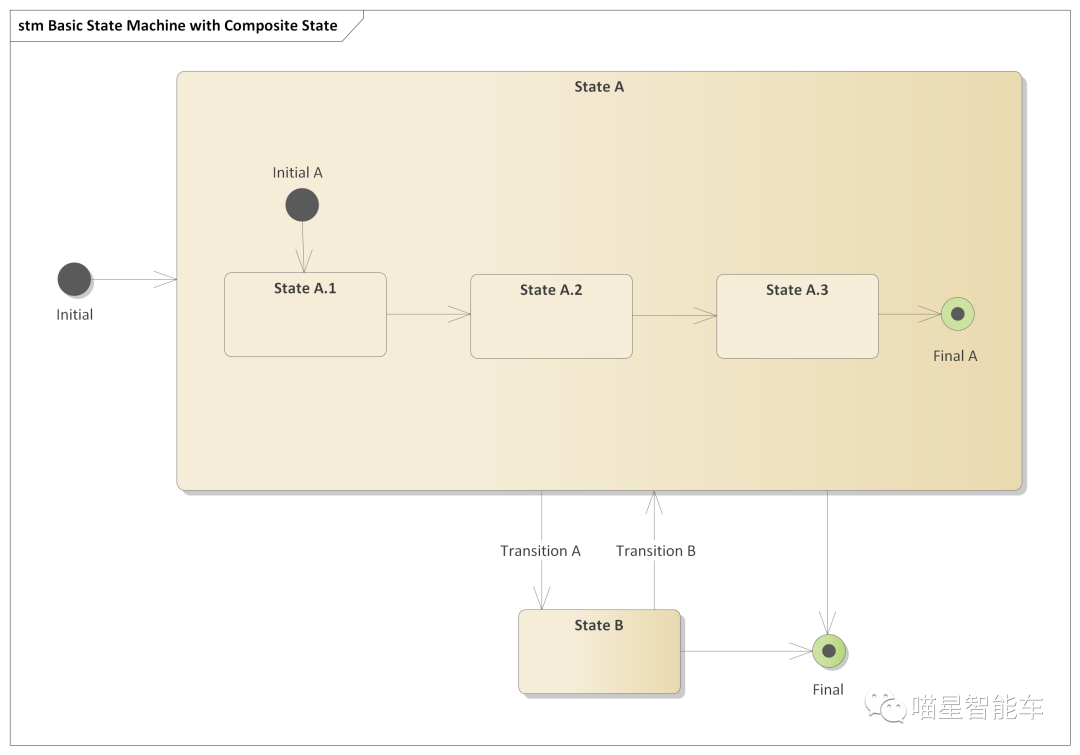

狀態(tài)機(jī)模塊在自動(dòng)駕駛系統(tǒng)中扮演著關(guān)鍵的角色,它負(fù)責(zé)管理和控制各個(gè)功能的狀態(tài)轉(zhuǎn)換和行為執(zhí)行。今天我們來聊聊如何設(shè)計(jì)自動(dòng)駕駛系統(tǒng)的狀態(tài)機(jī) 。

2023-09-19 15:07:25 4114

4114

狀態(tài)機(jī)建模是使用狀態(tài)圖和方程式的手段,創(chuàng)建基于混合信號(hào)的有限狀態(tài)機(jī)模型的一種建模工具。

2023-12-05 09:51:02 2888

2888

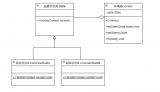

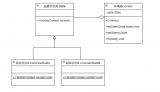

說起 Spring 狀態(tài)機(jī),大家很容易聯(lián)想到這個(gè)狀態(tài)機(jī)和設(shè)計(jì)模式中狀態(tài)模式的區(qū)別是啥呢?沒錯(cuò),Spring 狀態(tài)機(jī)就是狀態(tài)模式的一種實(shí)現(xiàn),在介紹 Spring 狀態(tài)機(jī)之前,讓我們來看看設(shè)計(jì)模式中的狀態(tài)模式。

2023-12-26 09:39:02 3071

3071

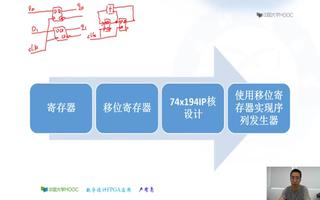

在verilog中狀態(tài)機(jī)的一種很常用的邏輯結(jié)構(gòu),學(xué)習(xí)和理解狀態(tài)機(jī)的運(yùn)行規(guī)律能夠幫助我們更好地書寫代碼,同時(shí)作為一種思想方法,在別的代碼設(shè)計(jì)中也會(huì)有所幫助。 一、簡(jiǎn)介 在使用過程中我們常說

2024-02-12 19:07:39 6009

6009

說起Spring狀態(tài)機(jī),大家很容易聯(lián)想到這個(gè)狀態(tài)機(jī)和設(shè)計(jì)模式中狀態(tài)模式的區(qū)別是啥呢?沒錯(cuò),Spring狀態(tài)機(jī)就是狀態(tài)模式的一種實(shí)現(xiàn),在介紹Spring狀態(tài)機(jī)之前,讓我們來看看設(shè)計(jì)模式中的狀態(tài)模式

2024-06-25 14:21:02 1580

1580

狀態(tài)機(jī)不穩(wěn)定,跑上幾十次就卡在某個(gè)狀態(tài)。改成三段式后,在RTL viewer看綜合后的電路,綜合成了狀態(tài)機(jī)(黃色那塊)。這時(shí)候程序運(yùn)行幾遍就會(huì)卡住。但是將CS賦值給led變量后,編譯后用

2016-08-06 17:20:59

狀態(tài)機(jī)可歸納為哪幾個(gè)要素?狀態(tài)機(jī)可分為哪幾種?什么是消息觸發(fā)類型的狀態(tài)機(jī)?

2021-04-19 06:02:21

狀態(tài)機(jī)編程基于狀態(tài)機(jī)的按鍵輸入軟件接口設(shè)計(jì)一般的教課書中給出的按鍵輸入軟件接口程序通常非常簡(jiǎn)單,在程序中一旦檢測(cè)到按鍵輸入口為低電平時(shí)(圖9-2),便采用(調(diào)用)軟件延時(shí)程序延時(shí)10ms。然后再

2008-07-10 18:00:24

今天大師匈聊一下策略狀態(tài)機(jī)標(biāo)準(zhǔn)內(nèi)的一些東西,然后順便放一張圖,協(xié)議分析軟件抓到的數(shù)據(jù)交互過程。一、協(xié)議交互過程(溝通電源)這個(gè)是我們常用的分析協(xié)議的一個(gè)工具,使用這個(gè)抓到的數(shù)據(jù)包。大師匈截圖了部分

2021-12-31 07:18:37

Mealy狀態(tài)機(jī)而言,由于其任何時(shí)刻的輸出與輸入有關(guān),這種情況就更常見了.2 狀態(tài)機(jī)設(shè)計(jì)方案比較2.1 采用枚舉數(shù)據(jù)類型定義狀態(tài)值在設(shè)計(jì)中定義狀態(tài)機(jī)的狀態(tài)值為枚舉數(shù)據(jù)類型,綜合器一般把它表示為二進(jìn)制數(shù)的序列

2012-01-12 10:48:26

波形仿真時(shí)verilog 寫的狀態(tài)機(jī)被綜合掉,編譯沒有錯(cuò)誤,狀態(tài)轉(zhuǎn)移也沒錯(cuò),什么原因可能導(dǎo)致這種問題呢。

2017-10-05 11:31:26

最近在CPLD里面做了一個(gè)4通道的模塊,每個(gè)模塊內(nèi)都有一個(gè)狀態(tài)機(jī),開始我是用的一段式狀態(tài)機(jī)寫發(fā),資源不夠,然后我將狀態(tài)機(jī)的寫法改為3段式,(將狀態(tài)轉(zhuǎn)換一段,輸出一段)發(fā)現(xiàn)資源降低了很多,問下,一段和三段式的狀態(tài)機(jī)為什么對(duì)占用資源會(huì)有影響?或者談?wù)勔欢魏腿蔚?b class="flag-6" style="color: red">綜合情況?

2015-01-21 14:07:40

一. 什么是狀態(tài)機(jī)我們以生活中的小區(qū)的停車系統(tǒng)為例:停車桿一般沒車的是不動(dòng)的(初態(tài)),有車來的時(shí)候需要抬桿(狀態(tài)1),車通過需要放桿(狀態(tài)2),如果在放桿的過程中突然有車,又需要抬桿(狀態(tài)3

2022-01-06 08:01:00

目錄1 前言2 狀態(tài)機(jī)2.1 什么是狀態(tài)機(jī)2.2 狀態(tài)機(jī)的概念2.3 使用狀態(tài)機(jī)寫鍵盤的思路3 代碼實(shí)例3.1 使用軟件3.2 protues電路圖3.2 狀態(tài)機(jī)部分程序3.3 Keil工程文件

2022-01-24 06:23:02

什么是狀態(tài)機(jī)?狀態(tài)機(jī)是如何編程的?

2021-10-20 07:43:43

從事邏輯設(shè)計(jì)的小伙伴對(duì)狀態(tài)機(jī)這個(gè)詞并不陌生,什么兩段、三段狀態(tài)機(jī)耳熟能詳,摩爾、米利狀態(tài)機(jī)型倒背如流。然而不得不承認(rèn)的是讀別人的RTL代碼真的是一件痛苦的事情,那狀態(tài)機(jī)可否更優(yōu)雅的呈現(xiàn)呢?狀態(tài)機(jī)那些

2022-07-13 14:56:24

一篇經(jīng)典文獻(xiàn),詳細(xì)講解了一段、兩段、三段式狀態(tài)機(jī)的實(shí)現(xiàn),效率、優(yōu)缺點(diǎn)。看完后相信會(huì)對(duì)狀態(tài)機(jī)有一個(gè)詳細(xì)的了解。 狀態(tài)機(jī)是邏輯設(shè)計(jì)的重要內(nèi)容,狀態(tài)機(jī)的設(shè)計(jì)水平直接反應(yīng)工程師的邏輯功底,所以許 多公司

2011-10-24 11:43:11

圖示的狀態(tài)機(jī)中設(shè)計(jì)了一個(gè)獨(dú)立的Update狀態(tài)用于更新UI界面的文本顯示為什么不直接在每個(gè)狀態(tài)動(dòng)作分支直接將更新的文本直接輸出到顯示控件?或者說圖示的編程方式相較于上述思路而言有什么好處?萌新求教

2018-07-19 09:40:11

利用 VHDL 設(shè)計(jì)的許多實(shí)用邏輯系統(tǒng)中,有許多是可以利用有限狀態(tài)機(jī)的設(shè)計(jì)方案來描述和實(shí)現(xiàn)的。無論與基于 VHDL的其它設(shè)計(jì)方案相比,還是與可完成相似功能的 CPU 相比,狀

2008-06-04 10:33:10 75

75 狀態(tài)機(jī)實(shí)例(VHDL源代碼):

2009-05-27 10:27:58 59

59 如何寫好狀態(tài)機(jī):狀態(tài)機(jī)是邏輯設(shè)計(jì)的重要內(nèi)容,狀態(tài)機(jī)的設(shè)計(jì)水平直接反應(yīng)工程師的邏輯功底,所以許多公司的硬件和邏輯工程師面試中,狀態(tài)機(jī)設(shè)計(jì)幾乎是必選題目。本章在引入

2009-06-14 19:24:49 98

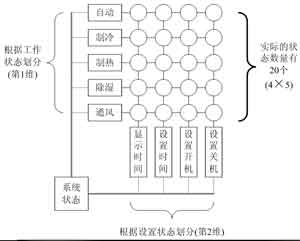

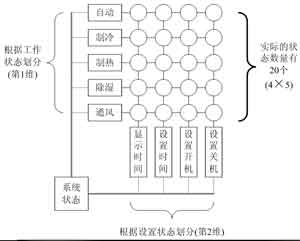

98 通過分析工控系統(tǒng)的特性,提出采用狀態(tài)機(jī)的思想進(jìn)行工控軟件設(shè)計(jì)。詳細(xì)論述了高速狀態(tài)機(jī)的錯(cuò)步問題以及控制層中狀態(tài)機(jī)的狀態(tài)劃分問題。結(jié)合具體的應(yīng)用實(shí)例,給出了基于狀

2009-08-10 14:26:08 30

30 狀態(tài)機(jī)思路在單片機(jī)程序設(shè)計(jì)中的應(yīng)用

狀態(tài)機(jī)的概念

狀態(tài)機(jī)是軟件編程中的一個(gè)重要概念。比這個(gè)概念更重要的是對(duì)

2009-03-18 15:00:02 1523

1523

狀態(tài)機(jī)舉例

你可以指定狀態(tài)寄存器和狀態(tài)機(jī)的狀態(tài)。以下是一個(gè)有四種狀態(tài)的普通狀態(tài)機(jī)。 // These are the symbolic names for states// 定義狀態(tài)的符號(hào)名稱parameter [1

2009-03-28 15:18:28 1183

1183 有許多可綜合狀態(tài)機(jī)的Verilog代碼描述風(fēng)格,不同代碼描述風(fēng)格經(jīng)綜合后得到電路的物理實(shí)現(xiàn)在速度和面積上有很大差別。優(yōu)秀的代碼描述應(yīng)當(dāng)易于修改、易于編寫和理解,有助于仿真和調(diào)

2011-12-24 00:52:00 30

30 狀態(tài)機(jī)代碼生成工具狀態(tài)機(jī)代碼生成工具狀態(tài)機(jī)代碼生成工具狀態(tài)機(jī)代碼生成工具

2015-11-19 15:12:16 9

9 狀態(tài)機(jī)原理及用法狀態(tài)機(jī)原理及用法狀態(tài)機(jī)原理及用法

2016-03-15 15:25:49 0

0 本文詳 細(xì)論述了高速狀態(tài)機(jī)的錯(cuò)步問題以及控制層中狀態(tài)機(jī)的狀態(tài)劃分問題,結(jié)合具體的應(yīng)用實(shí)例,給出了基于狀態(tài)機(jī)的實(shí)現(xiàn)方法。

2016-03-22 15:48:30 3

3 文中提出了 在嵌入式軟件中把狀態(tài)機(jī)作為一個(gè)獨(dú)立模塊從控制模塊中抽象出來的思想 , 描述了 抽象出來的狀態(tài)機(jī)模塊 。 并介紹了 如何將這種狀態(tài)機(jī)抽象模塊應(yīng)用到實(shí)際項(xiàng)目中 。

2016-03-22 15:47:10 1

1 本文通過舉例 利用VHDL 語言描述了不同模式的有限狀態(tài)機(jī) 分析了有限狀態(tài)機(jī)在 PLD 中綜合的特點(diǎn) 。

2016-03-22 15:41:36 3

3 本文提出一種優(yōu)秀 、高效的 Verilog HDL 描述方式來進(jìn)行有限狀態(tài)機(jī)設(shè)計(jì) 介紹了 有限狀態(tài)機(jī)的建模原則 并通過一個(gè)可綜合的實(shí)例 驗(yàn)證了 該方法設(shè)計(jì)的有限狀態(tài)機(jī)在面積和功耗上的優(yōu)勢(shì)。

2016-03-22 15:19:41 1

1 同步狀態(tài)機(jī)的簡(jiǎn)單介紹與入門!非常適合入門學(xué)習(xí)用。

2016-05-06 15:32:57 3

3 EDA的有限狀態(tài)機(jī),廣義而言是指只要涉及觸發(fā)器的電路,無論電路大小都可以歸結(jié)為狀態(tài)機(jī)。有限狀態(tài)機(jī)設(shè)計(jì)在學(xué)習(xí)EDA時(shí)是很重要的一章。

2016-06-08 16:46:10 3

3 狀態(tài)機(jī)VHDL程序,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 15:51:00 5

5 基于有限狀態(tài)機(jī)的五橋臂逆變器改進(jìn)調(diào)制策略_梅楊

2017-01-08 13:58:48 0

0 HDL代碼設(shè)計(jì)中重要的內(nèi)容之一就是設(shè)計(jì)程序的狀態(tài)機(jī)FSM,狀態(tài)轉(zhuǎn)換控制著整個(gè)程序的流程,為了理解程序,我們經(jīng)常需要把狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換圖畫出來,這樣看起來很直觀,但是,有沒有辦法自動(dòng)生成狀態(tài)轉(zhuǎn)換圖呢?

2017-02-10 15:39:49 15910

15910

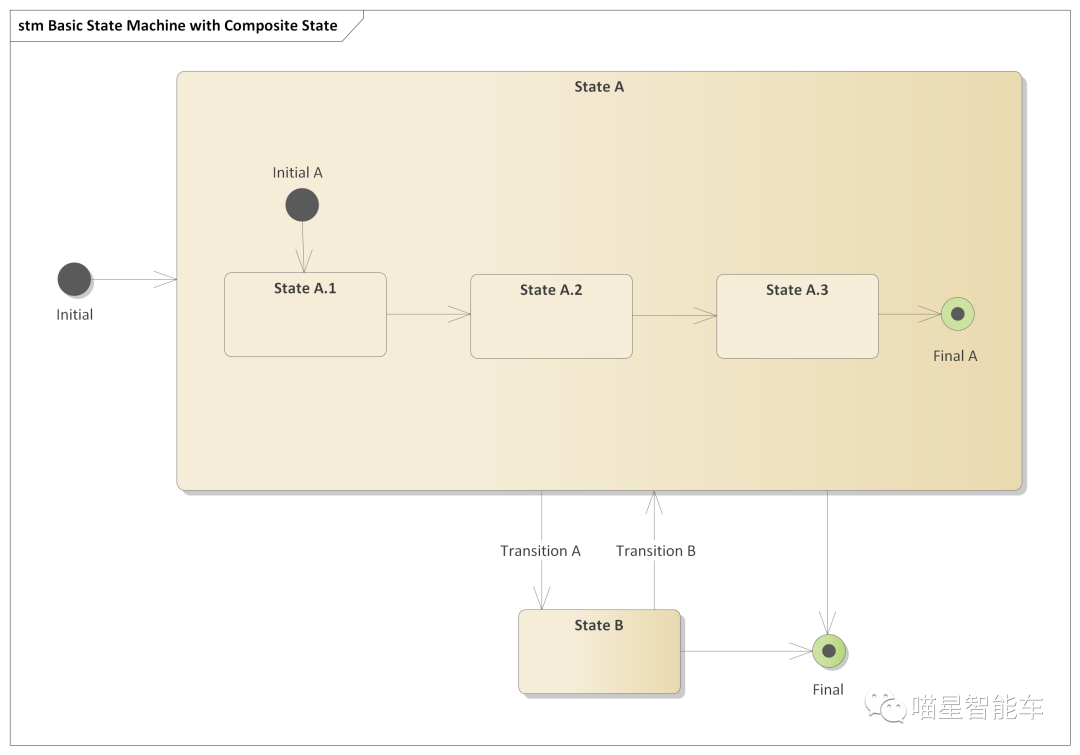

練習(xí)九.利用狀態(tài)機(jī)的嵌套實(shí)現(xiàn)層次結(jié)構(gòu)化設(shè)計(jì)目的:1.運(yùn)用主狀態(tài)機(jī)與子狀態(tài)機(jī)產(chǎn)生層次化的邏輯設(shè)計(jì);

2017-02-11 05:52:50 3660

3660

有限狀態(tài)機(jī)(FSM)是一種常見的電路,由時(shí)序電路和組合電路組成。設(shè)計(jì)有限狀態(tài)機(jī)的第一步是確定采用Moore狀態(tài)機(jī)還是采用Mealy狀態(tài)機(jī)。

2017-02-11 13:51:40 4710

4710

在FPGA/CPLD設(shè)計(jì)中頻繁使用的狀態(tài)機(jī),常出現(xiàn)一些穩(wěn)定性問題,本文提出了一些解決方法,實(shí)驗(yàn)表明該方法有效地提高了綜合效率. 隨著大規(guī)模和超大規(guī)模FPGA/CPLD器件的誕生和發(fā)展,以HDL(硬件

2017-11-24 20:59:08 3889

3889

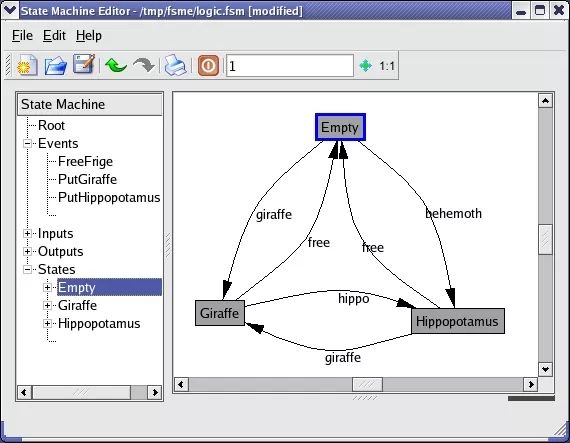

組成部分。 不過,狀態(tài)機(jī)理論的發(fā)展卻很緩慢。在眾多原因中,狀態(tài)機(jī)只是做為編程的實(shí)現(xiàn)工具而不是設(shè)計(jì)工具是一個(gè)最重要的原因。 本文的重點(diǎn)就在于,怎樣利用狀態(tài)機(jī)原理進(jìn)行程序設(shè)計(jì)。本文會(huì)先給出普通的、一個(gè)平面上的FSM(有限狀態(tài)機(jī))的概念和實(shí)例,并指出

2017-12-02 15:03:07 732

732 本文主要介紹了是如何利用74LS161實(shí)現(xiàn)復(fù)雜狀態(tài)機(jī)的。時(shí)序邏輯電路的數(shù)學(xué)模型是有限狀態(tài)機(jī)。有限狀態(tài)機(jī)它把復(fù)雜的控制邏輯分解成有限個(gè)穩(wěn)定狀態(tài),在每個(gè)狀態(tài)上判斷事件,變連續(xù)處理為離散數(shù)字處理,符合計(jì)算機(jī)的工作特點(diǎn)。本文主要討論使用MSI同步計(jì)數(shù)器74LS161進(jìn)行復(fù)雜狀態(tài)機(jī)的設(shè)計(jì)。

2018-01-18 09:00:02 11155

11155

狀態(tài)機(jī)最主要的特點(diǎn)就是靈活性,這個(gè)優(yōu)勢(shì)在程序后期的維護(hù)上更會(huì)顯示出來,本集中工程師將展現(xiàn)出狀態(tài)機(jī)是如何輕松對(duì)程序進(jìn)行靈活修改,從而滿足日益復(fù)雜的開發(fā)要求。

2018-06-14 03:19:00 3690

3690

如何使用QII狀態(tài)機(jī)向?qū)?chuàng)建一個(gè)狀態(tài)機(jī)

2018-06-20 00:11:00 4892

4892

有限狀態(tài)機(jī)(Finite State Machine, FSM),根據(jù)狀態(tài)機(jī)的輸出是否與輸入有關(guān),可分為Moore型狀態(tài)機(jī)和Mealy型狀態(tài)機(jī)。Moore型狀態(tài)機(jī)輸出僅僅與現(xiàn)態(tài)有關(guān)和Mealy型

2018-06-25 08:42:00 4338

4338 本篇文章包括狀態(tài)機(jī)的基本概述以及通過簡(jiǎn)單的實(shí)例理解狀態(tài)機(jī)

2019-01-02 18:03:31 11179

11179

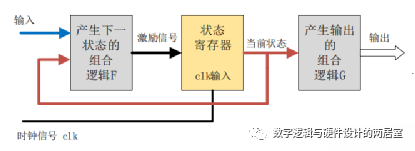

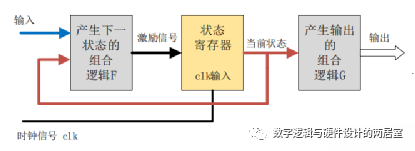

狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號(hào)按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號(hào)動(dòng)作,完成特定操作的控制中心。狀態(tài)機(jī)分為摩爾(Moore)型狀態(tài)機(jī)和米莉(Mealy)型狀態(tài)機(jī)。

2019-09-19 07:00:00 2999

2999

狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號(hào)按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號(hào)動(dòng)作,完成特定操作的控制中心。狀態(tài)機(jī)分為摩爾(Moore)型狀態(tài)機(jī)和米莉(Mealy)型狀態(tài)機(jī)。

2019-10-09 07:07:00 4101

4101 狀態(tài)機(jī)有三種描述方式:一段式狀態(tài)機(jī)、兩段式狀態(tài)機(jī)、三段式狀態(tài)機(jī)。下面就用一個(gè)小例子來看看三種方式是如何實(shí)現(xiàn)的。

2019-08-29 06:09:00 3376

3376

狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號(hào)按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號(hào)動(dòng)作、完成特定操作的控制中心。

2019-12-04 07:03:00 3640

3640

狀態(tài)機(jī)可歸納為4個(gè)要素,即現(xiàn)態(tài)、條件、動(dòng)作、次態(tài)。這樣的歸納,主要是出于對(duì)狀態(tài)機(jī)的內(nèi)在因果關(guān)系的考慮。“現(xiàn)態(tài)”和“條件”是因,“動(dòng)作”和“次態(tài)”是果。

2019-10-09 07:04:00 2633

2633 狀態(tài)機(jī)由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號(hào)按照預(yù)先設(shè)定的狀態(tài)進(jìn)行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號(hào)動(dòng)作,完成特定操作的控制中心。狀態(tài)機(jī)分為摩爾(Moore)型狀態(tài)機(jī)和米莉(Mealy)型狀態(tài)機(jī)。

2019-05-28 07:03:49 3390

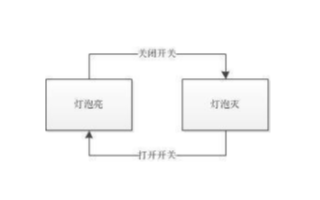

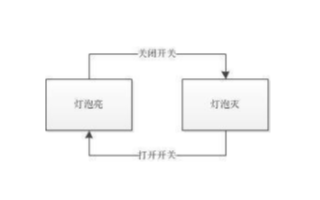

3390 在PLC程序的編寫過程中,可以使用狀態(tài)機(jī)的控制思路,將一些復(fù)雜的控制過程使用狀態(tài)機(jī)的方法處理。這里簡(jiǎn)單給大家介紹一下什么是狀態(tài)機(jī)?如下圖所示,為一個(gè)狀態(tài)機(jī)的狀態(tài)圖。

2020-09-10 14:44:18 5185

5185

狀態(tài)機(jī) 1、狀態(tài)機(jī)是許多數(shù)字系統(tǒng)的核心部件,是一類重要的時(shí)序邏輯電路。通常包括三個(gè)部分:一是下一個(gè)狀態(tài)的邏輯電路,二是存儲(chǔ)狀態(tài)機(jī)當(dāng)前狀態(tài)的時(shí)序邏輯電路,三是輸出組合邏輯電路。 2、根據(jù)狀態(tài)機(jī)的輸出

2020-11-16 17:39:00 27908

27908 之前寫過一篇狀態(tài)機(jī)的實(shí)用文章,很多朋友說有幾個(gè)地方有點(diǎn)難度不易理解,今天給大家換種簡(jiǎn)單寫法,使用函數(shù)指針的方法實(shí)現(xiàn)狀態(tài)機(jī)。 狀態(tài)機(jī)簡(jiǎn)介 有限狀態(tài)機(jī)FSM是有限個(gè)狀態(tài)及在這些狀態(tài)之間的轉(zhuǎn)移和動(dòng)作等行為

2020-10-19 09:36:53 2958

2958

說到單片機(jī)編程,不得不說到狀態(tài)機(jī),狀態(tài)機(jī)做為軟件編程的主要架構(gòu)已經(jīng)在各種語言中應(yīng)用,當(dāng)然包括C語言,在一個(gè)思路清晰而且高效的程序中,必然有狀態(tài)機(jī)的身影浮現(xiàn)。靈活的應(yīng)用狀態(tài)機(jī)不僅是程序更高效,而且

2020-10-20 17:27:47 5830

5830 狀態(tài)機(jī)在實(shí)際工作開發(fā)中應(yīng)用非常廣泛,在剛進(jìn)入公司的時(shí)候,根據(jù)公司產(chǎn)品做流程圖的時(shí)候,發(fā)現(xiàn)自己經(jīng)常會(huì)漏了這樣或那樣的狀態(tài),導(dǎo)致整體流程會(huì)有問題,后來知道了狀態(tài)機(jī)這樣的東西,發(fā)現(xiàn)用這幅圖就可以很清晰的表達(dá)整個(gè)狀態(tài)的流轉(zhuǎn)。

2020-10-25 11:31:29 4600

4600

本文目錄 前言 狀態(tài)機(jī)簡(jiǎn)介 狀態(tài)機(jī)分類 Mealy 型狀態(tài)機(jī) Moore 型狀態(tài)機(jī) 狀態(tài)機(jī)描述 一段式狀態(tài)機(jī) 二段式狀態(tài)機(jī) 三段式狀態(tài)機(jī) 狀態(tài)機(jī)優(yōu)缺點(diǎn) 總結(jié) 擴(kuò)展-四段式狀態(tài)機(jī) 01. 前言 狀態(tài)機(jī)

2020-11-05 17:58:47 8700

8700

今天的文章只是帶大家入門和了解一下狀態(tài)機(jī),等你真正在工作當(dāng)中有遇到這個(gè)狀態(tài)機(jī)作為開發(fā)需要的話,你再去深入研究。

2020-12-24 18:06:07 2577

2577 狀態(tài)機(jī)是邏輯單元、存儲(chǔ)器單元和反饋的組合。狀態(tài)機(jī)的輸入與狀態(tài)機(jī)的當(dāng)前狀態(tài)組合在一起,確定下一個(gè)狀態(tài)。當(dāng)出現(xiàn)狀態(tài)時(shí)鐘時(shí),下一個(gè)狀態(tài)成為當(dāng)前狀態(tài),狀態(tài)機(jī)的輸出由當(dāng)前狀態(tài)決定。

2021-03-30 15:58:14 7

7 Synplify的優(yōu)勢(shì)之一是有限狀態(tài)機(jī)編譯器。 這是一個(gè)強(qiáng)大的功能,不僅具有自動(dòng)檢測(cè)狀態(tài)機(jī)中的狀態(tài)的能力源代碼,并使用順序編碼,灰色編碼或一鍵編碼實(shí)現(xiàn)它們。但也要進(jìn)行可達(dá)性分析,以確定所有可能的狀態(tài)達(dá)到并優(yōu)化掉所有無法達(dá)到的狀態(tài)和轉(zhuǎn)換邏輯。因此,產(chǎn)生狀態(tài)機(jī)的高度優(yōu)化的最終實(shí)現(xiàn)。

2021-04-07 09:20:51 12

12 “本文主要分享了在Verilog設(shè)計(jì)過程中狀態(tài)機(jī)的一些設(shè)計(jì)方法。 關(guān)于狀態(tài)機(jī) 狀態(tài)機(jī)本質(zhì)是對(duì)具有邏輯順序或時(shí)序順序事件的一種描述方法,也就是說具有邏輯順序和時(shí)序規(guī)律的事情都適用狀態(tài)機(jī)描述。狀態(tài)機(jī)

2021-06-25 11:04:43 3362

3362 玩單片機(jī)還可以,各個(gè)外設(shè)也都會(huì)驅(qū)動(dòng),但是如果讓你完整的寫一套代碼時(shí),卻無邏輯與框架可言。這說明編程還處于比較低的水平,你需要學(xué)會(huì)一種好的編程框架或者一種編程思想!比如模塊化編程、狀態(tài)機(jī)編程、分層思想

2021-07-27 11:23:22 21875

21875

? 一、介紹 EFSM(event finite state machine,事件驅(qū)動(dòng)型有限狀態(tài)機(jī)),是一個(gè)基于事件驅(qū)動(dòng)的有限狀態(tài)機(jī),主要應(yīng)用于嵌入式設(shè)備的軟件系統(tǒng)中。 EFSM的設(shè)計(jì)原則是:簡(jiǎn)單

2021-11-16 15:29:10 2912

2912 目錄1 前言2 狀態(tài)機(jī)2.1 什么是狀態(tài)機(jī)2.2 狀態(tài)機(jī)的概念2.3 使用狀態(tài)機(jī)寫鍵盤的思路3 代碼實(shí)例3.1 使用軟件3.2 protues電路圖3.2 狀態(tài)機(jī)部分程序3.3 Keil工程文件

2021-11-29 13:21:08 4

4 以前寫狀態(tài)機(jī),比較常用的方式是用 if-else 或 switch-case,高級(jí)的一點(diǎn)是函數(shù)指針列表。最近,看了一文章《c語言設(shè)計(jì)模式–狀態(tài)模式(狀態(tài)機(jī))》(來源:embed linux

2021-12-16 16:53:04 9

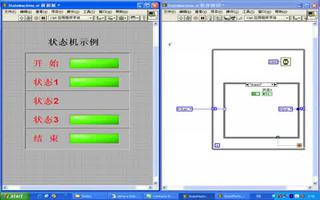

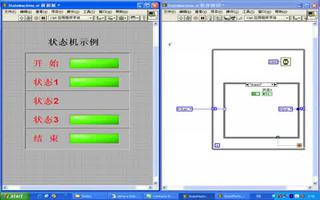

9 LABVIEW的狀態(tài)機(jī)實(shí)現(xiàn)資料合集

2022-01-04 11:18:40 51

51 有限狀態(tài)機(jī)又稱有限狀態(tài)自動(dòng)機(jī),簡(jiǎn)稱狀態(tài)機(jī),是表示有限個(gè)狀態(tài)以及在這些狀態(tài)之間的轉(zhuǎn)移和動(dòng)作等行為的數(shù)學(xué)計(jì)算模型,用英文縮寫也被簡(jiǎn)...

2022-02-07 11:23:28 4

4 說到單片機(jī)編程,不得不說到狀態(tài)機(jī),狀態(tài)機(jī)做為軟件編程的主要架構(gòu)已經(jīng)在各種語言中應(yīng)用,當(dāng)然包括C語言,在一個(gè)思路清晰而且高效的程序中,必然有狀態(tài)機(jī)的身影浮現(xiàn)。靈活的應(yīng)用狀態(tài)機(jī)不僅是程序更高效,而且

2022-02-10 10:44:57 12

12 本篇實(shí)現(xiàn)了一款全自動(dòng)洗衣機(jī)的基礎(chǔ)洗衣控制流程,可實(shí)現(xiàn)不同水位與清洗次數(shù)的設(shè)置,以及任務(wù)的暫停與繼續(xù)。此外,通過對(duì)之前按鍵狀態(tài)機(jī)的進(jìn)一步優(yōu)化修改,實(shí)現(xiàn)了按鍵狀態(tài)機(jī)的復(fù)用,實(shí)現(xiàn)多個(gè)按鍵的檢測(cè)。下篇文章將進(jìn)一步進(jìn)行功能優(yōu)化,添加OLED小屏幕實(shí)現(xiàn)不同狀態(tài)的可視化展示。

2022-09-06 08:47:08 4294

4294

有限自動(dòng)機(jī)(Finite Automata Machine)是計(jì)算機(jī)科學(xué)的重要基石,它在軟件開發(fā)領(lǐng)域內(nèi)通常被稱作有限狀態(tài)機(jī)(Finite State Machine),是一種應(yīng)用非常廣泛的軟件設(shè)計(jì)

2022-09-14 10:55:27 2164

2164 labview狀態(tài)機(jī)

2022-10-31 15:50:26 20

20 狀態(tài)機(jī)在嵌入式軟件中隨處可見,可能你會(huì)說狀態(tài)機(jī)有什么難的,不就是 switch 嗎?

2022-11-02 09:04:13 1641

1641 EFSM(event finite state machine,事件驅(qū)動(dòng)型有限狀態(tài)機(jī)),是一個(gè)基于事件驅(qū)動(dòng)的有限狀態(tài)機(jī),主要應(yīng)用于嵌入式設(shè)備的軟件系統(tǒng)中。

2023-02-11 10:17:15 1589

1589 今天還是更新狀態(tài)機(jī),狀態(tài)機(jī)基本是整個(gè)HDL中的核心,合理、高效地使用狀態(tài)機(jī),是數(shù)字電路中的重要技能。

2023-02-12 10:21:05 1631

1631 自己寫的按鍵狀態(tài)機(jī),需要的時(shí)候根據(jù)情況修改一下

2023-03-27 10:42:41 8

8 嵌入式狀態(tài)機(jī)是一種常用的軟件設(shè)計(jì)模式,它能夠提高代碼的可讀性和可維護(hù)性。狀態(tài)機(jī)是一個(gè)抽象的概念,它描述了一個(gè)系統(tǒng)或者組件的不同狀態(tài)以及在不同狀態(tài)下如何響應(yīng)輸入和事件。狀態(tài)機(jī)可以應(yīng)用于各種領(lǐng)域,比如通信協(xié)議、嵌入式系統(tǒng)、控制系統(tǒng)等。

2023-04-14 11:55:10 2742

2742 有限狀態(tài)機(jī)(Finite-State Machine,F(xiàn)SM),簡(jiǎn)稱狀態(tài)機(jī),是表示有限個(gè)狀態(tài)以及在這些狀態(tài)之間的轉(zhuǎn)移和動(dòng)作等行為的數(shù)學(xué)模型。

2023-06-01 15:23:39 2697

2697

狀態(tài)機(jī)往往是FPGA 開發(fā)的主力。選擇合適的架構(gòu)和實(shí)現(xiàn)方法將確保您獲得一款最佳解決方案。 FPGA 常常用于執(zhí)行基于序列和控制的行動(dòng), 比如實(shí)現(xiàn)一個(gè)簡(jiǎn)單的通信協(xié)議。對(duì)于設(shè)計(jì)人員來說,滿足這些行動(dòng)

2023-07-18 16:05:01 1984

1984

狀態(tài)機(jī)模塊的主要作用是跟蹤系統(tǒng)的當(dāng)前狀態(tài),并根據(jù)特定的事件和條件進(jìn)行狀態(tài)轉(zhuǎn)換。

2023-07-21 14:44:58 1611

1611

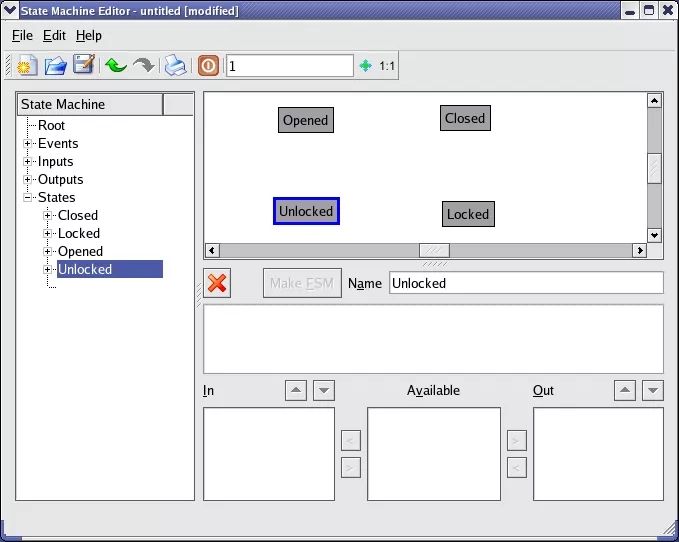

為實(shí)用的軟件系統(tǒng)編寫狀態(tài)機(jī)并不是一件十分輕松的事情,特別是當(dāng)狀態(tài)機(jī)本身比較復(fù)雜的時(shí)候尤其如此,許多有過類似經(jīng)歷的程序員往往將其形容為“毫無創(chuàng)意”的過程,因?yàn)樗麄冃枰獙⒋罅康臅r(shí)間與精力傾注在如何管理

2023-09-13 16:45:45 2376

2376

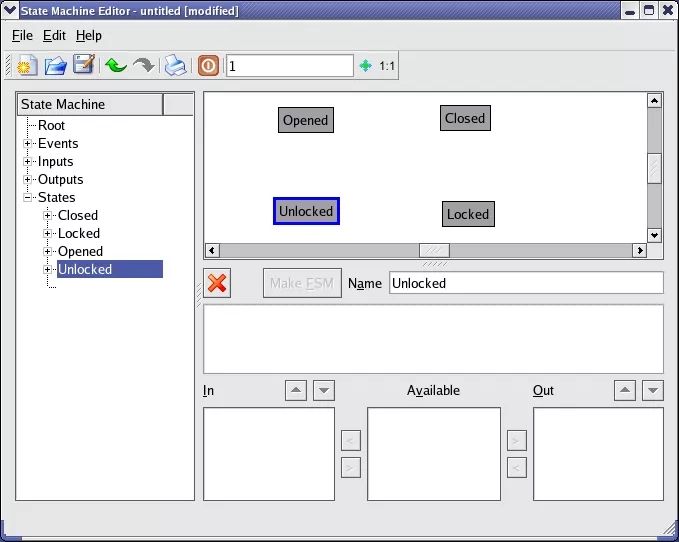

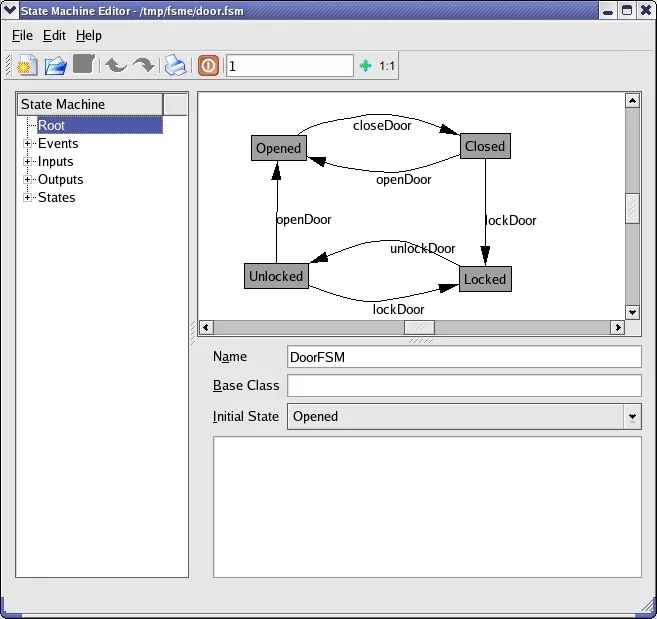

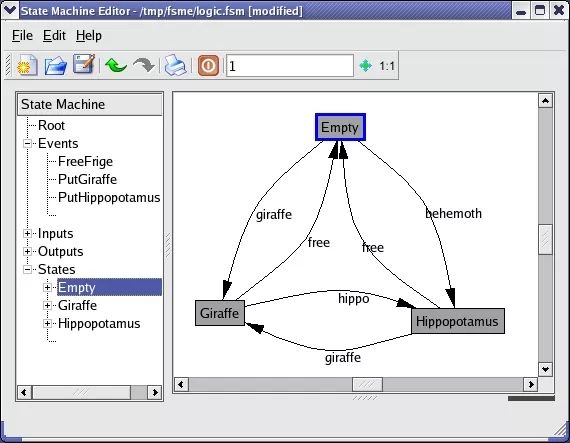

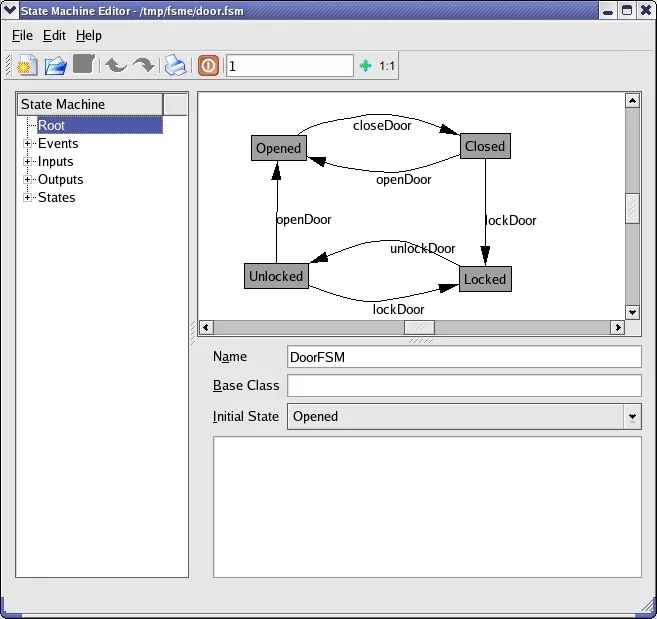

首先運(yùn)行fsme命令來啟動(dòng)狀態(tài)機(jī)編輯器,然后單擊工具欄上的“New”按鈕來創(chuàng)建一個(gè)新的狀態(tài)機(jī)。FSME中用于構(gòu)建狀態(tài)機(jī)的基本元素一共有五種:事件(Event)、輸入(Input)、輸出(Output

2023-09-13 16:50:03 2050

2050

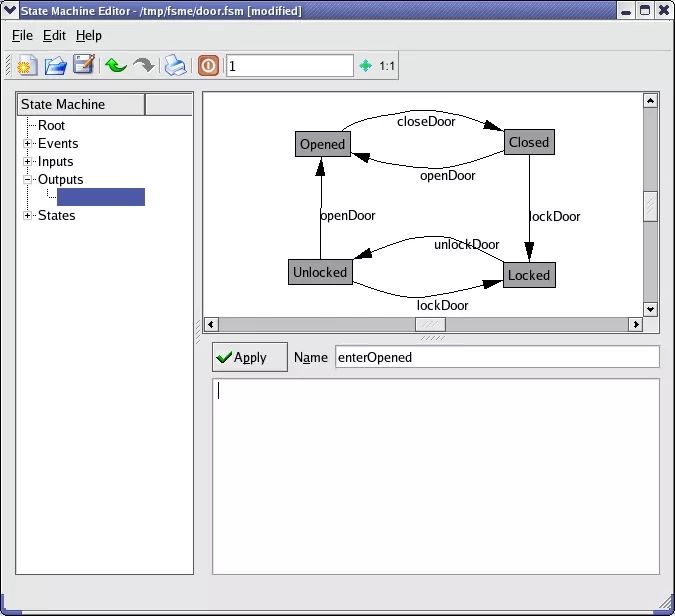

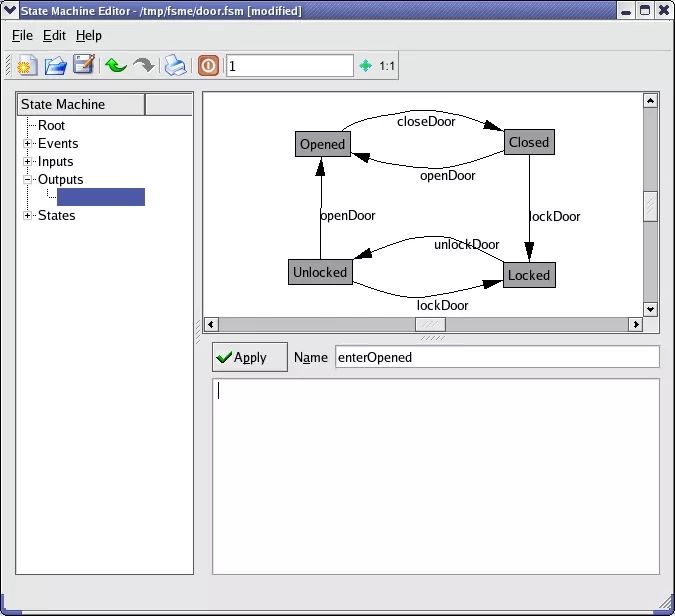

生成狀態(tài)機(jī)框架 使用FSME不僅能夠進(jìn)行可視化的狀態(tài)機(jī)建模,更重要的是它還可以根據(jù)得到的模型自動(dòng)生成用C++或者Python實(shí)現(xiàn)的狀態(tài)機(jī)框架。首先在FSME界面左邊的樹形列表中選擇"Root"項(xiàng)

2023-09-13 16:54:15 1555

1555

定制狀態(tài)機(jī) 目前得到的狀態(tài)機(jī)已經(jīng)能夠響應(yīng)來自外部的各種事件,并適當(dāng)?shù)卣{(diào)整自己當(dāng)前所處的狀態(tài),也就是說已經(jīng)實(shí)現(xiàn)了狀態(tài)機(jī)引擎的功能,接下來要做的就是根據(jù)應(yīng)用的具體需求來進(jìn)行定制,為狀態(tài)機(jī)加入與軟件系統(tǒng)

2023-09-13 16:57:37 2288

2288

如果一個(gè)對(duì)象(系統(tǒng)或機(jī)器),由若干個(gè)狀態(tài)構(gòu)成,在某種條件下觸發(fā)這些狀態(tài),會(huì)發(fā)生狀態(tài)相互轉(zhuǎn)移的事件,那么此對(duì)象稱之為狀態(tài)機(jī)。

2023-09-17 16:42:34 3533

3533 有限狀態(tài)機(jī)分割設(shè)計(jì),其實(shí)質(zhì)就是一個(gè)狀態(tài)機(jī)分割成多個(gè)狀態(tài)機(jī)

2023-10-09 10:47:06 1173

1173 狀態(tài)機(jī),又稱有限狀態(tài)機(jī)(Finite State Machine,F(xiàn)SM)或米利狀態(tài)機(jī)(Mealy Machine),是一種描述系統(tǒng)狀態(tài)變化的模型。在芯片設(shè)計(jì)中,狀態(tài)機(jī)被廣泛應(yīng)用于各種場(chǎng)景,如CPU指令集、內(nèi)存控制器、總線控制器等。

2023-10-19 10:27:55 12740

12740 狀態(tài)機(jī)卡住的場(chǎng)景——通過狀態(tài)跳轉(zhuǎn)條件的DFX信號(hào)去判斷卡住的原因

2024-01-15 10:03:42 987

987

編寫能夠被綜合工具識(shí)別的狀態(tài)機(jī),首先需要理解狀態(tài)機(jī)的基本概念和分類。狀態(tài)機(jī)(FSM)是表示有限個(gè)狀態(tài)以及在這些狀態(tài)之間轉(zhuǎn)換的邏輯結(jié)構(gòu)。

2024-05-01 11:38:00 3182

3182 在FPGA(現(xiàn)場(chǎng)可編程門陣列)中實(shí)現(xiàn)狀態(tài)機(jī)是一種常見的做法,用于控制復(fù)雜的數(shù)字系統(tǒng)行為。狀態(tài)機(jī)能夠根據(jù)當(dāng)前的輸入和系統(tǒng)狀態(tài),決定下一步的動(dòng)作和新的狀態(tài)。這里,我們將詳細(xì)探討如何在FPGA設(shè)計(jì)中實(shí)現(xiàn)狀態(tài)機(jī),包括其基本概念、類型、設(shè)計(jì)步驟、實(shí)現(xiàn)方法以及優(yōu)化策略。

2024-07-18 15:57:34 1848

1848

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論