聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

LabVIEW

+關注

關注

2018文章

3688瀏覽量

348121 -

NI

+關注

關注

19文章

1126瀏覽量

105045 -

程序

+關注

關注

117文章

3847瀏覽量

85404 -

狀態機

+關注

關注

2文章

500瀏覽量

29286

發布評論請先 登錄

相關推薦

熱點推薦

條件判斷法來實現狀態機

。

「示例程序:」

switch(StateVal)

{

case S0:

switch(EvntID)

{

case E1:

action_S0_E1(); /*S0 狀態下 E1

發表于 12-09 08:18

睿遠研究院丨IO-Link規范解讀(十一):ISDU狀態機與EVENT事件

上篇我們介紹了ISDU的典型編碼格式和應用案例,本篇我們就來詳細介紹下,ISDU的狀態機,并把EVENT事件的邏輯,給大家好好解析下。 1主站ISDU狀態機 如上圖所示,ISDU的狀態機的核心

嵌入式開發為何經常用到狀態機架構

一個管腳電平跳變或者一個串口數據,讓整個程序都不動的情況也讓我非常糾結,如果事件一直不發生電平跳變,你要等到世界末日么?

如果應用狀態機編程思想,程序只需要用全局變量記錄下工作狀態,就

發表于 11-25 07:08

睿遠研究院丨IO-Link規范解讀(八):M-Sequence Type 與消息處理狀態機

丟棄,減少后端工作量。 那么今天我們就來深入研究下,消息處理模塊中提到的各類M-Sequence,以及主從站的消息處理狀態機! ? 1 M-Sequence Type 上回講到主站發出來的MC和CKT

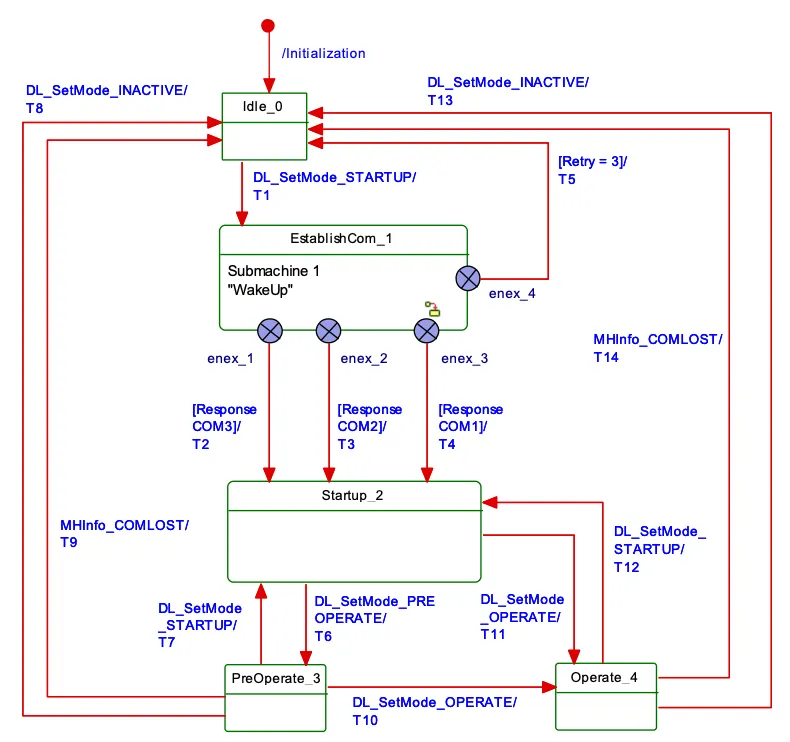

睿遠研究院丨IO-Link規范解讀(六):主從站狀態機解析

前言 書接上文,今天我們就來好好聊聊主從站的DL-Mode狀態機,還請各位童鞋前排坐好! 1主站狀態機解析 主站的DL-Mode狀態機有5個大狀態,也是我們很熟悉的 建立通信、開始、預

蜂鳥SOC的SPI外設:如何修改SPI的時鐘相位和時鐘極性

:

更改狀態機,使結束時間多半拍:

spi_master_rx/rx中的done信號等需要改變:

2. 我們仿真通過,并且下板測試與采樣模塊交互成功

發表于 10-20 09:36

JTAG標準的狀態機實現

JTAG作為一項國際標準測試協議(IEEE1149.1兼容),主要用于芯片內部測試和調試。目前的主流芯片均支持JTAG協議,如DSP、FPGA、ARM、部分單片機等。標準的JTAG接口是20Pin,但JTAG實際使用的只有4根信號線,再配合電源、地。

請問如何在FX10上使用GPIF III狀態機 *.h 文件?

LVCMOS 2 位 SlaveFIFO GPIF III 狀態機的演示中有一個 cy_gpif_header_lvcmos.h 文件。

我想知道如何使用.h文件,只需放入.h文件放入 FX10 項目?

您有它的用戶指南文檔嗎?

發表于 07-16 08:17

NVMe高速傳輸之擺脫XDMA設計之八:PCIe初始化狀態機設計

初始化是PCIe總線正常進行數據傳輸的前提,圖1為PCIe配置初始化狀態機狀態轉移圖。

圖1 PCIe配置初始化狀態機狀態轉移圖

各

發表于 07-05 22:00

有可能在 FX3 GPIF2 中創建兩個獨立的狀態機嗎?

我想,如果我想通過 FX3 GPIF2 創建兩個獨立的傳輸流接口,我需要在 GPIF2 設計器中創建兩個獨立的狀態機,我是否有可能在 GPIF2 設計器中創建兩個獨立的狀態機?

發表于 05-20 06:14

[Actor]在程序框圖編程時,如何操作消息和方法對應的VI

actor應用的關鍵:

當在程序框圖編程時,核心是針對“消息”vi 進行操作,并不操作消息對應的方法vi(具體要實現的功能)。

調用的消息vi時,后臺自動調用對應方法vi。

相當于在隊列狀態機中,隊列元素的進、出操作 與 該元素

發表于 05-13 18:10

求助,關于srammaster.cydsn中狀態機的問題求解

晚上好。

我目前正在學習 GPIF II。

查看..EZ-USB FX3 SDK1.3firmwaregpif_examplescyfxsrammastersrammaster.cydsn中的狀態機,有狀態START和START1。

這意味著什么?

發表于 05-12 06:20

如何對狀態機的程序進行靈活修改

如何對狀態機的程序進行靈活修改

評論