引言

信號完整性是指電路系統中信號的質量。如果在要求的時間內,信號能夠不失真地從源端傳

2010-12-06 10:34:20 1741

1741

信號完整性是指電路系統中信號的質量。如果在要求的時間內,信號能夠不失真地從源端傳送到接收端,就稱該信號

2010-12-30 15:57:01 1160

1160

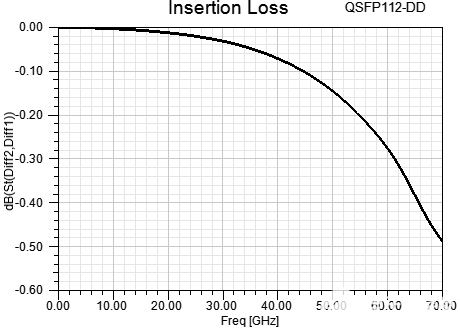

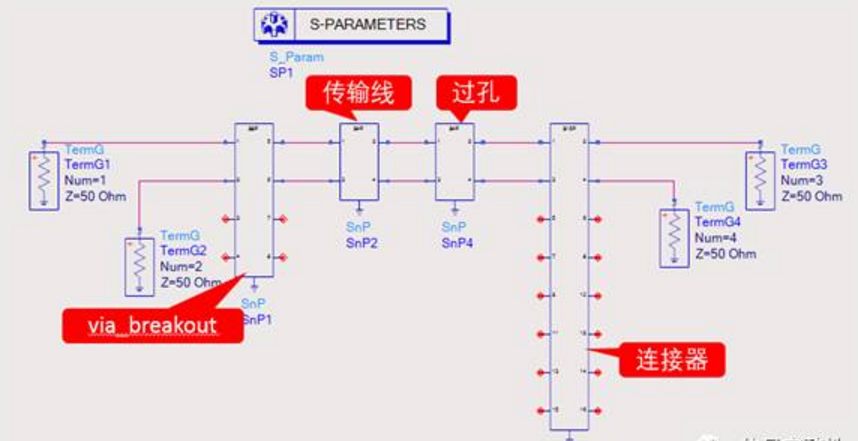

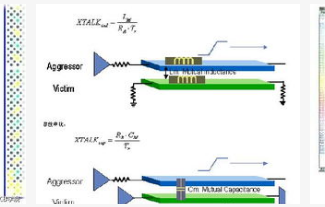

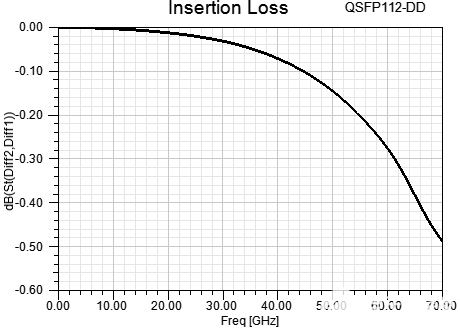

越高的速率傳輸,意味著更快的上升沿和更高的帶寬,這必然會為信號完整性帶來極大的挑戰。要滿足所需的插損、回損、TDR和串擾等,必然要進行高速信號完整性仿真。

以800G DAC為例,高速信號

2022-07-15 16:01:02 2447

2447

定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

2023-03-02 09:41:06 2281

2281

PCB中信號完整性分析的基礎知識可能不是基本的。信號完整性仿真工具非常適合在原理圖和布局設計期間計算不同網絡中信號的行為,但您仍然需要采取一些步驟來解釋結果。

2023-06-09 10:31:57 1533

1533

信號完整性研究的是如何使驅動器輸出的信號傳輸到接收器件并被正確接收。

2023-06-12 17:22:48 3940

3940

信號完整性(Signal Integrity,SI)是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳輸到接收端,我們就稱該信號是完整的。

2023-09-28 11:27:47 4069

4069

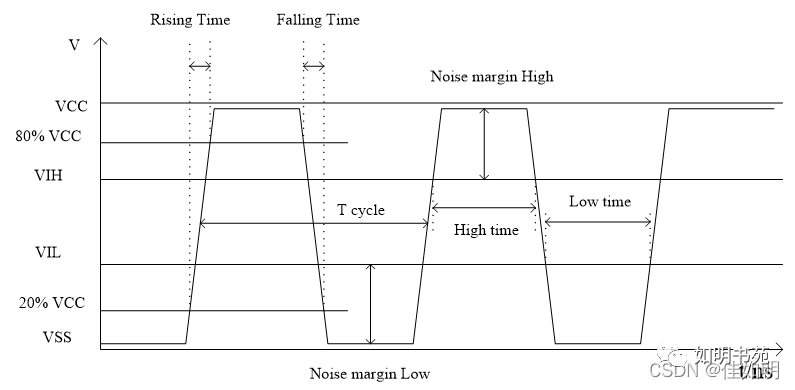

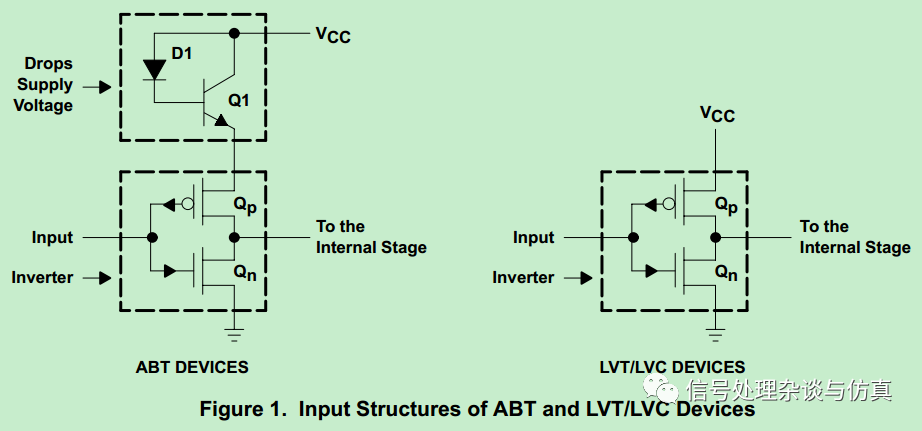

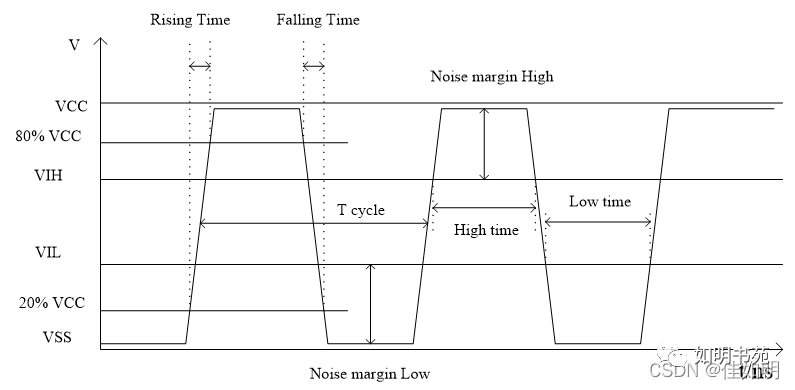

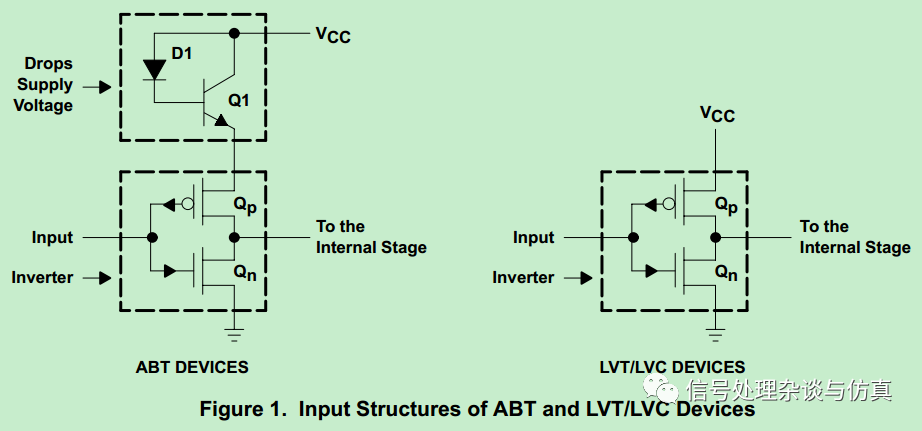

CMOS器件的輸入信號上升時間或下降時間統稱為輸入轉換時間,輸入轉換時間過長也稱為慢CMOS輸入。如果輸入信號上升時間過長,超過器件手冊允許的最大輸入轉換時間,則有可能在器件內部引起大的電流浪涌,造成器件損壞或引起器件輸出電平翻轉(輸入原本為0,輸出為1;或者相反情況)。

2023-10-31 10:39:53 3047

3047

信號完整性(Signal Integrity,SI)是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳輸到接收端,我們就稱該信號是完整的。它是現代通信領域中一個至關重要的概念,隨著

2023-12-01 11:26:23 3449

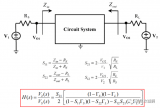

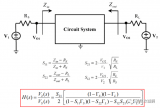

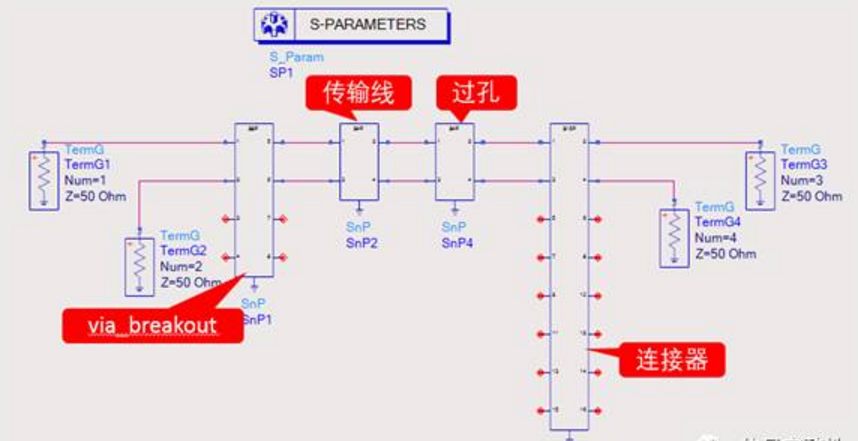

3449 解釋完帶寬這一概念,我們來考慮如何才能通過仿真準確的預測信號完整性。 信號帶寬的確定、器件模型的獲取 當我們確定了要分析的信號的信息(包含速率、接口電平、上升時間等等)、以及驅動器和接收器型號之后

2025-01-22 11:51:07 2573

2573

、仿真軟件優劣等概況;概述后面諸講的各種基本概念。同時,簡要介紹相關技術資料、國內外最新科研成果、國內出版的原版譯著情況等。第二講 信號/互連線帶寬與時頻域阻抗 介紹信號完整性的研究對象——上升邊

2010-12-16 10:03:11

做了電路設計有一段時間,發現信號完整性不僅需要工作經驗,也需要很強的理論指導,壇友能提供一些信號完整性的視頻資料么?非常感謝!

2019-02-14 14:43:52

在altium designer中想進行信號完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

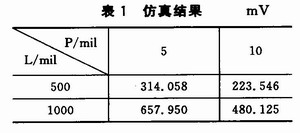

以及信號波形的上升/下降/保持時間。將電路進行瞬態仿真后利用ADS2005A中內含的眼圖工具可自動統計出各抖動分量的值。 電源完整性通常關心的是工作器件所承受的實際電源電壓波動,即圖3中的Vchip

2015-01-07 11:33:53

子電器可靠性工程協會決定在北京組織召開“信號完整性仿真應用高級研修班”,并由北京懷遠文化傳媒有限公司承辦,現將有關事宜通知如下:一、培訓時間、地點:2天,北京 2009年11月28-29日,11月27日報到;二

2009-11-25 10:13:20

信號完整性資料

2015-09-18 17:26:36

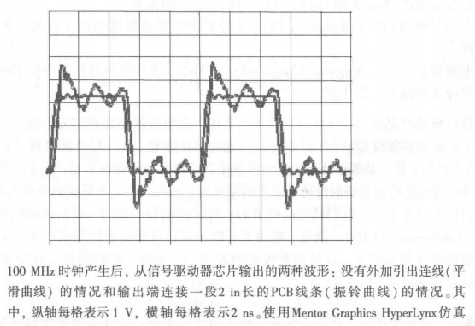

手工連線面成的樣機同規范布線的最終印制板產品一樣都能正常工作。

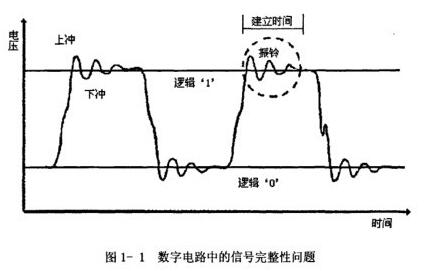

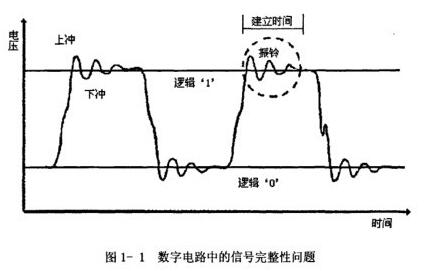

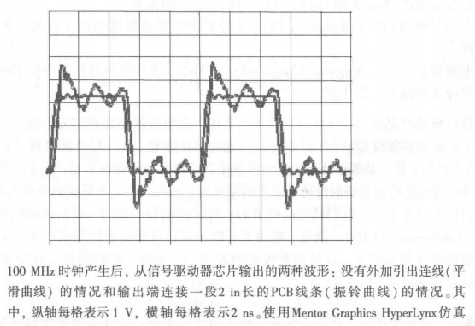

但是現在時鐘頻率提高了,信號上升邊也已普遍變短。對大多數電子產品而言,當時鐘頻率超過100MHz或上升邊小于1 ns時,信號完整性效應

2023-09-28 08:18:07

信號完整性的定義信號完整性包含哪些內容

2021-03-04 06:09:35

擾、軌道塌陷和電磁干擾。3、隨著上升邊的減小或者時鐘頻率的提高,各種信號完整性問題變得更嚴重,并且更加難以解決。4、由于晶體管越來越小,它們的上升邊將越來越短,信號完整性也將成為越來越大的問題,這是

2015-12-12 10:30:56

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

1.信號完整性(Signal Integrity):就是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳送到接收端,我們就稱該信號是完整的。

2019-05-23 06:40:24

什么是DSP圖像處理系統?DSP圖像處理系統中信號完整性的問題是什么?有哪些解決方案?

2021-06-01 06:40:35

信號完整性(Signal Integrity, SI)是指信號在信號線上的質量,即信號在電路中以正確的時序和電壓作出響應的能力。如果電路中信號能夠以要求的時序、持續時間和電壓幅度到達接收器,則可

2018-11-27 15:22:34

`編輯推薦本書全面論述了信號完整性與電源完整性問題。主要講述信號完整性分析及物理設計概論,6類信號完整性問題的實質含義,物理互連設計對信號完整性的影響,電容、電感、電阻和電導的特性分析,求解信號

2017-08-08 18:03:31

征上升時間就要小于該信號上升時間的50%,這是個簡單的經驗法則。2.從頻域角度看,為了比較好的傳輸帶寬為1GHz的信號,互連線的帶寬至少為信號帶寬的兩倍,即2GHz頻域與時域的總結1.上升時間通常

2017-12-06 08:46:10

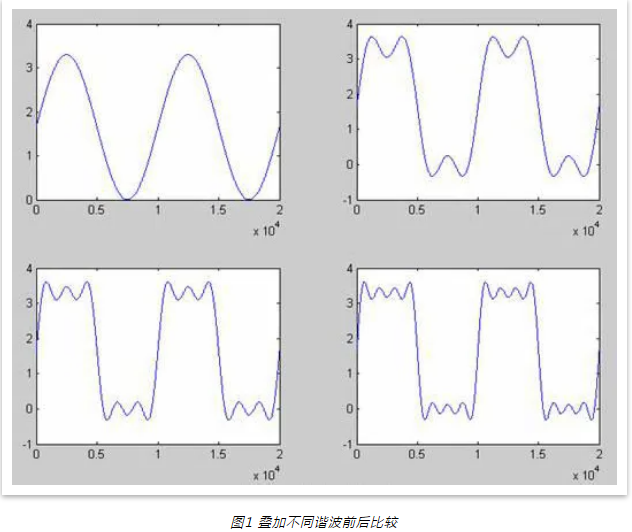

與理想方波越接近。同理降低信號帶寬如刪除高頻分量,其上升時間會變長。有兩種損耗機理:導體損耗和介質損耗。這兩種損耗對高頻分量的衰減大于對低頻分量的衰減。這種選擇性衰減使得在互連線中傳播的信號的帶寬降低

2017-12-01 09:55:07

一般來說:時鐘下降沿比上升沿時間短。這是典型的CMOS輸出驅動器造成的,為P管和N管的串聯,而P管的導通時間短。一般來說,時鐘下降沿比上升沿更容易出現信號完整性的問題,如果將N溝做得比P溝長,可使

2017-11-29 08:46:06

于博士-信號完整性研究

2018-11-14 10:36:36

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

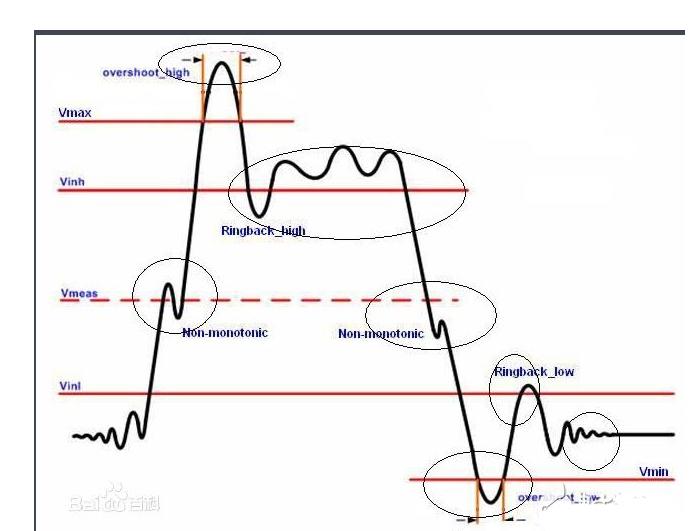

的時延有關,《信號完整性分析》中描述說,“當傳輸線延時Td>信號上升時間的20%時,就要開始考慮由于導線沒有終端端接而產生的振鈴噪聲。當時延大于上升時間的20%時,振鈴會影響電路功能,,必須加以控制,否則這是造成信號完整性問題的隱患。吐過Td

2019-05-22 06:07:06

何為信號完整性?信號完整性包括哪些?干擾信號完整性的因素有哪些?如何去解決?

2021-05-06 07:00:23

1 示波器探頭的上升時間和帶寬示波器主要的限制為三個方面:靈敏性的不足、輸入電壓的幅度不夠大、帶寬限制。只要數字測試中的靈敏度不是特別的高,一般示波器的靈敏度是滿足要求的。在高電平時,數字信號一般

2018-04-19 10:42:59

對上升時間的影響2.10 帶寬及上升時間2.11 “有效的”含義2.12 實際信號的帶寬2.13 帶寬和時鐘頻率2.14 測量的帶寬2.15 模型的帶寬2.16 互連線的帶寬2.17 小結第3章 阻抗

2019-11-13 20:09:31

與帶寬選擇依據類似。在帶寬中,由于當前信號擁有超高速率,并不能一直實現這種經驗法則。注意,示波器上升時間越快,捕獲快速跳變關鍵細節的精度越高。 在某些應用中,您可能知道信號的上升時間。有一個常數,可以把

2016-04-11 14:38:38

解決背板互連中信號完整性問題的兩種方案

2019-09-16 09:08:59

考慮。盡管從信號完整性上表現出來的結果較為直接,但是信號參考層的不完整會造成信號回流路徑變化多端,從而引起信號質量變差,連帶引起了產品的EMI性能變差。這將直接影響最終PCB板的信號完整性。因此研究

2012-08-02 22:18:58

:介紹信號完整性的研究對象——上升邊,介紹上升邊的寬帶信號特點。介紹信號帶寬與信號頻率/周期的表達式。介紹信號帶寬、互連線帶寬、本證上升時間、互連線模型帶寬、測量帶寬等的應用。第三講 電感與地彈、趨膚

2010-11-09 14:21:09

高速電路信號完整性分析與設計—信號完整性仿真仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上升沿從20%~80%VCC的時間,一般是ns級或

2009-09-12 10:31:31

在高速電路設計中信號完整性分析由于系統時鐘頻率和上升時間的增長,信號完整性設計變得越來越重要。不幸的是,絕大多數數字電路設計者并沒意識到信號完整性問題的重要性,或者是直到設計的最后階段才初步認識到

2009-10-14 09:32:02

高速數字硬件電路設計中信號完整性在通常設計的影響是什么?高速電路設計中信號完整性面臨的挑戰有哪些?怎么處理?

2021-04-22 06:26:55

由于系統時鐘頻率和上升時間的增長,信號完整性設計變得越來越重要。不幸的是,絕大多數數字電路設計者并沒意識到信號完整性問題的重要性,或者是直到設計的最后階段才

2009-09-18 09:28:46 0

0 高速電路信號完整性分析與設計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 信號完整性原理分析

什么是“信號完整性”?在傳統的定義中“完整性(integrity)”指完整和末受損的意思。因此,具有良好完整性的數字信號應是干凈,

2009-11-04 12:07:06 212

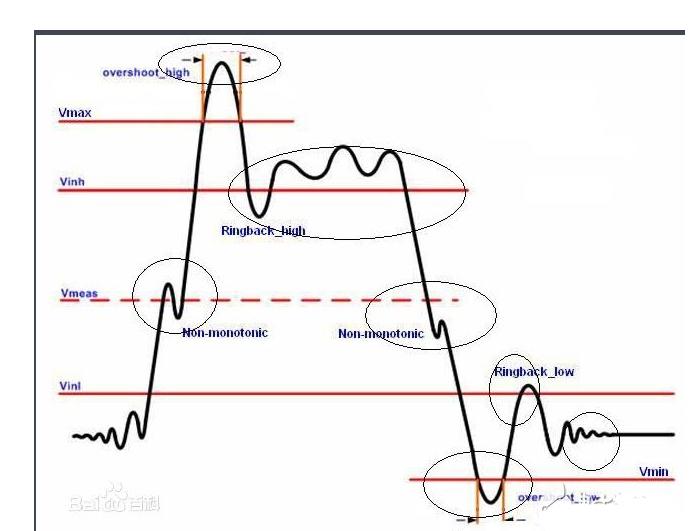

212 信號完整性基礎根據定義, “完整性”是指“完整和無損害的”。 同樣,一個具有良好的完整性的數字信號有干凈、快速的上升沿;穩定和有效的邏輯電平;準確的時間位置和

2010-08-05 15:11:33 242

242 什么是信號完整性

信號完整性(Signal Integrity):就是指電路系統中信號的

2009-06-30 10:23:18 5717

5717

BOB購買了一臺標稱300MHZ的示波器,探頭的標稱值是300MHZ,兩個指標均為3DB帶寬。問:對于上升時間為2NS的信號,這個組合信號的影響如何?

2010-06-03 16:20:14 1022

1022

BOB購買了一臺標稱300MHZ的示波器,探頭的標稱值是300MHZ,兩個指標均為3DB帶寬。問:對于上升時間為2NS的信號,這個組合信號的影響如何?

2010-07-05 11:44:24 2473

2473

在pcb layout中必須要考慮SI差的信號完整性不是由某一因素導致的,而是由板級設計中多種因素共同引起的

2011-11-21 13:57:34 7607

7607 為了使設計人員對信號完整性與電源完整性有個全面的了解,文中對信號完整性與電源完整性的問題進行了仿真分析與設計,也從系統的角度對其進行了探討。

2011-11-30 11:12:24 0

0 本專題詳細介紹了信號完整性各部分知識,包括信號完整性的基礎概述,信號完整性設計分析及仿真知識,還有具體應用中的一些小經驗分享等等,充分翔實的向大家描述了信號完整性。

2011-11-30 11:44:35

在當前的高工作頻率下,影響信號上升時間、脈寬、定時、抖動或噪聲內容的任何事物都會影響整個系統的可靠性。為保證信號完整性,必需了解和控制信號經過的傳輸環境的阻抗。阻

2011-12-21 14:30:46 131

131 2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:26:07 102

102 2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:21:42 2037

2037 本書全面論述了信號完整性問題。主要講述了信號完整性和物理設計概論,帶寬、電感和特性阻抗的實質含義,電阻、電容、電感和阻抗的相關分析,解決信號完整性問題的四個實用技術手段,物理互連設計對信號完整性

2015-11-10 17:36:24 0

0 電地完整性、信號完整性分析導論,有需要的下來看看

2016-02-22 16:18:01 71

71 10129@52RD_信號完整性與電源完整性的仿真分析與設計

2016-12-14 21:27:39 0

0 所謂“萬丈高樓平地起”,說的就是這個道理,想從事信號完整性工作就必須對整個信號完整性的理論基礎有一個很明晰的了解。至少要熟讀幾本信號完整性方面的書籍,了解什么是信號完整性;了解信號完整性研究的對象和內容是什么;信號完整性與哪些因素有關系;信號完整性會影響到產品的哪一個方面;等等。

2017-08-29 15:47:22 21314

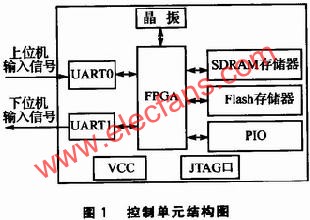

21314 高速數字系統中,對于頻率達到百兆甚至CHz以上的信號,會由于系統的信號完整性的問題而導致信號質量不佳。甚至對于不到50 MHz的信號,由于其電平跳變時間在Ins甚至ps級,最終PCB產品中依然有可能會m現信號完整性問題。 為了縮短開

2017-11-09 16:24:32 13

13 的工藝發展使得集成度越來越高,導致芯片上電流密度急速增加,使信號完整性的問題更加嚴重。因此非常有必要從整個系統設計開始就考慮信號完整性與電源完整性的問題。這就需要在設計前后把信號完整性和電源完整性仿真引入到設計流程中。

2017-12-04 04:59:26 34095

34095

信號的上升時間,對于理解信號完整性問題至關重要。

2018-04-02 17:45:57 16646

16646

信號上升時間并不是信號從低電平上升到高電平所經歷的時間,而是其中的一部分。業界對它的定義尚未統一,最好的辦法就是跟隨上游的芯片廠商的定義,畢竟這些巨頭有話語權。

2018-04-11 11:16:00 9656

9656

本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設計信號完整性的方法。

2018-05-23 15:08:32 11792

11792 信號上升時間并不是信號從低電平上升到高電平所經歷的時間,而是其中的一部分。業界對它的定義尚未統一,最好的辦法就是跟隨上游的芯片廠商的定義,畢竟這些巨頭有話語權。通常有兩種:第一種定義為10-90

2019-06-26 15:40:06 2131

2131

信號完整性(S i gnal Integri ty,SI)是指信號在信號線上傳輸的質量。對于數字電路,就是要信號在電路中能以正確的時序和電壓做出響應。如果電路中信號能夠以要求的時序、持續時間和電壓

2019-05-27 13:58:16 2399

2399

信號的第一次諧波幅度約為0.6V,第三次諧波的幅度約是0.2V。 3、信號的帶寬和上升時間的關系為:BW=0.35/RT。例如,如果上升時間是1NS, 則帶寬是350MHZ。如果互連線的帶寬是3GHZ,則它可傳輸的最短上升時間約為0.1NS。

2020-09-08 10:46:00 1

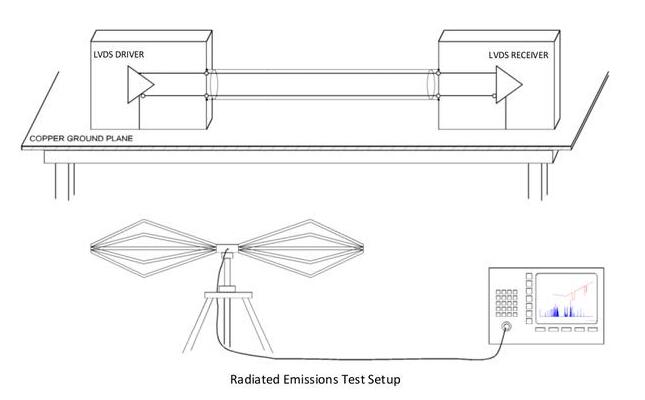

1 隨著電路速度的增加,信號完整性在電子設計中變得更加重要。更快的數據速率和更短的上升/下降時間使信號完整性更具挑戰性。信號的失真和降級會對電磁兼容性產生不利影響。隨著信號完整性降低,電路輻射和電路抗擾性都可能會增加。

2020-07-09 15:29:48 4237

4237

去的低速時代,電平跳變時信號上升時間較長,通常幾個 ns。器件間的互連線不至于影響電路的功能,沒必要關心信號完整性問題。

2020-07-15 08:00:00 3

3 我們在介紹信號完整性的時候通常會說“當傳輸延時大于六分之一的信號的上升時間時,需要考慮信號完整性問題”,于是乎教科書里面都會配上一副類似于這樣表現上升時間或者傳輸延時與反射的圖片: 最開始的時候小陳

2021-04-13 09:46:29 3365

3365

信號完整性是指信號在通過一定距離的傳輸路徑后在特定接收端口相對指定發送端口信號的還原程度。在討論信號完整性設計性能時,如指定不同的收發參考端,則對信號還原程度會用不同的指標來描述。通常指定的收發

2021-01-05 16:21:17 13

13 根據定義, “完整性”是指“完整和無損害的”。 同樣,一個具有良好的完整性的數字信號有干凈、快速的上升沿;穩定和有效的邏輯電平;準確的時間位置和沒有任何的瞬態跳變。

2021-01-05 17:32:32 26

26 本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-20 14:22:53 2344

2344

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-23 08:45:50 28

28 本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

信號完整性是指高速產品設計中由互連線引起的所有問題。包括以下幾部分:

時序

噪聲

電磁干擾(EMI

2021-01-26 09:28:30 12

12 信號完整性(SignalIntegrity)就是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳輸到接收端,我們就稱該信號是完整的。

2021-03-14 14:51:31 4671

4671 總結了在高速PCB板設計中信號完整性產生的原因、抑制和改善的方法。介紹了使用IBS模型的仿真步驟以及使用 CADENCE公司的 Allegro SPB軟件,支持IBIS模型對反射和串擾的仿真,驗證了其改善后的效果,可以直觀地看到PCB設計是否滿足設計要求,進而指導和驗證高速PCB的設計。

2021-05-27 13:59:31 22

22 信號完整性與電源完整性的仿真(5V40A開關電源技術參數)-信號完整性與電源完整性的仿真分析與設計!!!

2021-09-29 12:11:21 91

91 何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2022-01-07 15:38:32 0

0 高速電路信號完整性分析與設計—信號完整性仿真

2022-02-10 17:29:52 0

0 的工藝發展使得集成度越來越高,導致芯片上電流密度急速增加,使信號完整性的問題更加嚴重。因此非常有必要從整個系統設計開始就考慮信號完整性與電源完整性的問題。這就需要在設計前后把信號完整性和電源完整性仿真引入到設計流程中。

2022-08-30 09:13:44 8293

8293 定義:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同 引起的。當電路中信號能以要求的時序、持續時間和電壓幅度到達接收端時,該電路就有很好的信號完整性。當信號不能正常響應時,就出現了信號完整性問題。

2022-11-16 14:56:00 6199

6199 由信號頻率升高、上升時間減小所引起PCB互連線上的所有信號質量問題都屬于信號完整性的研究范疇。本論文的主要研究可概括為傳輸線在PCB設計制造過程中所產生的信號完整性問題,具體分為三個方面:

(1

2023-03-27 10:40:30 0

0 業界經常流行這么一句話:“有兩種設計師,一種是已經遇到了信號完整性問題,另一種是即將遇到信號完整性問題”。固態硬盤作為一種高集成度的高時鐘頻率的硬件設備,信號完整性的重要性不言而喻。借著這句話本文主要跟大家聊下信號完整性的一些基本內容。

2023-06-27 10:43:26 3270

3270

小的成本,快的時間使產品達到波形完整性、時序完整性、電源完整性的要求;我們知道:電源不穩定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產生畸變,

2023-08-17 09:29:30 8717

8717

pcb信號完整性詳解 隨著電子領域技術日新月異的發展,高速電路已經成為了電路設計的重要領域之一。在高速電路中,信號完整性顯得尤為重要。在設計PCB電路時,信號完整性是一個必須考慮的因素。那么

2023-09-08 11:46:58 2269

2269 信號完整性是指在規定的時間內,信號從源端傳輸到接收端,信號不失真(能判斷出信號的高低電平)。

2023-09-21 16:30:14 4037

4037

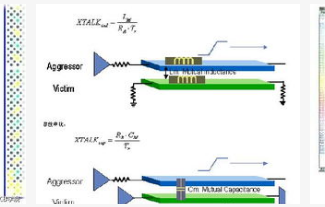

完整性需要在整個系統和組件設計過程中加以考慮。與過去不同的是, 互連不再是事后考慮的問題 。隨著上升時間的縮短和時鐘頻率的提高,曾經被認為是電氣透明的連接器和電纜會對系統傳輸信號的質量產生重大影響。這些因素包括 串擾、回波損耗、插入損耗和電磁干擾(EMI) 等因素都會對確定哪種互連解決方

2023-10-19 15:09:49 899

899

示波器和探頭的上升時間與帶寬之間具有怎樣的量化關系? 示波器和探頭是現代電子測量技術中不可或缺的兩個部分。其中,示波器是一種測量電信號波形的儀器,而探頭則是將電信號引入示波器中的裝置。在電子測量中

2023-10-22 12:43:33 1865

1865 信號頻率和上升時間的關系? 信號頻率和上升時間是電子領域中兩個常用的概念。它們之間的關系是比較密切的,一個信號的頻率越高,它的上升時間就會越短。在本文中,我將會詳細介紹信號頻率和上升時間的相關知識

2023-11-06 11:01:07 7207

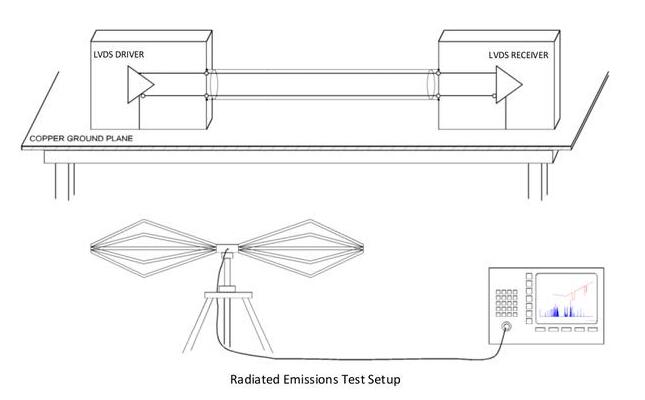

7207 在現代電子通信和數據處理系統中,信號完整性(Signal Integrity, SI)是一個至關重要的概念。它涉及信號在傳輸過程中的質量保持,對于確保系統性能和穩定性具有決定性的影響。本文將從信號完整性的定義、影響因素、測試方法、以及在實際應用中的重要性等方面,對信號完整性進行詳細的探討。

2024-05-28 14:30:58 2968

2968 電子發燒友網站提供《信號完整性與電源完整性-電源完整性分析.pdf》資料免費下載

2024-08-12 14:31:17 117

117 電子發燒友網站提供《高速PCB的信號完整性、電源完整性和電磁兼容性研究.pdf》資料免費下載

2024-09-19 17:37:43 1

1 高速電路中的信號完整性和電源完整性研究

2024-09-25 14:44:38 0

0 高速高密度PCB信號完整性與電源完整性研究

2024-09-25 14:43:20 5

5 2024年12月20日14:00-16:00中星聯華科技將舉辦“高速信號完整性分析與測試”-“碼”上行動系列線上講堂線上講堂。本期會議我們將為大家介紹高速串行總線傳輸基本框架,什么是信號完整性?高速

2024-12-15 23:33:31 1134

1134

響應曲線從零時刻到首次達到穩態值的時間,通常定義為響應曲線從穩態值的10%上升到穩態值的90%所需的時間。 很多信號完整性問題都是由信號上升時間短引起的,那么信號上升時間和信號帶寬有什么關系呢? 對于數字電路,輸出的通常是方波信

2025-01-06 17:56:48 2686

2686

信號完整性揭秘-于博士SI設計手記4.4有限上升時間信號的反射波形從上一節討論中我們知道,阻抗不連續的點處,反射信號是人射信號的一個副本,并討論了上升時間為0的信號的反射情況。這些規律對于上升時間

2025-08-01 08:37:38 768

768

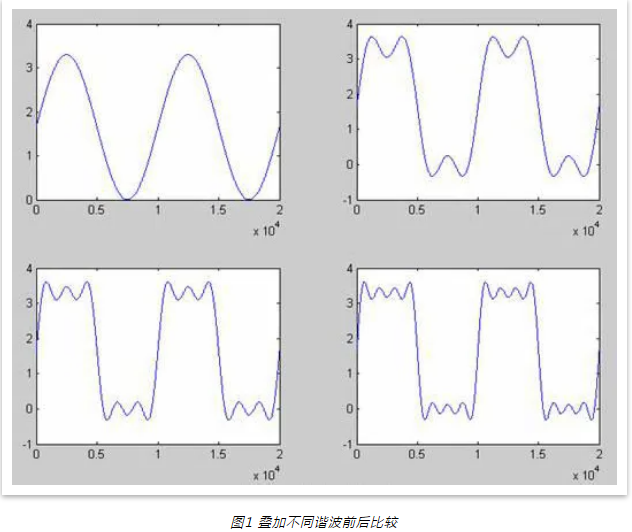

信號完整性揭秘-于博士SI設計手記2.6信號帶寬與上升時間的關系2.4節已經說明了由信號的頻譜可以得到時域波形,實質上是傅里葉逆變換過程,只不過對于周期信號來說,這一傅里葉逆變換過程更明顯地

2025-08-15 17:56:54 1017

1017

電子發燒友App

電子發燒友App

評論