完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > versal

Versal 產(chǎn)品組合基于 臺積電(TSMC)的 7 nm FinFET 工藝技術(shù),是第一個(gè)將軟件可編程性與特定領(lǐng)域硬件加速和靈活應(yīng)變能力相結(jié)合的平臺,這對于跟上當(dāng)今快速的創(chuàng)新步伐至關(guān)重要。

文章:82個(gè) 瀏覽:8483次 帖子:0個(gè)

詳解基于賽靈思的Versal? ACAP設(shè)計(jì)創(chuàng)建步驟

Versal ACAP(自適應(yīng)計(jì)算加速平臺)是高度集成化的多核計(jì)算平臺,可通過靈活的自適應(yīng)能力來滿足不斷變化的動(dòng)態(tài)算法的需求。VCK190 是賽靈思最早...

DDR4/LPDDR4硬核控制器I/O plannin的設(shè)計(jì)和實(shí)現(xiàn)

在Versal新一代ACAP器件上,除了延續(xù)之前Ultrascale/Ultrascale+系列器件上已有的DDR4 IP之外,還配置了最新的DDR4/...

AMD Versal自適應(yīng)SoC內(nèi)置自校準(zhǔn)的工作原理

本文提供有關(guān) AMD Versal 自適應(yīng) SoC 內(nèi)置自校準(zhǔn) (BISC) 工作方式的詳細(xì)信息。此外還詳述了 Versal 的異步模式及其對 BISC...

集賽靈思多年投資和35年架構(gòu)之大成,基于7nm工藝,多核異構(gòu)且能靈活改變,面向所有開發(fā)者和各種應(yīng)用的Versal 宣布發(fā)貨了!

使用Aurora 6466b協(xié)議實(shí)現(xiàn)AMD UltraScale+ FPGA與AMD Versal自適應(yīng)SoC的對接

在本博客中,我們將介紹使用 Aurora 6466b 協(xié)議實(shí)現(xiàn) AMD UltraScale+ FPGA 與 AMD Versal 自適應(yīng) SoC 的對...

Versal CPM AXI Bridge模式的地址轉(zhuǎn)換

Versal 系列的 DMA axi bridge 模式可以在 PL 的 QDMA IP 或者在 CPM(The integrated block fo...

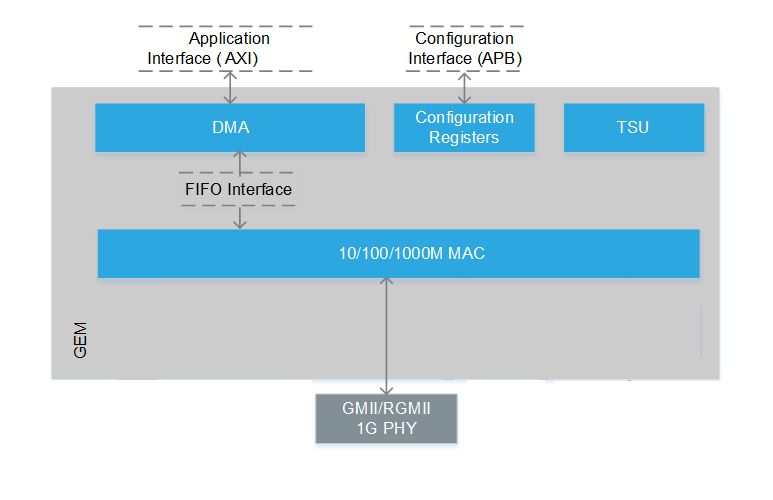

在探討為什么要升級到 Versal ACAP 時(shí),必須首先認(rèn)識到所有硬 IP 的價(jià)值,包括存儲控制器、PCIe?、多速率以太網(wǎng)和片上可編程網(wǎng)絡(luò)( NoC...

Versal GTM如何用Tcl命令在IBERT生成QPRBS13序列

目前對于 Vivado 2023.1 版本的 IBERT GUI 界面暫時(shí)不支持 QPRBS13 的設(shè)置,需要通過 tcl 或者端口設(shè)置的方法來實(shí)現(xiàn)。

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之 Versal 介紹(2)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之 Versal 介紹,以及Versal 芯片開發(fā)流程的簡介。

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部參考時(shí)鐘設(shè)計(jì)指南

本文旨在呈現(xiàn)使用 DDR4、LPDDR4 或 LPDDR4X 存儲器控制器的 Versal ACAP 器件的外部參考時(shí)鐘電路要求

2023-07-10 標(biāo)簽:仿真DDR4時(shí)鐘設(shè)計(jì) 2.6k 0

如何利用XPIO構(gòu)建并實(shí)現(xiàn)帶有Strobe的高速接口設(shè)計(jì)

在 AMD Versal 自適應(yīng) SoC 器件中,SelectIO 是實(shí)現(xiàn)高速接口的重要組成部分。它為器件提供了靈活且高性能的通用 I/O 資源,支持多...

AMD Versal系列FPGA NoC介紹及實(shí)戰(zhàn)

NoC是相對于SoC的新一代片上互連技術(shù),從計(jì)算機(jī)發(fā)展的歷史可以看到NoC 必將是SoC 之后的下一代主流技術(shù),SoC 通常指在單一芯片上實(shí)現(xiàn)的數(shù)字計(jì)算...

2023-07-13 標(biāo)簽:fpgaamd計(jì)算機(jī) 2.4k 0

PCIe 仿真需要Endpoint 模型和Root Port 模型協(xié)同工作。用戶一般可以采用購買BFM/VIP 來模擬對端模型也可以自己設(shè)計(jì)對端模型,更...

本篇博文側(cè)重于提供 Versal GTY 仿真示例、演示 GTY 如何解復(fù)位以及如何執(zhí)行速率變更。

Versal? 是由多個(gè)高度耦合的可配置塊組成的自適應(yīng)計(jì)算加速平臺?(ACAP)

2023-07-07 標(biāo)簽:NoCVivado啟動(dòng)文件 2.1k 0

Versal HDIO OBUFT和IOBUF三態(tài)時(shí)序影響

本文著重探討 HDIO OBUFT 和 IOBUF 用例。如果含三態(tài)控制 (OBUFT/IOBUF) 的 HDIO 輸出緩沖器的上電電壓為 3.3 V ...

本文涵蓋了在 Versal GTY 和 GTYP 中使用模式生成器和檢查器時(shí)對以下操作的限制

AMD Versal自適應(yīng)SoC中eMMC燒錄/啟動(dòng)調(diào)試檢查表(下)

有多種受支持的方式可用于燒錄 eMMC 器件,包括使用 AMD Vivado IDE、使用 AMD Vitis GUI 或使用 U-Boot。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |