作者:Manuel Uhm ,賽靈思芯片市場營銷總監

在我與客戶交流時,常被問到這個問題。也許措辭并非完全如此,但大致是下面這樣:“為什么我要升級到 Versal?ACAP?現在是時候這樣做了嗎?”

這是一個很好的問題,而且答案也很簡單,那就是——“具體情況具體分析”。

好吧,也許這樣的答案根本不簡單!公正地說,有諸多因素需要考慮,包括設計要求/資源、設計能在多大程度上利用 Versal ACAP 中數量龐大的硬 IP、庫和軟 IP 可用性、芯片可用性、生產時限等。

因此,具體答案確實會隨著相關因素的變化而發生改變。我們將在今后的博文中探討這些主題,但今天,我想把重點放在“為什么升級到 Versal”這個問題上并提供具體的客戶示例。

認識到所有硬 IP 的價值

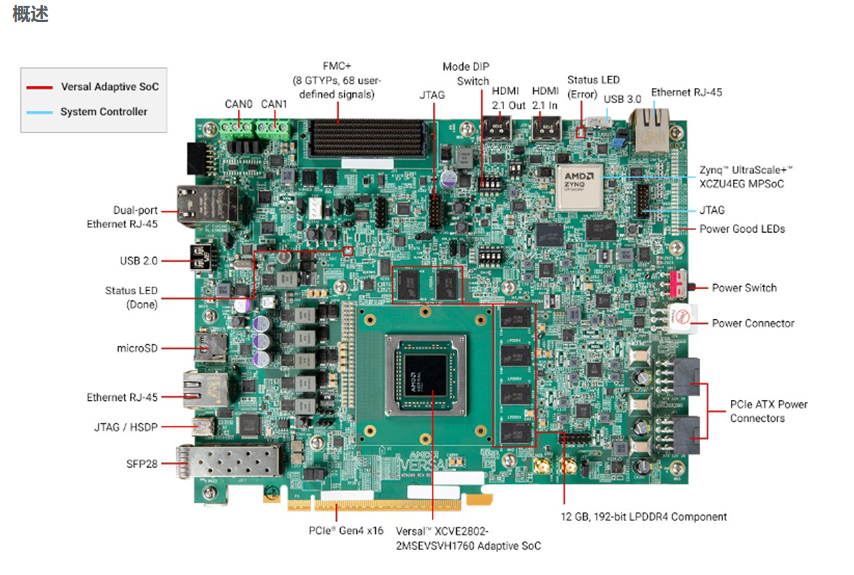

在探討為什么要升級到 Versal ACAP 時,必須首先認識到所有硬 IP 的價值,包括存儲控制器、PCIe?、多速率以太網和片上可編程網絡( NoC )等常用基礎設施的價值,它可以減少對靈活應變的引擎或可編程邏輯的路由需求。

一些 Versal 系列還包含 AI 引擎(一種非常適合高級信號處理和 ML 算法的新型矢量處理器)、高帶寬存儲器、直接 RF 和高速密鑰。賽靈思將這些 IP 全部硬化的主要原因之一在于,賽靈思在多年前就意識到摩爾定律即將走向終點,僅靠縮小晶體管難以為客戶在每個新的工藝節點上提供他們所期待的性能提升和功耗下降。

下圖所示的是 Versal AI Core 系列器件中硬 IP 的價值。可以看出,與我們大獲成功的 16nm UltraScale+? 產品相比,它擁有 LUT 占用大幅降低、功耗顯著下降等多項優勢。在 Versal AI Core VC1902 器件中,有望省下多達 360 萬個 LUT。

當然,大多數設計并不能用到所有硬 IP ,但如果將一個類似設計移植到 Versal ACAP,就會看到 LUT 占用和功耗的實質性降低,而且還可以提供布局布線速度加快、日設計迭代次數增加等附加優勢。

Versal AI Core 系列中集成外殼程序和硬 IP 的價值

借助 AI 引擎實現高級信號處理

今天我還想重點講解一下 AI 引擎。AI 引擎由數十個到數百個(在最大型的 AI Core 系列器件 VC1902 中多達 400 個)專為線性代數和矩陣數學等數學功能優化的小型 VLIW SIMD 矢量處理器陣列構成。當人們聽到“AI 引擎”一詞時,往往會自然而然地想到人工智能。

然而,這些功能只是眾多高級信號處理算法(如波束成型和大規模 MIMO )和機器學習推斷算法(如用于圖像分類的卷積神經網絡( CNN ))的基本構建塊。有鑒于這一原因,無論是信號處理還是推斷,AI 引擎都能分別提供復數數據和實數數據支持。

AI 引擎的關鍵目標應用之一是 5G 無線系統信號處理。針對一個支持 200MHz 瞬時帶寬 2 的 64 天線系統的波束成型技術,AI 引擎可為其提供 5 倍的計算密度并降低 50% 的功耗。這也引起了領先的 5G 測試測量設備提供商 Keysight 的關注。

此外,他們也十分注重開發生產力。誠然,他們擁有負責靈活應變的引擎硬件編程的專家,但是相比硬件布局布線需要耗費數個小時, AI 引擎的編譯用時僅需要幾分鐘,這樣一來,他們的 5G 無線算法的設計與開發生產力就會顯著提高,每星期便能多完成幾次設計迭代。

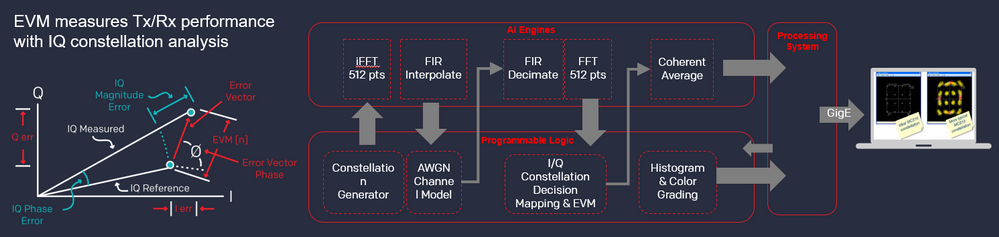

然而,從他們的實現方案原理圖可以看出(參見下圖),Versal ACAP 的系統級價值可謂是決定性的,因為他們能將 AI 引擎的功耗及生產力與靈活應變的引擎的靈活性相結合,創建出令人嘆服的 EVM 演示。

EVM 測量 Tx/Rx 性能及其 IQ 級聯分析

這僅僅是客戶采用 Versal ACAP 架構(特別是 AI 引擎)從而獲得重大效益的示例之一。還有眾多其他客戶在 VC1902 上為 AI 引擎編程,用于 5G、數據中心推斷、邊緣推斷原型設計、雷達、線纜接入等眾多應用。

如果您有興趣進一步了解 Versal AI Core 系列(點擊此處了解)中的 AI 引擎,請閱讀本白皮書(點擊此處閱讀)并觀看 Keysight 視頻(點擊此處查看),直接聆聽他們講述更多有關 AI 引擎的價值。

編輯:hfy

-

信號處理

+關注

關注

49文章

1097瀏覽量

104931 -

存儲控制器

+關注

關注

0文章

24瀏覽量

9457 -

Versal

+關注

關注

1文章

172瀏覽量

8390 -

AI引擎

+關注

關注

0文章

19瀏覽量

1397

發布評論請先 登錄

探索AMD XILINX Versal Prime Series VMK180評估套件,開啟硬件創新之旅

AMD Versal自適應SoC內置自校準的工作原理

AMD 7nm Versal系列器件NoC的使用及注意事項

在AMD Versal自適應SoC上使用QEMU+協同仿真示例

基于AMD Versal器件實現PCIe5 DMA功能

AMD第二代Versal AI Edge和Versal Prime系列加速量產 為嵌入式系統實現單芯片智能

利用AMD VERSAL自適應SoC的設計基線策略

Versal 600G DCMAC Subsystem LogiCORE IP產品指南

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

面向AI與機器學習應用的開發平臺 AMD/Xilinx Versal? AI Edge VEK280

AMD Versal自適應SoC器件Advanced Flow概覽(下)

AMD Versal自適應SoC器件Advanced Flow概覽(上)

是否采用 Versal?為什么升級到 Versal?

是否采用 Versal?為什么升級到 Versal?

評論