1 引言

在高速信號處理系統中, 需要緩存高速、大量的數據, 存儲器的選擇與應用已成為系統實現的關鍵所在。DDR SDRAM是一種高速CMOS、動態隨機訪問存儲器, 它采用雙倍數據速率結構來完成高速操作。SDR SDRAM一個時鐘周期只能傳輸一個數據位寬的數據, 因此在相同的數據總線寬度和工作頻率下, DDR SDRAM的總線帶寬比SDR SDRAM的總線帶寬提高了一倍。

Xilinx VirtexTM- 4 FPGA 具備ChipSync 源同步技術等優勢。它的輸入輸出模塊( IOB) 提供了封裝引腳與內部可配置邏輯之間的接口, 無論是輸入路徑還是輸出路徑都提供了一個可選的SDR 和DDR 寄存器。VirtexTM- 4 的IOB 專門針對源同步設計進行了優化, 包括每一位的偏移校正、數據的串行化和解串行化、時鐘分頻以及專用的本地時鐘資源等, 而且它在每一個I/O 模塊中都提供了64- 階延遲線。這些特性使得VirtexTM- 4 FPGA 能夠更好的實現DDR SDRAM控制器的邏輯設計, 準確可靠的捕獲數據。

實驗板選擇專為DSP 應用而優化的Virtex- 4 SX35 作為DDR SDRAM控制器的實現平臺, 選用Micron MT46V8M16P-75Z DDR SDRAM。

2 DDR SDRAM 控制器工作原理

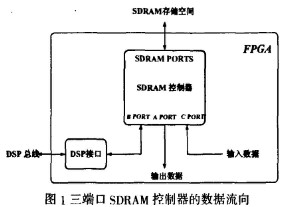

DDR SDRAM控制器的主要功能就是完成對DDR SDRAM的初始化, 將DDR SDRAM復雜的讀寫時序轉化為用戶簡單的

讀寫時序, 以及將DDR SDRAM接口的雙時鐘沿數據轉換為用戶的單時鐘沿數據, 使用戶像操作普通的RAM一樣控制DDR SDRAM; 同時, 控制器還要產生周期性的刷新命令來維持DDR SDRAM內的數據而不需要用戶的干預。該控制器的模塊化表示如圖1。

應用層接口是DDR 控制器與FPGA 用戶設計的接口。對于DDR 控制器的用戶來說, 只需要了解如何使用應用層接口, 通

過應用層接口給DDR 控制器發出指令、數據, 并且接收數據。這種模塊化設計增加了DDR 控制器的可移植性, 也使用戶使用起來更簡單。

要功能是:完成存儲器的初始化, 接收并解碼用戶指令然后產生讀、寫、刷新等指令。控制層的邏輯設計主要是由一個狀態機管理的。物理層是直接與DDR SDRAM通信的平臺, 它的主要功能是:捕獲DDR SDRAM發出的數據、以及通過輸入輸出緩存發送所有DDR SDRAM的控制信號、地址信號以及數據信號。

2.1 控制層工作原理

控制層主要由一個狀態機來控制DDR SDRAM控制器的狀態轉移。狀態機如圖2 所示。

DDR SDRAM上電后必須按照規定的程序完成初始化的過程。在初始化過程中一定要注意普通模式寄存器與擴展模式寄

存器的值是否正確。普通模式寄存器用來設定DDR SDRAM的工作方式, 包括突發長度、突發類型、CAS 潛伏期和工作模式;擴展模式寄存器主要實現對DDR SDRAM內部DLL 的使能和輸出驅動能力的設置。在本實驗板中選擇的是Micron

MT46V8M16P- 75Z 型號的DDR SDRAM, 該型號芯片CAS 潛伏期只能為2 或者2.5。

初始化完成之后, DDR SDRAM進入正常的工作狀態, 此時可對存儲器進行讀寫和刷新操作。在本設計中為了計算讀數據

延遲量引入了一個假讀操作(Dummy Read) , 這將在下一節中詳細分析。DDR SDRAM在一對差分時鐘的控制下工作。命令在每個時鐘的上升沿觸發。隨著數據一起傳送的還包括一個雙向的數據選通信號DQS, 接收方通過該信號來接收數據。該選通信號與數據相關, 其作用類似于一個獨立的時鐘。DQS 作為選通信號在讀周期中由DDR SDRAM來產生。讀周期中, DQS 與數據是邊沿對齊的。讀操作時, DDR 控制器采用直接時鐘獲取的方式捕獲數據。讀命令觸發后, 數據將在CAS 延遲之后出現在數據總線上。DQS 在寫周期中是由DDR 控制器產生的。寫周期中, DQS 與數據是中心對齊的。讀寫操作時序如圖3(DQ 指傳輸的數據) 。

在進行讀寫操作之前需要先執行ACTIVE 命令( 激活命令) , 與激活命令一起被觸發的地址用來選擇將要存取的區( bank) 和頁( 或行) 。與讀或寫命令一起觸發的地址位用來選擇突發存取的起始列單元。在激活指令之前還有一個預充電

( PRECHARGE) 操作, 預充電操作關閉之前進行操作的存儲區或行, 此操作之后DDR SDRAM才能對新的區或者行進行讀寫操作。

DDR SDRAM需要用自動刷新(AUTO REFRESH) 命令來周期性的刷新DDR SDRAM, 以保持其內部的數據不丟失。自動刷新必須在所有區都空閑的狀態下才能執行。128Mb 的DDR SDRAM執行自動刷新的周期最大為15.625μs。

寫操作是由FPGA 向DDR SDRAM寫入數據, 只需按照DDR SDRAM的工作要求發出相應的指令即可, 邏輯設計相對簡單, 因此下面我們將詳細介紹讀操作中的數據捕獲技術。

2.2 物理層數據捕獲技術及數據通道電路

物理層的主要功能是獲得DDR SDRAM發出的數據、以及通過輸入輸出緩存發送所有DDR SDRAM的控制信號、地址信號以及數據信號。數據捕獲技術及數據通道電路是DDR SDRAM控制器的技術核心。DDR SDRAM接口是源同步接口,

即數據與傳輸時鐘是邊沿對齊的。因此, 為了在FPGA 中可靠捕獲數據要么延遲時鐘要么延遲數據, 使數據與時鐘中心對齊。本設計采取直接時鐘數據捕獲技術。

所謂直接時鐘數據捕獲技術就是利用DQS 信號計算數據延遲量, 通過延遲數據使數據中心與FPGA 內部時鐘沿對齊, 然

后用該內部時鐘直接讀取數據。DQS 是由DDR 發出的數據選通信號, 它與FPGA 內部時鐘頻率相同。此項技術的關鍵是確定數據的延遲時間。相對于其他的數據捕獲技術, 這種直接時鐘數據捕獲技術可以應用于更高的時鐘頻率, 精確性和穩定性都高于其他方法。

為了得到數據應該延遲的時間量, 首先要對DQS 進行邊沿檢測。控制器發出Dummy_rd_en 信號( 即假讀信號) 使DDR

SDRAM 發出DQS 信號, 當延遲量計算完畢時, 置Dummy_rd_en 為低。

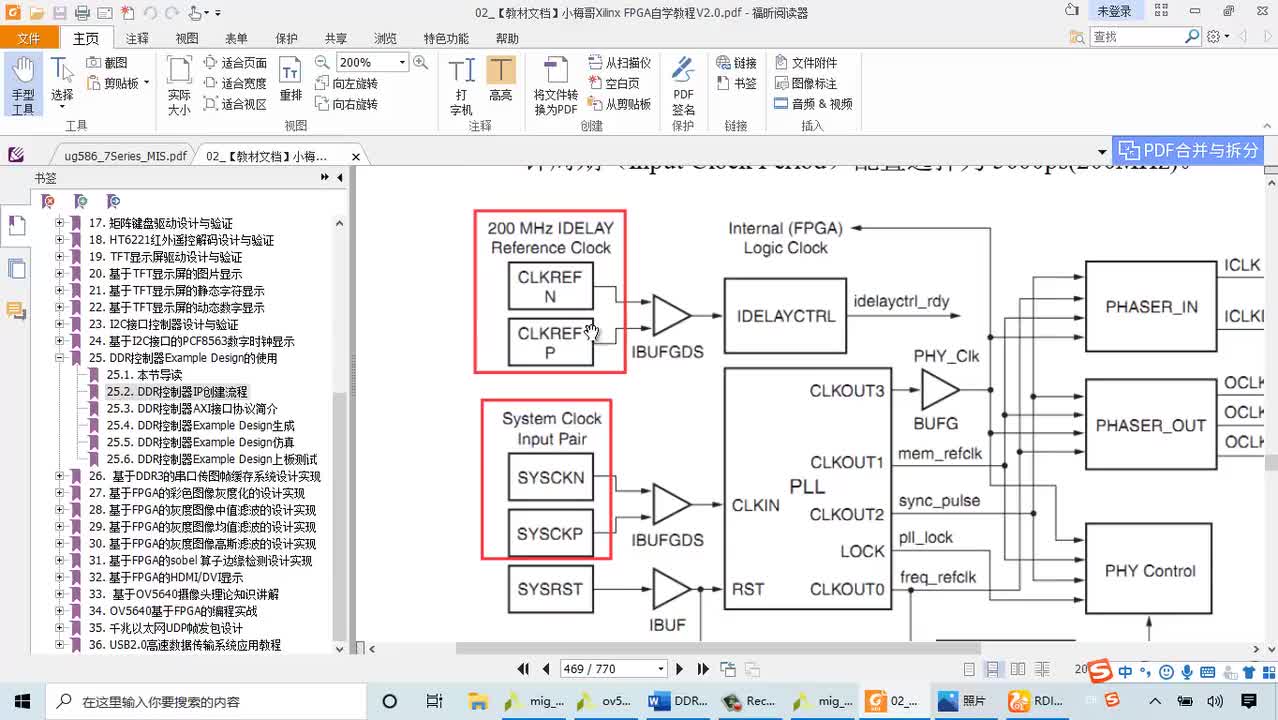

在Xilinx VirtexTM- 4 FPGA 中實現該延遲檢測電路是非常容易的, 因為設計可以直接利用FPGA 內部的IDELAY 與IDELAY_CTRL 電路。圖5 表示了邊沿檢測以及數據通道電路。

在該電路中, DQS 輸入到IDELAY 模塊, 延遲量初始化為0, 然后延遲量逐次遞增, 在這個過程中不斷檢測延遲后的DQS 的跳變沿, 并將延遲量TAP 值記錄下來, 以便計算數據DQ 的延遲量。在圖中可看出, 邊沿檢測和控制邏輯發出DLYRST、DLYCE 和DLYINC 三個信號來控制IDELAY 延遲模塊的工作模式。

由于IDELAY 模塊的最大延遲階數為64, 且在Xilinx VirtexTM-4 FPGA 中, 延遲模塊的精度TIDELAYRESOLUTION 為75ps, 所以延遲時間最大為75ps*64=4.8ns, 因此當時鐘頻率低于200MHZ( 周期為5ns) 時, 不可能檢測到兩個跳變沿, 此時必須采取適當的措施來獲得數據延遲量。當64 階延遲量完成時只檢測到一個跳變沿時, 我們認為數據延遲量為檢測到第一個跳變沿時的延遲量加上16, 因為四分之一個200MHZ 時鐘周期大約為16階延遲量( 16*75=1.2ns) 即:

延遲后的數據經過IDDR 觸發器分別得到上升沿對應的數據和下降沿對應的數據, 然后再通過異步查找表FIFO 使讀進

FPGA 的數據與FPGA 內部時鐘同步方便用戶使用。

3 控制器實驗結果及結論

該DDR 控制器設計總共占用751 個4 輸入LUT, 占總LUT 資源的2%。另外, 設計還使用了3 個DCM。DDR 控制器在

Xilinx ISE8.1i 編程環境下實現, 結合ModelSim SE6.1b 進行仿真。板上調試時時鐘選為100MHZ, 經測試數據傳輸及捕獲準確無誤。

經實驗驗證該DDR 控制器工作穩定可靠、確實可行, 占用邏輯資源較少, 且具有較高的可移植性, 以及簡單方便的用戶接

口。該DDR 控制器經過簡單的修改就可以控制其他型號的DDR SDRAM芯片, 因此可以極大地提高信號處理板的存儲容

量, 很好的用于高速信號處理系統中。

電子發燒友App

電子發燒友App

評論