首次流片成功取決于整個系統(tǒng)硬件和相關(guān)軟件的驗證,有些公司提供的快速原型生成平臺具有許多調(diào)試功能,但這些平臺的價格非常高。

2011-01-18 12:23:16 1361

1361

RTL代碼驗證工作上,另外軟件的相關(guān)開發(fā)工作,也會在得到芯片前開始,這2方面都需要借助FPGA原形來模擬芯片的行為,幫助硬件開發(fā)和軟件開發(fā)者,共同提升工作效率。 FPGA原型在數(shù)字芯片設(shè)計中,基本是必不可少的,原因非常明顯,相比用

2020-12-30 12:00:13 3715

3715 什么是FPGA原型?? FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能

2022-07-19 16:27:29 2400

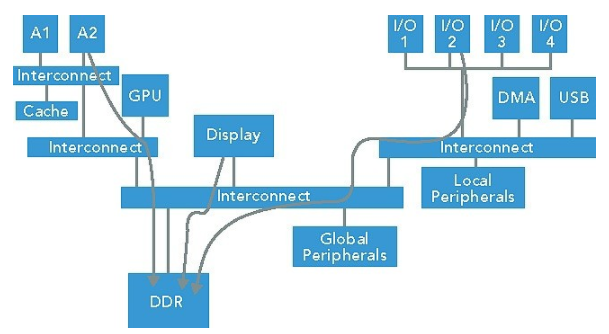

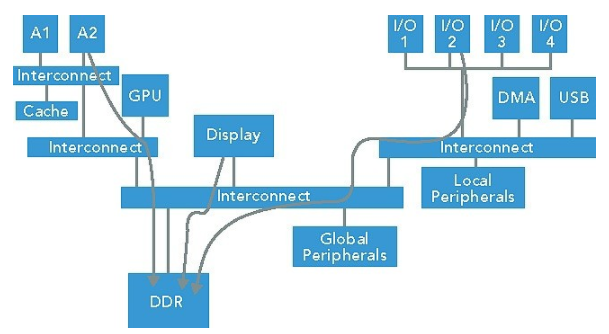

2400 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規(guī)模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣:

2023-04-25 11:15:20 2534

2534

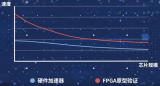

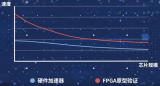

FPGA原型在數(shù)字芯片設(shè)計中非常重要,因為相比用仿真器,或者加速器等來跑仿真,FPGA的運行速度,更接近真實芯片,可以配合軟件開發(fā)者來進行底層軟件的開發(fā)。這一流片前的軟硬件的協(xié)同開發(fā),是其最不可替代的地方。

2023-05-10 10:44:00 11197

11197

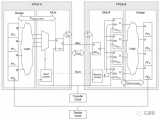

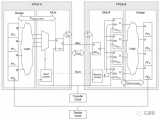

多片FPGA之間的互連,經(jīng)常提到多路復用的概念,也經(jīng)常提到TDM的概念,正確理解多路復用在多片FPGA原型驗證系統(tǒng)中的機理,尤其是時序機制,對于我們正確看待和理解多片FPGA原型系統(tǒng)的性能有很好的促進作用。下圖是一個使用多路復用器后接采樣FF的多路復用解決方案的示例。

2023-06-06 10:04:35 2286

2286

引言隨著電子設(shè)計自動化(EDA)驗證工具的重要性日益增加,開發(fā)者們開始尋求減少流片成本和縮短開發(fā)周期的方法。其中,使用可編程邏輯芯片(FPGA)來構(gòu)建有效的驗證流程成為一種流行的解決方案,這種

2024-06-06 08:23:48 2007

2007

國微思爾芯發(fā)布3億門原型驗證系統(tǒng),采用業(yè)界最高容量的 Intel? Stratix? 10 GX 10M FPGAs。

2020-09-08 10:56:20 1403

1403 Tape Out并回片后都可以進行驅(qū)動和應(yīng)用的開發(fā)。目前ASIC的設(shè)計變得越來越大,越來越復雜,單片FPGA已不能滿足原型驗證要求,多片FPGA驗證應(yīng)運而生。本文我就將與大家探討FPGA原型驗證的幾個經(jīng)典挑戰(zhàn)性場景,(具體應(yīng)對的辦法,請戳原文。)容量限制和性能要求

2020-08-21 05:00:12

的費用持續(xù)上升。一次失敗的ASIC流片將會推遲數(shù)個月的上市時間。誰愿意承擔簽字的責任呢? 一些BUG通過仿真和Emulation是抓不到的。傳統(tǒng)的驗證方法認為設(shè)計的功能符合功能定義就是對的。 但功能定義到底對不對呢?唯一的辦法就是建立一個真實的硬件:原型。

2019-07-11 08:19:24

with Tcl...........................................953.9 Gate Clock 處理............................................993.10 多片 FPGA 驗證

2015-09-18 15:26:25

ASIC設(shè)計-FPGA原型驗證

2020-03-19 16:15:49

生成的代碼加以全面分析。 使用FPGA在環(huán)仿真加速驗證 使用系統(tǒng)級仿真和HDL協(xié)同仿真驗證DDC算法之后,便可以立即在FPGA目標平臺上部署DDC算法。對算法執(zhí)行基于FPGA的驗證(也稱為FPGA在環(huán)仿真

2018-09-04 09:26:53

。HAPS-51采用FPGA陣列Xilinx Virtex-5 LX330和板上存儲器,加快了ASIC驗證的速度。先前的HAPS系統(tǒng)在存儲器存取方面采用子板,而最新的HAPS-51則采用位于板上并靠近

2018-11-20 15:49:49

測試平臺,采用系統(tǒng)級指標分析HDL實現(xiàn) 方案;通過FPGA在環(huán)仿真加速驗證(圖1)。為什么在FPGA上建立原型?在FPGA上建立算法原型可以增強工程師的信心,使他們相信自己的算法在實際環(huán)境中的表現(xiàn)能夠

2020-05-04 07:00:00

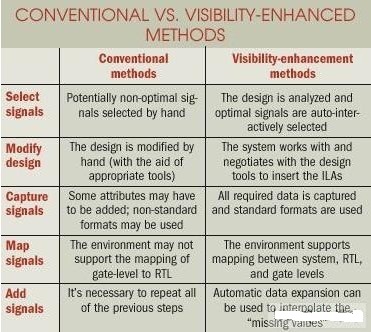

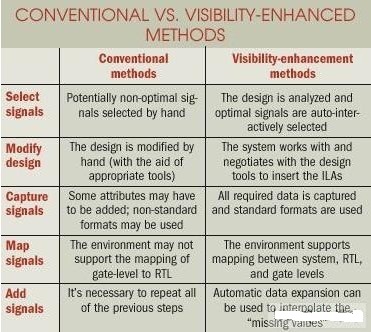

采用基于現(xiàn)場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰(zhàn)之一在于當原型系統(tǒng)未能發(fā)揮期望的性能時了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計的一個關(guān)鍵因素是難以觀察內(nèi)部信號。 目前的頂級

2019-07-12 06:38:15

NoC為FPGA設(shè)計提供了哪些優(yōu)勢?NoC在FPGA內(nèi)部邏輯互連中發(fā)揮的作用是什么?如何利用片上高速網(wǎng)絡(luò)創(chuàng)新地實現(xiàn)FPGA內(nèi)部超高帶寬邏輯互連?

2021-06-17 11:35:28

的設(shè)計和驗證的復雜性需求。隨著原型技術(shù)在設(shè)計分割以及多 FPGA 聯(lián) 合調(diào)試領(lǐng)域的進步,基于FPGA 的原型系統(tǒng)不僅可以滿足百萬門級的設(shè)計需求,還可以實現(xiàn)設(shè)計規(guī)模高達15 億門。基 于FPGA

2018-08-07 09:41:23

用基于現(xiàn)場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰(zhàn)之一在于當原型系統(tǒng)未能發(fā)揮期望的性能時了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計的一個關(guān)鍵因素是難以觀察內(nèi)部信號。 目前的頂級

2020-07-07 09:08:34

采用基于現(xiàn)場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰(zhàn)之一在于當原型系統(tǒng)未能發(fā)揮期望的性能時了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計的一個關(guān)鍵因素是難以觀察內(nèi)部信號。

2019-10-14 07:07:06

為什么不能采用基于現(xiàn)場可編程門陣列(FPGA)的原型?驗證團隊面臨的最大挑戰(zhàn)之一在于當原型系統(tǒng)未能發(fā)揮期望的性能時了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計的一個關(guān)鍵因素是難以觀察內(nèi)部信號。

2019-08-13 07:45:06

請教大神如何利用FPGA實現(xiàn)原型板原理圖的驗證?

2021-04-29 06:57:34

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經(jīng)成為ASIC芯片設(shè)計中重要的驗證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設(shè)計,并給出驗證結(jié)果。

2019-06-18 07:43:00

原型驗證環(huán)境概述一套完整的RFID系統(tǒng)是由閱讀器(Reader)、電子標簽芯片(Tag)也就是所謂的應(yīng)答器(Transponder)及應(yīng)用軟件三部分組成。電子標簽芯片的FPGA原型驗證環(huán)境也是一套完整

2019-05-29 08:03:31

隨著大容量高速度的FPGA的出現(xiàn),在流片前建立一個高性價比的原型驗證系統(tǒng)已經(jīng)成為縮短系統(tǒng)級芯片(SoC)驗證時間,提高首次流片成功率的重要方法。本文著重討論了用FPGA建

2009-09-11 15:50:09 16

16 FPGA驗證是基于VHDL的VLSI設(shè)計中非常重要的一個環(huán)節(jié)。用戶設(shè)計的電子系統(tǒng)首先必須是可綜合的,綜合之后再通過FPGA原型驗證,即可在物理層面對用戶設(shè)計完成實物驗證。通過FPGA驗證

2010-07-12 19:13:59 28

28 比較了多種DSP芯片的互連性能,給出了一種簡單高性能DSP網(wǎng)絡(luò)結(jié)構(gòu)。針對構(gòu)成DSP網(wǎng)絡(luò)通訊接口的鏈路口,分析其基本特點,并且提出了在FPGA中實現(xiàn)的設(shè)計原理。最后給出了設(shè)計仿真圖和

2010-07-27 16:46:46 24

24 隨著SoC設(shè)計復雜度的提高,驗證已成為集成電路設(shè)計過程中的瓶頸,而FPGA技術(shù)的快速發(fā)展以及良好的可編程特性使基于FPGA的原型驗證越來越多地被用于SoC系統(tǒng)的設(shè)計過程。本文討論

2010-11-11 16:00:07 35

35 富士通微電子正式采用亞科鴻禹FPGA原型驗證平臺

富士通微電子(上海)有限公司近日赴北京亞科鴻禹電子有限公司,圓滿完成了對StarFire-V530原型驗證板的測試驗收工作。

2010-02-24 08:50:34 1027

1027 基于FPGA的可層疊組合式SoC原型系統(tǒng)設(shè)計

在復雜片上系統(tǒng)SoC的設(shè)計過程中,驗證仿真是影響項目進度的關(guān)鍵因素。隨著芯片生產(chǎn)和制造工藝的提高,SoC設(shè)計的規(guī)模、復雜

2010-01-08 11:18:42 1204

1204

為提高芯片驗證與測試的可靠性,針對片上網(wǎng)絡(luò)核心芯片的結(jié)構(gòu)特點,設(shè)計出一種基于宿主機/目標機通信模式的測試系統(tǒng)。重點描述了測試系統(tǒng)軟硬件的設(shè)計與實現(xiàn),并采用Stratix系列FPGA芯片進行原型測試和驗證。實驗結(jié)果表明,該系統(tǒng)可對芯片的復位、實現(xiàn)功能及

2011-01-15 15:46:29 31

31 《 FPGA的原型開發(fā)方法手冊》(FPMM),這是一本介紹如何使用 FPGA 作為平臺進行片上系統(tǒng)(SoC)開發(fā)的實用指南。FPMM 收錄了眾多公司的設(shè)計團隊在設(shè)計和驗證方面的寶貴經(jīng)驗,

2011-03-14 09:06:50 1099

1099 介紹了一種基于SRAM技術(shù)的FPGA可編程邏輯器件的編程方法,能在系統(tǒng)復位或上電時自動對器件編程。有效地解決了基于SRAM的FPGA器件掉電易失性問題,針對當前系統(tǒng)規(guī)模的日益增大,本文提出了一種用單片機對多片FPGA自動加載配置的解決方案.

2011-03-15 16:41:22 21

21 HAPS-600系列以高達8100萬ASIC門的容量為各種基于FPGA的更大型的原型驗證項目提供高靈活性和可擴展性。

2011-03-21 10:28:38 1088

1088 新思科技有限公司推出HAPS-600 系列,這是其HAPS系列基于現(xiàn)場可編程門陣列(FPGA)原型驗證系統(tǒng)中容量最高的一款產(chǎn)品

2011-03-22 09:32:15 1860

1860 對ASIC設(shè)計進行FPGA原型驗證時,由于物理結(jié)構(gòu)不同,ASIC的代碼必須進行一定的轉(zhuǎn)換后才能作為FPGA的輸入。 現(xiàn)代集成電路設(shè)計中,芯片的規(guī)模和復雜度正呈指數(shù)增加。尤其在ASIC設(shè)計流程中

2011-03-25 15:16:20 108

108 S2C日前宣布其Verification Module技術(shù)(專利申請中)已可用于其基于 Xilinx 的FPGA原型驗證系統(tǒng)中。V6 TAI Verification Module可以實現(xiàn)在FPGA原型驗證環(huán)境和用戶驗證環(huán)境之間高速海量數(shù)據(jù)傳輸。用戶

2011-09-20 09:07:58 1622

1622 新思科技公司日前宣布了一種集成化混合原型驗證解決方案,它將Synopsys的Virtualizer虛擬原型驗證和Synopsys基于FPGA的HAPS原型驗證結(jié)合在一起

2012-06-07 11:26:30 1373

1373 新思科技公司日前宣布:該公司推出其Synopsys HAPS?-70系列基于FPGA的原型驗證系統(tǒng),從而擴展了其HAPS產(chǎn)品線以應(yīng)對系統(tǒng)級芯片(SoC)設(shè)計的不斷增加的規(guī)模及復雜度。

2012-11-27 21:51:39 1766

1766 Workbench是一種軟件解決方案,在整個片上系統(tǒng)設(shè)計過程對互連進行周期精確的性能分析,能在關(guān)鍵流量狀況下快速識別出設(shè)計問題,并幫助用戶改進器件性能、加快產(chǎn)品上市。Interconnect

2013-11-07 09:34:14 1477

1477 新增的8種模塊使設(shè)計者更專注于產(chǎn)品差異化, 并加快產(chǎn)品上市時間 S2C 公司,業(yè)內(nèi)領(lǐng)先的 FPGA 快速原型驗證系統(tǒng)供應(yīng)商, 今日發(fā)布8種新的 FPGA 原型驗證接口子卡和配件,其旨在加快發(fā)展片上

2017-02-08 06:50:11 1106

1106

如今,設(shè)計人員使用兩種相對獨立的方法進行 SoC 原型驗證:以事務(wù)級模型為基礎(chǔ)的虛擬原型驗證和基于 FPGA 的原型驗證。 虛擬原型驗證執(zhí)行快速的 TLM,并可提供更高效的調(diào)試和分析方案,非常適合

2017-02-08 14:32:11 572

572 此方案可簡化,無電纜的設(shè)計分割,最多允許四個用戶同時使用。S2C公司,業(yè)內(nèi)領(lǐng)先的 FPGA 快速原型驗證系統(tǒng)供應(yīng)商,發(fā)布了適用于超大規(guī)模設(shè)計的基于賽靈思Virtex UltraScale(VU

2018-06-29 08:09:00 6021

6021 設(shè)計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協(xié)同驗證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗證

2017-11-17 03:06:01 21449

21449

設(shè)計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協(xié)同驗證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗證

2017-11-17 03:06:01 5210

5210

利用Xilinx的FPGA設(shè)計了一個FPGA原型驗證平臺,用于無源高頻電子標簽芯片的功能驗證。主要描述了驗證平臺的硬件設(shè)計,解決了由分立元件實現(xiàn)模擬射頻前端電路時存在的問題,提出了FPGA器件選型

2017-11-18 08:42:22 4347

4347

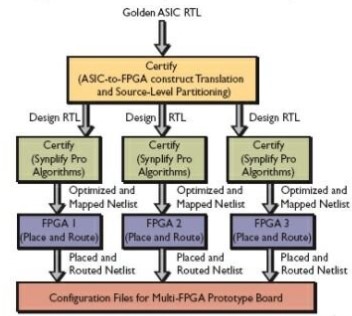

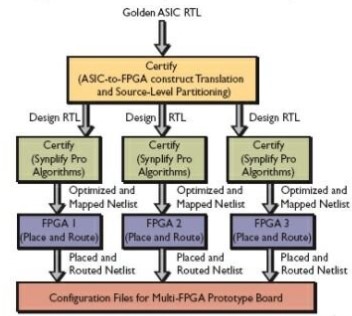

在不太遙遠的過去,對ASIC設(shè)計團隊而言,在這類情況下主要的解決方案就是在內(nèi)部建立他們自己的定制多個FPGA的原型開發(fā)板。然而,今天,使用現(xiàn)成的多個FPGA原型開發(fā)板——例如,由Synplicity

2019-05-16 08:07:00 3784

3784

采用基于現(xiàn)場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰(zhàn)之一在于當原型系統(tǒng)未能發(fā)揮期望的性能時了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計的一個關(guān)鍵因素是難以觀察內(nèi)部信號。

2019-01-08 08:16:00 2517

2517

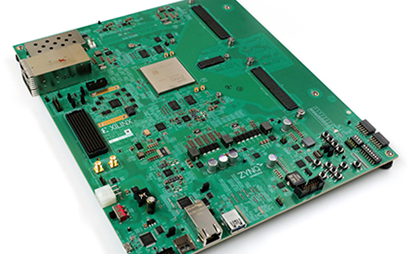

以及ZYNQ 7020模組。XCVU13P主器件具有極其豐富的FPGA可編程邏輯資源,提供了強悍的算法原型驗證能力。同時平臺板載的ZYNQ 7020器件可用于系統(tǒng)管理并增強系統(tǒng)的靈活性。該平臺提供有

2020-05-19 10:50:05 3371

3371 ,加速超大規(guī)模設(shè)計驗證,提升設(shè)計性能 完整的原型驗證解決方案包括多FPGA深度調(diào)試,系統(tǒng)級協(xié)同建模及 90 多種應(yīng)用接口子板庫 2020年10月22日,國微思爾芯,一站式EDA驗證解決方案專家,正式推出面向超大規(guī)模SoC原型市場的ProdigyTM S7-19P原型驗證系統(tǒng)。 S7-19P提供單、

2020-10-23 15:02:18 3161

3161 流片成功無疑是所有芯片開發(fā)者的共同目標,否則耗時持久的努力和流片所產(chǎn)生的高昂成本都將付諸東流。基于FPGA的原型驗證是芯片流片前非常重要的一個步驟,不僅可以提高流片成功率,還可加速軟件的開發(fā)速度。

2022-01-19 08:54:14 3208

3208 其次,部分FPGA開發(fā)板也被用在IP和小型芯片設(shè)計的開發(fā)驗證場景。這部分開發(fā)板配備大容量的FPGA芯片,甚至是單板配備多片FPGA芯片來適應(yīng)開發(fā)驗證場景,一般由用戶自己負責手工實現(xiàn)從設(shè)計到FPGA功能原型的流程。

2022-04-28 09:38:33 3563

3563 電路,是可編程的邏輯陣列。FPGA 的基本結(jié)構(gòu)包括可編程輸入輸出單元、基本可編程邏輯單元、數(shù)字時鐘管理模塊、嵌入式塊RAM、豐富的布線資源、內(nèi)嵌專用硬核,以及底層內(nèi)嵌功能單元。 ? 圖1? 某FPGA的基本邏輯單元?? 市售常見的基于FPGA的平臺產(chǎn)品包括FPGA開發(fā)板、FPGA原型驗證系統(tǒng)。既然

2022-04-28 14:16:59 4031

4031

從系統(tǒng)的特性上看,FPGA 原型系統(tǒng)支持多FPGA、自動分割;性能較高的情況下運行系統(tǒng)軟件;仿真加速器的超大容量可以放全芯片的設(shè)計,進行全芯片的系統(tǒng)功能/性能/功耗驗證。

2022-05-25 09:35:13 10849

10849 面對持續(xù)不斷的上市時間壓力和日益復雜的 SoC 設(shè)計,很難找到不想從設(shè)計周期中縮短時間的工程師。特別是在高級節(jié)點,驗證 SoC 互連已成為一個耗時的步驟。但是,工具現(xiàn)在可以高效且有效地執(zhí)行周期精確的性能分析和互連驗證。

2022-06-14 10:12:17 3131

3131

FPGA(Field Programmable Gate Array)原型驗證,基于其成本適中、速率接近真實系統(tǒng)環(huán)境等優(yōu)點,受到了驗證工程師的青睞。正是由于廣泛豐富的應(yīng)用場景,FPGA 原型系統(tǒng)上

2022-09-19 13:40:03 1200

1200

在現(xiàn)代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應(yīng)該是非常熟悉的場景了。

2023-03-28 09:33:16 2001

2001 我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-03-28 14:11:15 1690

1690 FPGA原型驗證在數(shù)字SoC系統(tǒng)項目當中已經(jīng)非常普遍且非常重要,但對于一個SoC的項目而言,選擇合適的FPGA原型驗證系統(tǒng)顯的格外重要

2023-04-03 09:46:45 2074

2074 當SoC系統(tǒng)的規(guī)模很大的時候,單片FPGA驗證平臺已經(jīng)無法容納這么多容量,我們將采取將SoC設(shè)計劃分為多個FPGA的映射。

2023-04-06 11:20:48 1400

1400 如果SoC設(shè)計規(guī)模小,在單個FPGA內(nèi)可以容納,那么只要系統(tǒng)中的FPGA具有所SoC所設(shè)計需要時鐘的數(shù)量

2023-04-07 09:42:57 1705

1705 FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2023-04-10 09:23:29 2664

2664 FPGA原型驗證平臺系統(tǒng)靈活性主要體現(xiàn)在其外部連接表現(xiàn)形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統(tǒng)。

2023-04-11 09:50:03 1543

1543 FPGA原型驗證平臺系統(tǒng)靈活性主要體現(xiàn)在其外部連接表現(xiàn)形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統(tǒng)。

2023-04-11 09:50:37 936

936 多片FPGA的原型驗證系統(tǒng)的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數(shù)量受封裝技術(shù)的限制

2023-04-12 10:14:42 1558

1558 FPGA與FPGA之間互連對信號延遲的影響,兩片FPGA的IO之間每一個額外的過渡,例如連接器、焊點甚至板內(nèi)通孔,都會增加一些阻抗,從而降低信號質(zhì)量,并增加信號之間串擾的概率。然而,經(jīng)過仔細分析,發(fā)現(xiàn)這并不是一個想象中的大問題。主要矛盾是FPGA互連線的影響。

2023-04-16 10:21:51 1333

1333 FPGA原型驗證系統(tǒng)要盡可能多的復用SoC相關(guān)的模塊,這樣才是復刻SoC原型的意義所在。

2023-04-19 09:08:15 1953

1953 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規(guī)模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣。

2023-05-04 16:21:34 1331

1331

多片FPGA原型驗證系統(tǒng)的拓撲連接方式各不相同,理想的多片FPGA原型驗證系統(tǒng)應(yīng)該可以靈活配置,可以使用其相應(yīng)的EDA工具

2023-05-08 11:51:40 891

891

當SoC的規(guī)模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統(tǒng)。

2023-05-10 10:15:16 689

689 FPGA原型驗證的原理是將芯片RTL代碼綜合到FPGA上來驗證芯片的功能。對于目前主流行業(yè)應(yīng)用而言,芯片規(guī)模通常達到上億門甚至數(shù)十億門,一顆FPGA的容量難以容納下芯片的所有邏輯功能。

2023-05-18 12:52:52 1145

1145

假如給定FPGA內(nèi)的時鐘沒有正確運行,那么我們多片FPGA系統(tǒng)的整體將不能同時啟動,這將有可能是致命的。

2023-05-22 09:21:24 621

621

當SoC的規(guī)模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統(tǒng)。

2023-05-23 15:31:10 1015

1015 如果SoC設(shè)計規(guī)模小,在單個FPGA內(nèi)可以容納,那么只要系統(tǒng)中的FPGA具有所SoC所設(shè)計需要時鐘的數(shù)量

2023-05-23 15:46:24 1420

1420

FPGA原型驗證系統(tǒng)要盡可能多的復用SoC相關(guān)的模塊,這樣才是復刻SoC原型的意義所在。

2023-05-23 16:50:34 1109

1109

我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-05-30 11:10:27 1358

1358

在現(xiàn)代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應(yīng)該是非常熟悉的場景了。

2023-05-30 15:04:06 2103

2103

多片FPGA之間的互連,經(jīng)常提到多路復用的概念,也經(jīng)常提到TDM的概念

2023-06-06 10:07:37 852

852

綜合工具的任務(wù)是將SoC設(shè)計映射到可用的FPGA資源中。自動化程度越高,構(gòu)建基于FPGA的原型的過程就越容易、越快。

2023-06-13 09:27:06 879

879

當SoC系統(tǒng)的規(guī)模很大的時候,單片FPGA驗證平臺已經(jīng)無法容納這么多容量,我們將采取將SoC設(shè)計劃分為多個FPGA的映射。

2023-06-19 15:42:08 1081

1081 引言Preface如何快速便捷的完成巨型原型驗證系統(tǒng)的組網(wǎng),并監(jiān)測系統(tǒng)的連通性及穩(wěn)定性?如何將用戶設(shè)計快速布局映射到參與組網(wǎng)的原型驗證系統(tǒng)的每一塊FPGA?隨著用戶設(shè)計規(guī)模的日益增大,傳統(tǒng)基于單片

2022-06-16 10:19:18 1306

1306

剖析》分析了用戶在進行大規(guī)模原型驗證過程中的多FPGA聯(lián)合調(diào)試難題,并介紹了一種新型FPGA原型驗證深度跟蹤調(diào)試解決方案,用于幫助客戶在SoC開發(fā)過程中解決調(diào)試問

2022-06-16 10:16:48 1693

1693

所有形式的原型都為驗證硬件設(shè)計和驗證軟件提供了強大的方法,模型或多或少地模仿了目標環(huán)境。基于FPGA的原型設(shè)計在項目的關(guān)鍵后期階段尤其有益。用戶有幾個原型設(shè)計選項根據(jù)他們的主要需求,可以選擇各種基于軟件和硬件的技術(shù)來原型他們的設(shè)計。

2023-10-11 12:39:41 1808

1808

FPGA原型設(shè)計是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應(yīng)用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2024-01-12 16:13:01 2194

2194 proFPGA是mentor的FPGA原型驗證平臺,當然mentor被西門子收購之后,現(xiàn)在叫西門子EDA。

2024-01-22 09:21:01 3230

3230

FPGA原型驗證流程是確保FPGA(現(xiàn)場可編程門陣列)設(shè)計正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計實現(xiàn)到功能驗證的整個過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 3057

3057 FPGA原型驗證平臺與硬件仿真器在芯片設(shè)計和驗證過程中各自發(fā)揮著獨特的作用,它們之間存在明顯的區(qū)別。

2024-03-15 15:07:03 2340

2340 引言原型驗證是一種在FPGA平臺上驗證芯片設(shè)計的過程,通過在FPGA上實現(xiàn)芯片的設(shè)計原型,使得開發(fā)人員可以在硬件完成之前提前開始軟件開發(fā)和系統(tǒng)驗證。然而,如何快速確保在原型驗證平臺上開發(fā)的軟件能

2024-09-30 08:04:29 1651

1651

近日,新思科技宣布推出全新基于AMD Versal? Premium VP1902自適應(yīng)系統(tǒng)級芯片(SoC)的HAPS?原型驗證系統(tǒng),以此進一步升級其硬件輔助驗證(HAV)產(chǎn)品組合。 此次推出的全新

2025-02-19 17:12:08 1235

1235 西門子的 Veloce proFPGA CS 是一款針對軟件驗證和軟硬件系統(tǒng)集成優(yōu)化的原型系統(tǒng)。它是一款基于 FPGA 的邏輯功能驗證級工具。

2025-02-27 11:48:41 1155

1155 隨著臺積電在 2011年推出第一版 2.5D 封裝平臺 CoWoS、海力士在 2014 年與 AMD 聯(lián)合發(fā)布了首個使用 3D 堆疊的高帶寬存儲(HBM)芯片,先進封裝技術(shù)帶來的片上互連拓撲結(jié)構(gòu)的改變和帶來的集成能力的提升,成為當前片上互連技術(shù)發(fā)展的主要驅(qū)動因素。

2025-05-22 10:17:51 975

975

子,工程師可以從 proFPGA Uno 系統(tǒng)開始進行 IP 或子片上系統(tǒng) (SoC) 的開發(fā),然后將其重復用于完整的 SoC 和專用集成電路 (ASIC)原型設(shè)計。這只需要將 Uno 中的相同

2025-06-30 13:53:59 1694

1694

電子發(fā)燒友App

電子發(fā)燒友App

評論