FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是標配了。從PCI到PCI Express, 從ATA到SATA,從并行ADC接口到JESD204, 從RIO到Serial RIO,…等等,都是在借助SerDes來提高性能。SerDes是非常復雜的數模混合設計,用戶手冊的內容只是描述了森林里面的一棵小樹,并不能夠解釋SerDes是怎么工作的。SerDes怎么可以沒有傳輸時鐘信號?什么是加重和均衡?抖動和誤碼是什么關系?各種抖動之間有什么關系?本篇小文試著從一個SerDes用戶的角度來理解SerDes是怎么設計的, 由于水平有限,一定有不夠準確的地方,希望對剛開始接觸SerDes的工程師有所幫助。

1.????SerDes的價值

1.1并行總線接口

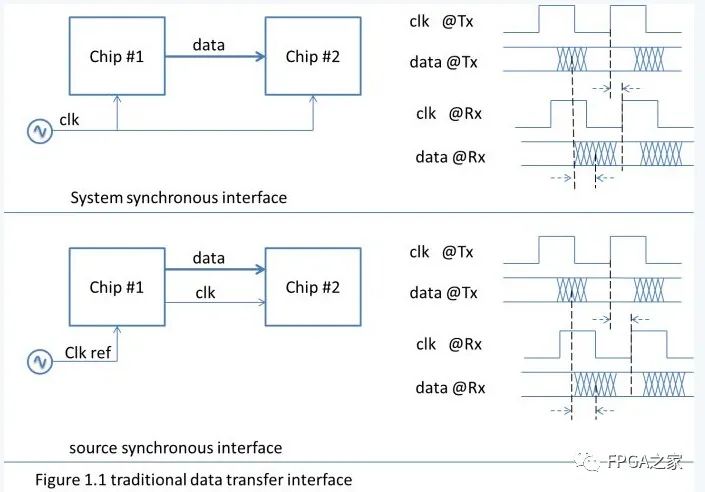

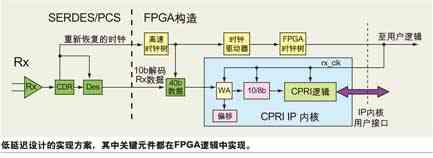

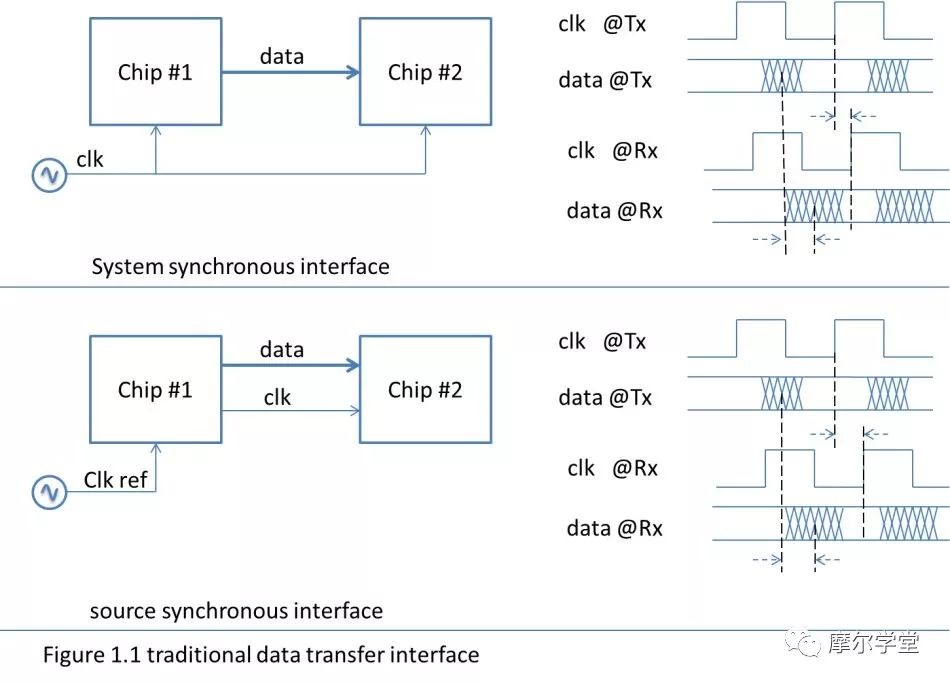

在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。

隨著接口頻率的提高,在系統同步接口方式中,有幾個因素限制了 有效數據窗口寬度 的繼續增加。

l??時鐘到達兩個芯片的傳播延時不相等(clock skew)

l??并行數據各個bit的傳播延時不相等(data skew)

l??時鐘的傳播延時和數據的傳播延時不一致(skew between data and clock)

雖然可以通過在目的芯片(chip #2)內用PLL補償時鐘延時差(clock skew),但是PVT變化時,時鐘延時的變化量和數據延時的變化量是不一樣的。這又進一步惡化了數據窗口。

源同步接口方式中,發送側Tx把時鐘伴隨數據一起發送出去, 限制了clock skew對有效數據窗口的危害。通常在發送側芯片內部,源同步接口把時鐘信號和數據信號作一樣的處理,也就是讓它和數據信號經過相同的路徑,保持相同的延時。這樣PVT變化時,時鐘和數據會朝著同一個方向增大或者減小相同的量,對skew最有利。

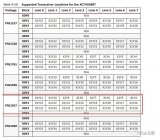

我們來做一些合理的典型假設,假設一個32bit數據的并行總線,??

a)發送端的數據skew = 50 ps????????????????????????---很高的要求

b)pcb走線引入的skew = 50ps??????????????????????---很高的要求

c)時鐘的周期抖動jitter = +/-50 ps???????????????---很高的要求

d)接收端觸發器采樣窗口 = 250 ps?????????????---Xilinx V7高端器件的IO觸發器

可以大致估計出并行接口的最高時鐘 = 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。

利用源同步接口,數據的有效窗口可以提高很多。通常頻率都在1GHz以下。在實際應用中可以見到如SPI4.2接口的時鐘可以高達DDR 700MHz x 16bits位寬。DDR Memory接口也算一種源同步接口,如DDR3在FPGA中可以做到大約800MHz的時鐘。

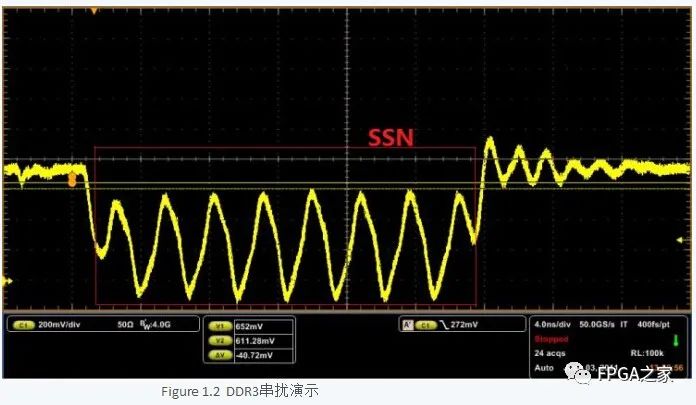

要提高接口的傳輸帶寬有兩種方式,一種是提高時鐘頻率,一種是加大數據位寬。那么是不是可以無限制的增加數據的位寬呢?這就要牽涉到另外一個非常重要的問題-----同步切換噪聲(SSN)。

這里不討論SSN的原理,直接給出SSN的公式 SSN = L *N* di/dt。L是芯片封裝電感,N是數據寬度,di/dt是電流變化的斜率。隨著頻率的提高,數據位款的增加,SSN成為提高傳輸帶寬的主要瓶頸。圖1.2是一個DDR3串擾的例子。圖中低電平的理論值在0V,由于SSN的影響,低電平表現為震蕩,震蕩噪聲的最大值達610mV,因此噪聲余量只有1.5V/2-610mV=140mV。

?????????????????????????????????????????????????????Figure 1.2??DDR3串擾演示

因此也不可能靠無限的提高數據位寬來繼續增加帶寬。一種解決SSN的辦法是使用差分信號替代單端信號,使用差分信號可以很好的解決SSN問題,代價是使用更多的芯片引腳。使用差分信號仍然解決不了數據skew的問題,很大位寬的差分信號再加上嚴格的時序限制,給并行接口帶來了很大的挑戰。

1.2 SerDes接口

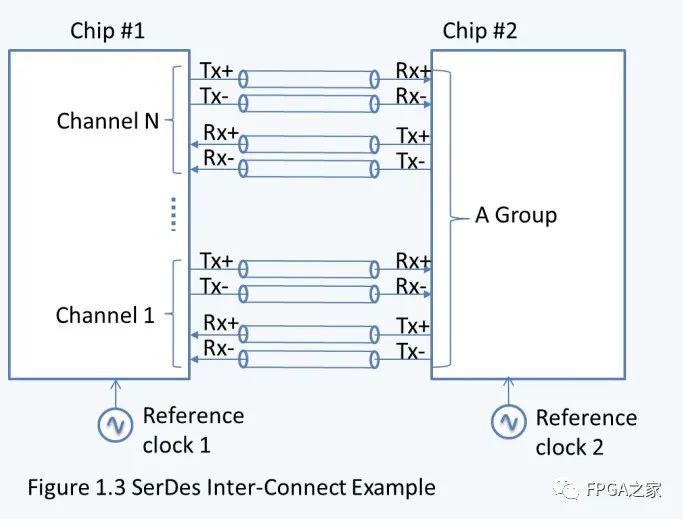

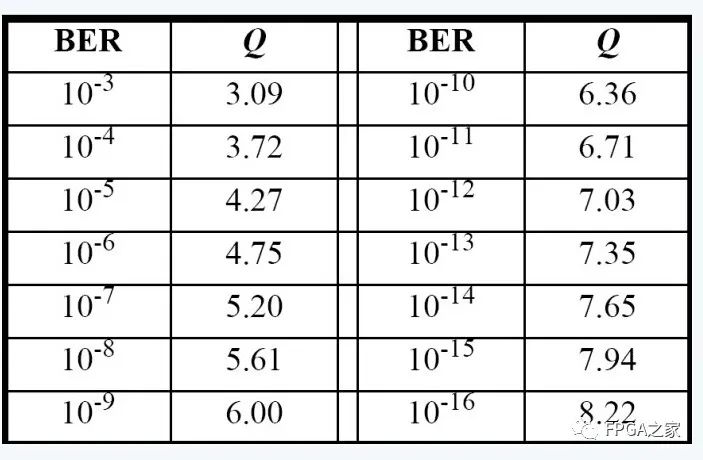

源同步接口的時鐘頻率已經遇到瓶頸,由于信道的非理想(channel)特性,再繼續提高頻率,信號會被嚴重損傷,就需要采用均衡和數據時鐘相位檢測等技術。這也就是SerDes所采用的技術。SerDes(Serializer-Deserializer)是串行器和解串器的簡稱。串行器(Serializer)也稱為SerDes發送端(Tx),(Deserializer)也稱為接收端Rx。Figure1.3是一個N對SerDes收發通道的互連演示,一般N小于4。

?

可以看到,SerDes不傳送時鐘信號,這也是SerDes最特別的地方,SerDes在接收端集成了CDR(Clock Data Recovery)電路,利用CDR從數據的邊沿信息中抽取時鐘,并找到最優的采樣位置。

SerDes采用差分方式傳送數據。一般會有多個通道的數據放在一個group中以共享PLL資源,每個通道仍然是相互獨立工作的。

SerDes需要參考時鐘(Reference Clock),一般也是差分的形式以降低噪聲。接收端Rx和發送端Tx的參考時鐘可以允許幾百個ppm的頻差(plesio-synchronous system),也可以是同頻的時鐘,但是對相位差沒有要求。

作個簡單的比較,一個SerDes通道(channel)使用4個引腳(Tx+/-,Rx+/-), 目前的FPGA可以做到高達28Gbps。而一個16bits的DDR3-1600的線速率為1.6Gbps*16 = 25Gbps,卻需要50個引腳。此對比可以看出SerDes在傳輸帶寬上的優勢。

相比源同步接口,SerDes的主要特點包括:

l ?SerDes在數據線中時鐘內嵌,不需要傳送時鐘信號。

l ?SerDes通過加重/均衡技術可以實現高速長距離傳輸,如背板。

l??SerDes 使用了較少的芯片引腳

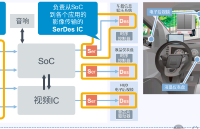

1.3?中間類型

也存在一些介于SerDes和并行接口之間的接口類型,相對源同步接口而言,這些中間類型的接口也使用串行器(Serializer)解串器(Deserializer),同時也傳送用于同步的時鐘信號。這類接口如視頻顯示接口7:1 LVDS等。

2. SerDes結構(architecture)

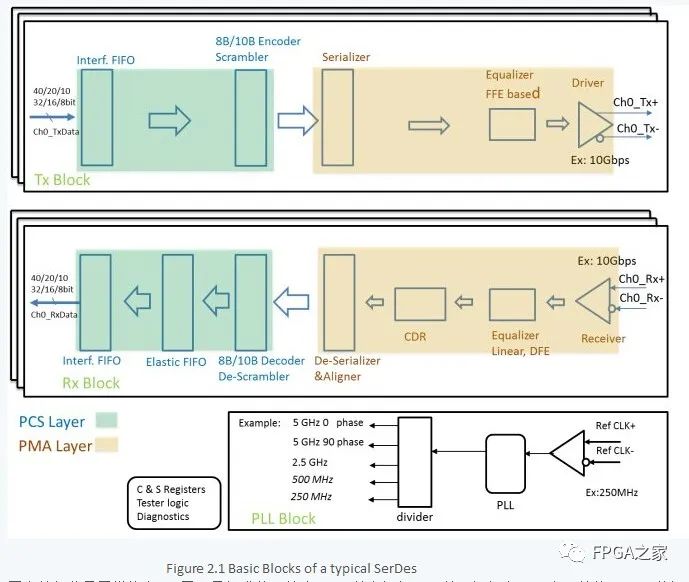

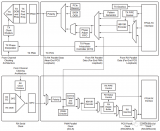

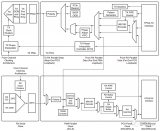

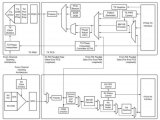

SerDes的主要構成可以分為三部分,PLL模塊,發送模塊Tx,接收模塊Rx。為了方便維護和測試,還會包括控制和狀態寄存器,環回測試,PRBS測試等功能。見圖2.1。

?????????????????????????????????????????????????????Figure 2.1 Basic Blocks of a typical SerDes

圖中藍色背景子模塊為PCS層,是標準的可綜合CMOS數字邏輯,可以硬邏輯實現,也可以使用FPGA軟邏輯實現,相對比較容易被理解。褐色背景的子模塊是PMA層,是數模混合CML/CMOS電路,是理解SerDes去別于并行接口的關鍵,也是本文要討論的內容。

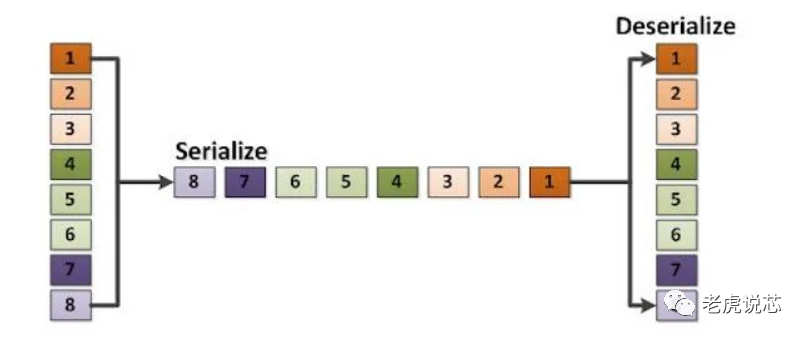

發送方向(Tx)信號的流向: FPGA軟邏輯(fabric)送過來的并行信號,通過接口FIFO(Interface FIFO), 送給8B/10B編碼器(8B/10B encoder)或擾碼器(scambler),以避免數據含有過長連零或者連1。之后送給串行器(Serializer)進行 并->串 轉換。串行數據經過均衡器(equalizer)調理,有驅動器(driver)發送出去。

接收方向(Rx)信號的流向, 外部串行信號由線性均衡器(Linear Equalizer)或DFE (Decision Feedback Equalizer)結構均衡器調理,去除一部分確定性抖動(Deterministic jitter)。CDR從數據中恢復出采樣時鐘,經解串器變為對齊的并行信號。8B/10B解碼器(8B/10B decoder)或解擾器(de-scambler)完成解碼或者解擾。如果是異步時鐘系統(plesio-synchronous system),在用戶FIFO之前還應該有彈性FIFO來補償頻差。

PLL負責產生SerDes各個模塊所需要的時鐘信號,并管理這些時鐘之間的相位關系。以圖中線速率10Gbps為例,參考時鐘頻率250MHz。Serializer/Deserializer至少需要5GHz 0相位時鐘和5GHz 90度相位時鐘,1GHz(10bit并行)/1.25GHz(8bit并行)時鐘等。

一個SerDes通常還要具調試能力。例如偽隨機碼流產生和比對,各種環回測試,控制狀態寄存器以及訪問接口,LOS檢測, 眼圖測試等。

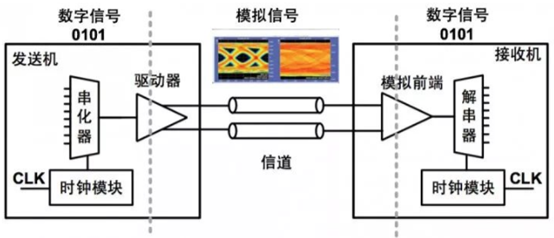

2.1串行器解串器(Serializer/Deserializer)

串行器Serializer把并行信號轉化為串行信號。Deserializer把串行信號轉化為并行信號。一般地,并行信號為8 /10bit或者16/20bit寬度,串行信號為1bit寬度(也可以分階段串行化,如8bit->4bit->2bit->equalizerà1bit以降低equalizer的工作頻率)。采用擾碼(scrambled)的協議如SDH/SONET, SMPTE SDI使用8/16bit的并行寬度,采用8B/10B編碼的協議如PCIExpress,GbE使用10bits/20bits寬度。

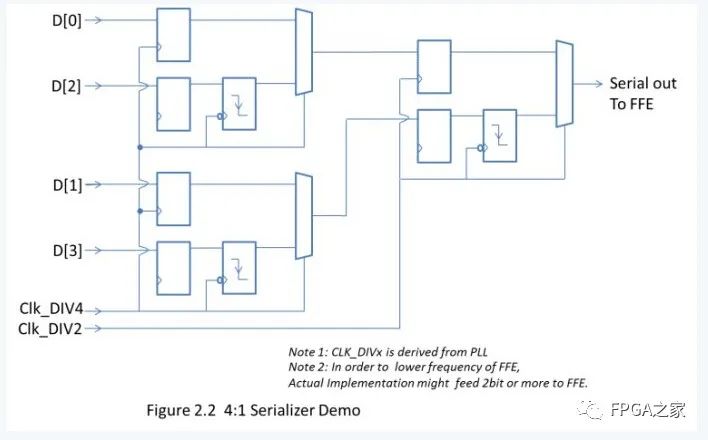

一個4:1的串行器如圖xxx所示。8:1或16:1的串行器采用類似的實現。實現時,為了降低均衡器的工作頻率,串行器會先把并行數據變為2bits,送給均衡器equalizer濾波,最后一步再作2:1串行化,本文后面部分都按1bit串行信號解釋。

?

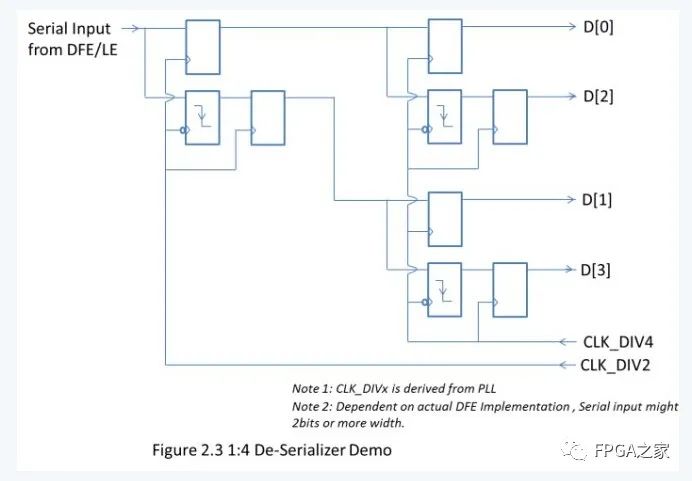

一個1:4的解串器如圖2.3所示,8:1或16:1的解串器采用類似的實現。實現時,為了降低均衡器(DFE based Equalizer)的工作頻率,DFE工作在DDR模式下,解串器的輸入是2bit或者更寬,本文后面部分都按1bit串行信號解釋。

?

Serializer/Deserializer的實現采用雙沿(DDR)的工作方式,利用面積換速度的策略,降低了電路中高頻率電路的比例,從而降低了電路的噪聲。

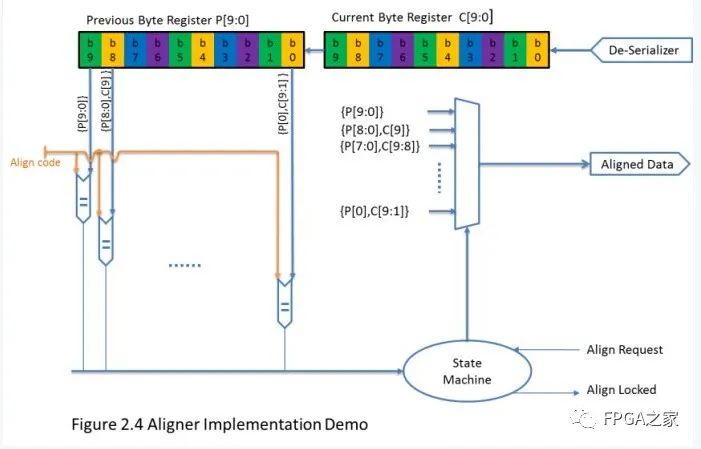

接收方向除了Deserializer之外,一般帶有還有對齊功能邏輯(Aligner)。相對SerDes發送端,SerDes接收端起始工作的時刻是任意的,接收器正確接收的第一個 bit可能是發送并行數據的任意bit位置。因此需要對齊邏輯來判斷從什么bit位置開始,以組成正確的并行數據。對齊邏輯通過在串行數據流中搜索特征碼字(Alignment Code)來決定串并轉換的起始位置。比如8B/10B編碼的協議通常用K28.5(正碼10’b1110000011,負碼10’b0001111100)來作為對齊字。圖2.4為一個對齊邏輯的演示。通過滑窗,逐bit比對,以找到對齊碼(Align-Code)的位置,經過多次在相同的位置找到對齊碼之后,狀態機鎖定位置并選擇相應的位置輸出對齊數據。

?

2.2發送端均衡器( Tx Equalizer)

SerDes信號從發送芯片到達接收芯片所經過的路徑稱為信道(channel),包括芯片封裝,pcb走線,過孔,電纜,連接器等元件。從頻域看,信道可以簡化為一個低通濾波器(LPF)模型,如果SerDes的速率大于信道(channel)的截止頻率,就會一定程度上損傷(distort)信號。均衡器的作用就是補償信道對信號的損傷。

發送端的均衡器采用FFE(Feed forward equalizers)結構,發送端的equalizer也稱作加重器(emphasis)。加重(Emphasis)分為去加重(de-emphasis)和預加重(pre-emphasis)。De-emphasis降低差分信號的擺幅(swing)。Pre-emphasis增加差分信號的擺幅。FPGA大部分使用de-emphasis的方式,加重越強,信號的平均幅度會越小。

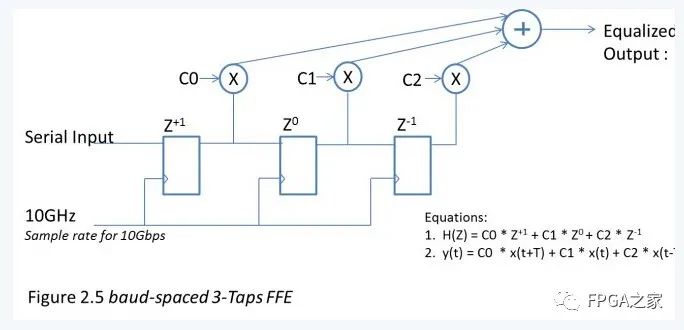

發送側均衡器設計為一個高通濾波器(HPF),大致為信道頻響H(f)的反函數H-1(f),FFE的目標是讓到達接收端的信號為一個干凈的信號。FFE的實現方式有很多,一個典型的例子如圖2.5所示。

?

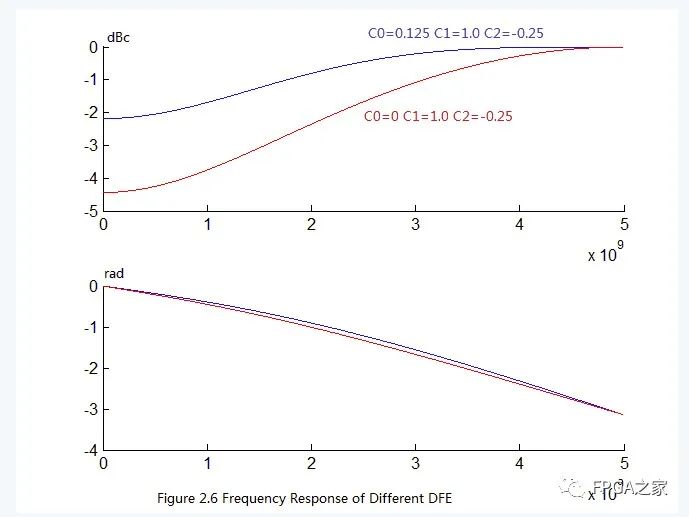

調節濾波器的系數可以改變濾波器的頻響,以補償不同的信道特性,一般可以動態配置。以10Gbps線速率為例,圖2.5為DFE頻率響應演示。可以看到,對于C0=0,C1=1.0,C2=-0.25的配置,5GHz處高頻增益比低頻區域高出4dB,從而補償信道對高頻頻譜的衰減。

?

采樣時鐘的頻率限制了這種FFE最高只能補償到Fs/2(例子中Fs/2=5GHz)。根據采樣定理,串行數據里的信息都包含在5GHz以內,從這個角度看也就足夠了。如果要補償Fs/2以上的頻率,就要求FFE高于Fs的工作時鐘,或者連續時間域濾波器(Continuous Time FFE)。

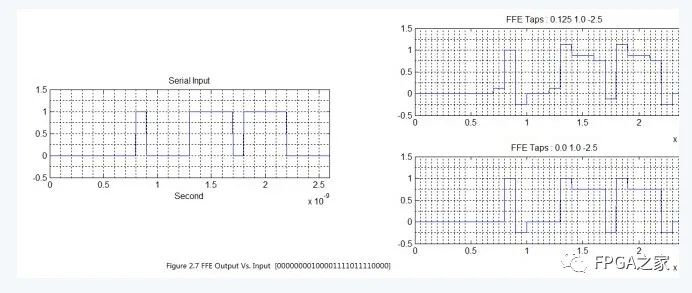

圖2.7為DFE時域濾波效果的演示,以10Gbps線速率為例,一個UI=0.1 nS=100ps。演示的串行數據碼流為二進制[00000000100001111011110000]。

2.3接收端均衡器( Rx Equalizer)

2.3.1?線形均衡器(Linear Equalizer)

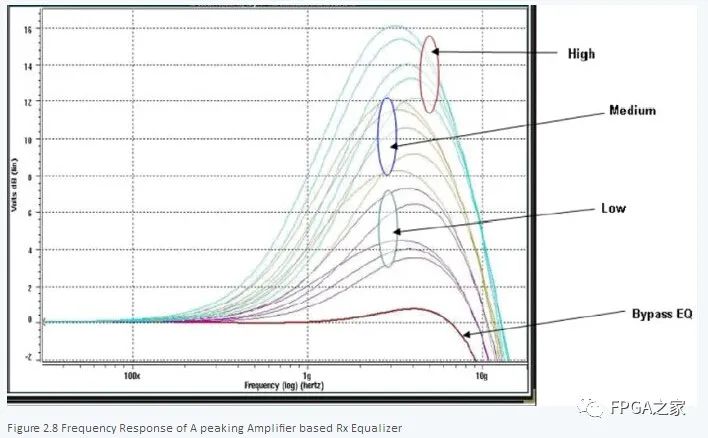

接收端均衡器的目標和發送均衡器是一致的。對于低速(<5Gbps)SerDes,通常采用連續時間域,線性均衡器實現如尖峰放大器(peaking amplifier),?均衡器對高頻分量的增益大于對低頻分量的增益。圖2.8為一個線性均衡器的頻域特性。通常工廠會對均衡特性封裝為數種級別,可以動態設置,以適應不同的信道特性,如High/Med/Low等。

Figure 2.8 Frequency Response of A peaking Amplifier based Rx Equalizer

2.3.2 DFE均衡器(Decision Feedback Equalizer)

對于高速(>5Gbps)SerDes,由于信號的抖動(如ISI相關的確定性抖動)可能會超過或接近一個符號間隔(UI, Unit Interval), 單單使用線性均衡器不再適用。線性均衡器對噪聲和信號一起放大,并沒有改善SNR或者說BER。對于高速SerDes,采用一種稱作DFE (Decision Feedback Equalizer)的非線性均衡器。DFE通過跟蹤過去多個UI的數據(history bits)來預測當前bit的采樣門限。DFE只對信號放大,不對噪聲放大,可以有效改善SNR。

圖2.9演示了一個典型的5階DFE。接收的串行數據由比較器(slicer)來判決0或者1,然后數據流由一個濾波器來預測碼間干擾(ISI),再從輸入的原始信號中減掉碼間干擾(ISI),從而的到一個干凈的信號。為了讓DFE均衡器的電路工作在電路線形范圍內,串行信號先經過VGA自動控制進入DFE的信號幅度。

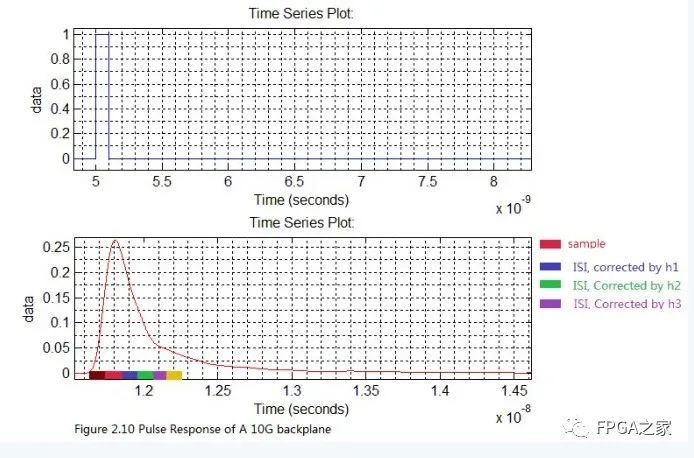

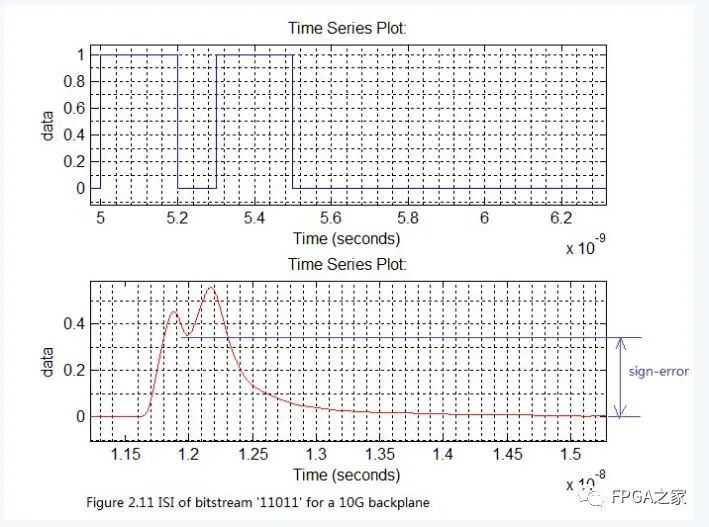

為了理解DFE的工作原理,先來看一個10Gbps背板的脈沖響應,這個背板模型是matlab給出的一個基于實測的模型,具有典型特性。

?

圖2.10中,一橫格代表一個UI的時間。可以看出,一個UI( 0.1nS = 1/10GHz )的脈沖信號,通過背板后,泄漏到前后多個相鄰的UI里面,從而對其他UI的數據產生干擾。采樣點后面的干擾叫做post-cursor干擾,采樣點前面的叫做pre-cursor干擾。DFE的第一個系數 h1(此例中0.175)矯正第一個post-cursor, 第二個系數 h2(此例中0.075)矯正第二個post-cursor。DFE的階數越多,能夠校正的post-cursor也越多。

?

用上述的背板傳輸一個11011的碼流,由于post-cursor和pre-cursor的泄漏,如果沒有均衡,將會導致’0’不能識別,見圖2.11。假定有一個2階的DFE,?那么‘0’bit處的幅度應該減去第一個’1’bit的h2,第二個’1’bit的h1,?得到0.35-0.075-0.175 =0.1,?足夠被識別為0。

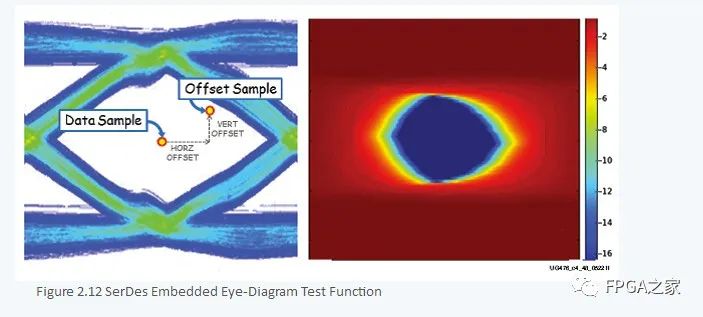

可見,DFE計算歷史bits的post-cursor干擾,在當前bit中把干擾減去,從而得到干凈的信號。由于DFE只能能夠校正post-cursor ISI,?所以DFE前面一般會帶有LE。只要DFE的系數接近信道(channel)的脈沖相應,就可以到的比較理想的結果。但是信道是一個時變的媒介,比如溫度電壓工藝的慢變化等因素會改變信道channel的特性。因此DFE的系數需要自適應算法,自動撲獲和跟隨信道的變化。DFE系數自適應算法非常學術,每個廠商的算法都是保密的,不對外公布。對于NRZ碼,典型的算法準則是基于sign-error驅動的算法。Sign-error是均衡后信號的幅度和期望值的誤差,算法以sign-error均方差最小為優化目標,逐次優化h1/h2/h3…。因為sign-error和采樣位置是耦合在一起相互影響,因此也可以sign-error和眼圖寬度兩個準則為目標進行DFE系數的預測。也因此,采用DFE結構的SerDes通常都會帶有內嵌眼圖測試電路,如圖2.9所示。眼圖測試電路通過垂直方向上平移信號的幅度,水平方向上平移采樣位置,計算每一個平移位置上的誤碼率BER,從而得到每一個偏移位置與誤碼率關系的”眼圖”,見圖2.12。

??Figure 2.12 SerDes Embedded Eye-Diagram Test Function

2.4時鐘數據恢復(CDR)

CDR的目標是找到最佳的采樣時刻,這需要數據有豐富的跳變。CDR有一個指標叫做 最長連0或連1長度 容忍(Max Run Length或者Consecutive Identical Digits)能力。如果數據長時間沒有跳變,CDR就無法得到精確的訓練,CDR采樣時刻就會漂移,可能采到比真實數據更多的1或者0。而且當數據重新恢復跳變的時,有可能出現錯誤的采樣。比如有的CDR采用PLL實現,如果數據長時間停止跳變,PLL的輸出頻率就會漂移。實際上,SerDes上傳輸的數據要么利用加擾,要么利用編碼的方法來保證Max Run Length在一定的范圍內。

l ?8B/10B編碼的方法可以保證Max Run Length不超過5個UI。

l??64B/66B編碼的方法可以保證Max Run Length不超過66個UI

l??SONET/SDH加擾得方法可以保證Max Run Length不超過80個UI(BER<10^-12)

在點到點的連接中,大部分SerDes協議采用連續模式(continuous-mode),線路上數據流是持續而沒有中斷的。在點到多點的連接中,往往采用突發模式(burst-mode)如PON。很顯然Burst-Mode對SerDes鎖定時間有苛刻的要求。

Continuous-Mode的協議如SONET/SDH則要求容忍較長的連0, 而且對CDR的抖動傳輸性能也有嚴格的要求(因為loop timing)。

如果收(Rx)發(Tx)是異步模式(asynchronous mode),或者頻譜擴展(SSC)應用中,則要求CDR有較寬的相位跟蹤范圍以跟蹤Rx/Tx頻率差。

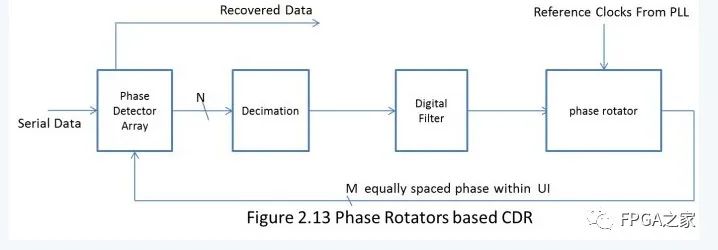

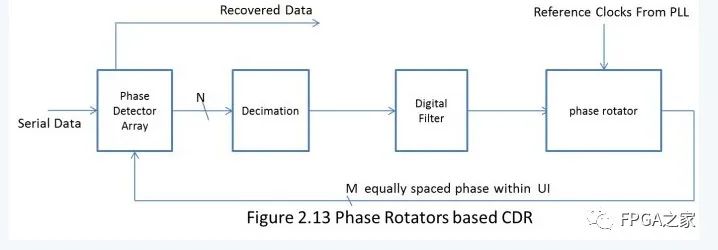

根據應用場景的不同需求,CDR的實現也有非常多種架構。FPGA SerDes常常采用的基于數字PLL的CDR,和基于相位插值器的CDR。這兩種CDR在環路中采用數字濾波器,相對模擬charge pump加模擬濾波器的結構更節省面積。

圖2.13是基于相位插值器的CDR。鑒相器陣列對輸入的串行數據與M個等相位間隔的時鐘在多個UI的跨度上進行相位比較,得到多個UI跨度上的相位誤差信號。相位誤差信號的頻率很高,寬度也很寬,經過抽取器降速并平滑后,送給數字濾波器。數字濾波器的性能會影響環路的帶寬,穩定性,反應速度等。經數字濾波器平滑后的誤差信號送給相位插值器(phase rotators)修正時鐘相位。最終環路鎖定時,理論上相位誤差為零,90度偏移的時鐘作為恢復時鐘采樣串行輸入。

?

圖2.14是基于DPLL的CDR, 分為兩個環路,對數據鎖相的環路(phase tracking loop)和圖2.13的CDR工作原理類似。鑒相器陣列對輸入的串行數據與M個等相位間隔的時鐘進行相位比較(也可能是在多個UI的跨度上),得到相位誤差信號。相位誤差信號送給數字濾波器。數字濾波器的性能會影響環路的帶寬,穩定性,反應速度等。經數字濾波器平滑后的誤差信號送給VCO修正時鐘相位。最終環路鎖定時,理論上相位誤差為零,90度偏移的時鐘作為恢復時鐘采樣串行輸入。

基于DPLL的CDR多了一個頻率跟蹤環路(Frequency Tracking Loop)。這是為了減小CDR的鎖定時間,減少對環路濾波器的設計約束。只有當 頻率跟蹤環路 鎖定后,才會切換到數據 相位跟蹤環路。相位跟蹤環路失鎖時,再自動切換到頻率跟蹤環路。N倍參考時鐘(Reference Clock)頻率 和 線路速率接近相等,因此兩個環路的VCO穩態控制電壓是接近相等的。借助 頻率跟蹤環路,減小了 相位跟蹤環路 的捕獲時間。

????相位跟蹤環路鎖定時,頻率跟蹤環路不會影響相位環路。因此SerDes接收側對參考時鐘的抖動沒有很高的要求。

基于相位插值器的CDR的參考時鐘可以是收發公用的PLL,也可以是每個通道獨立的PLL。這種結構的參考時鐘抖動會直接影響恢復時鐘的抖動以及接收誤碼率。

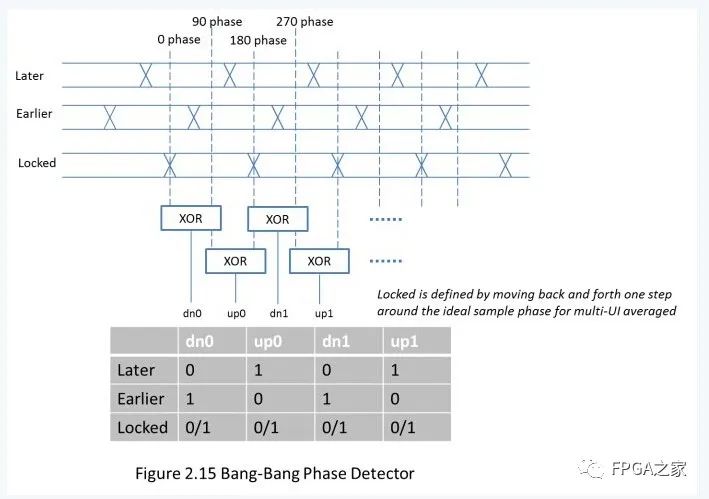

l??鑒相器(PD)

鑒相器用來比較相位誤差,相位誤差以UP或者DN的信號表示, UP/DN持續的時間正比于相位誤差。一個bang-bang結構鑒相器的例子如圖2.15。例子中只用了四個相位的恢復時鐘作為例子。

l??抽取器和濾波器

抽取器是為了讓濾波器在較低的頻率下工作。抽取的步長,平滑的方法都會影響環路的性能。數字濾波器有比例分支(Proportion)和積分分支(Integral)構成,分別跟蹤相位誤差和頻率誤差。另外數字濾波器的處理延時也不能太大,如果處理延時過大,就會導致環路不能跟蹤相位和頻率的快速變化,導致誤碼。

CDR的結構不限于以上兩種,還有其他很多變種。基本上都是一個鎖相環路。環路的跟隨性能,穩定性(STABILITY),帶寬(bandwidth)/增益(gain)性能分析是一個非常學術的問題,用小信號線形模型分析,有非常多的書籍和資料解釋了環路的量化性能。CDR環路有一些的特點總結如下:

l??環路帶寬

1.頻率低于環路帶寬的相位抖動會透過CDR轉移到恢復時鐘上。換句話說,頻率低于環路帶寬的抖動可以被CDR跟蹤,不會引起誤碼。高頻的抖動分量根據抖動幅度的大小,可能會引起誤碼。

2.環路帶寬越大,鎖定時間越短,恢復時鐘的抖動也越大。反之則鎖定時間越長,恢復時鐘的抖動也越小。作為CDR,我們希望環路帶寬大一點,這樣可以有更大的抖動容忍能力,但是對于loop timing的應用如SONET/SDH對恢復時鐘的抖動有限制,又不能太大。

3. 開關電源的開關頻率一般小于環路帶寬,可以被CDR跟蹤。但是,一方面開關電源耦合到VCO(Digital to Multi-Phase Convertor)上的噪聲不能被環路跟蹤,低成本Ring VCO尤其對電源噪聲敏感。另一方面開關電源的諧波可能超出環路帶寬。

一些協議提供了CDR增益模板,如SDH/SONET。兼容這些協議需要計算輸入和輸出的抖動預算。

2.5 ?公用鎖相環(PLL)

?? SerDes需要一個工作在數據波特率上的內部時鐘,或者1/2數據波特率的內部時鐘,工作在DDR模式。片外提供給SerDes的參考時鐘頻率遠遠低于數據波特率,PLL用來倍頻產生內部高頻時鐘。FPGA的SerDes PLL一般有8x,16x,10x,20x,40x模式,以支持常用的SerDes接口協議。比如PCIExpress工作在5Gbps, 在40x模式下需要提供125MHz的片外參考時鐘,20x模式下需要提供250MHz的片外參考時鐘。

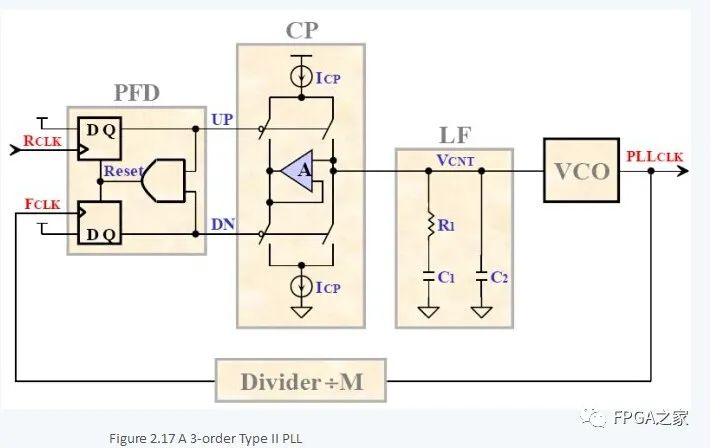

一個三階PLL電路如圖2.17,輸入信號的相位和VCO反饋信號的相位由鑒相器比較,相位誤差有charge pump轉化為電壓或電流信號,經過Loop Filter平滑后產生控制電壓,修正VCO的相位,最終使相位誤差趨于零。

????????????????????????????????????Figure 2.17 A 3-order Type II PLL

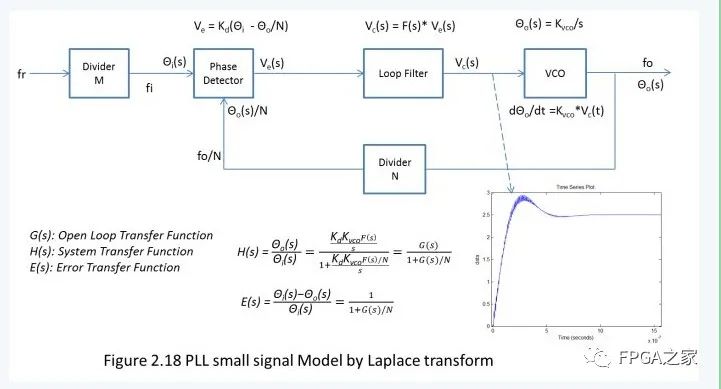

PLL的工作過程分為入鎖過程和跟蹤過程。在入鎖過程,環路的模型可以用一個非線性微分方程表示,可以評估捕獲時間,捕獲帶寬等指標。入鎖后,在小信號范圍內,PLL的模型是一個常系數線性方程,可以在拉普拉斯變換域研究PLL的帶寬,增益,穩定性等性能,?圖2.18是小信號數學模型。

?

PLL以傳輸函數極點(分母的根)個數命名環路的階數。VCO對相位有積分作用(Kvco/s),因此不帶濾波器的環路稱為一階環。帶一階濾波器的環路稱為二階環。一階環和二階環是無條件的穩定系統。然而高階環路有更多的極點和零點可以獨立的調整帶款,增益,穩定性,捕獲帶,捕捉時間等性能。

PLL的頻域傳輸函數特性主要有環路濾波器F(s)|s=jw決定, 一個通用的PLL頻域傳輸曲線如圖2.19所示。有兩個重要特征,環路帶款和jitter peaking。過大的peaking會放大jitter, 大的阻尼系數(damping factor)可以限制peaking, 但是會增加環路的如鎖時間, 影響滾降的速度和固有頻率(natural frequency)。

l??當環路鎖定后,固定相位差:

Kdc為環路的直流開環增益,Δω為VCO中心頻率和受控頻率的差。對于charge pump + passive filter結構的PLL相位誤差為零。

l ?當環路鎖定后,只有固定相位差,兩個輸入信號頻率相等。

fr/M = fo/N

l ?對于輸入端的噪聲,環路是一個低通濾波器,可以抑制高于環路截止頻率的噪聲或干擾。作為SerDes的PLL, 希望帶寬的小一些,以抑制參考時鐘上的干擾和噪聲。

對于VCO噪聲,環路是一個高通濾波器的作用。只有低于環路截止頻率的VCO噪聲得到了抑制。過量的VCO高頻噪聲會惡化時鐘的抖動。低速SerDes(<5Gbps)的VCO出于成本考慮采用Ring結構的VCO,噪聲大且對電源敏感。高速SerDes的VCO采用噪聲小較小的LC結構VCO。

3.抖動和信號集成( Jitter, SI )

抖動是指信號的跳邊時刻偏離其理想(ideal)或者預定(expected)時刻的現象。噪聲,非理想的信道,非理想的電路都是產生抖動的原因。

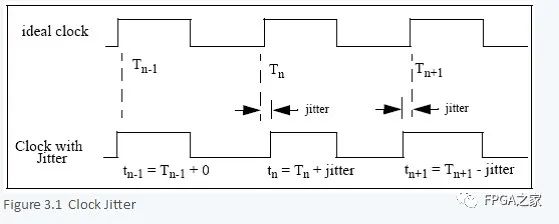

3.1 時鐘的抖動(clock jitter)

Figure 3.1??Clock Jitter

對于時鐘信號,根據應用場景的不同,對抖動的定義也不一樣。比如數字邏輯計算時序余量的時候,關心的是周期抖動。而時鐘設計人員更喜歡相位抖動,因為可以利用頻譜評估相位抖動,并可以用頻譜來評估具體的干擾對總相位抖動的貢獻。

參考圖3.1,介紹一下幾種抖動的定義。

l??相位抖動(phase jitter)

Jphase(n)= tn?– n*T。理想時鐘的每個周期T都是相等的,沒有抖動。真實時鐘的跳邊沿相對于理想時鐘的偏離稱作相位抖動。

l??周期抖動(period jitter)

Jperiod(n)= (tn- tn-1)– T。周期抖動是實際時鐘的周期相對于理想周期的偏離(deviation)。顯然Jperiod(n) = Jphase(n) - Jphase(n-1)。

l??Cycle-to-Cycle jitter

Jcycle(n) = (tn- tn-1) - (tn-1- tn-2)。前后相鄰的兩個周期的偏差是Cycle-Cycle抖動。顯然Jcycle(n)= Jperiod(n) – Jperiod(n-1)。

假設相位抖動的最大值為 +/-Jp,?而且抖動的頻率fjitter?= 0.5fclock?= 0.5/T,也就是,

tn-2時刻的相位抖動為最大值+Jp?,tn-1時刻的相位抖動為最小值-Jp

tn時刻的相位抖動為最大值+Jp?, tn+1時刻的相位抖動為最小值-Jp

那么,周期抖動最大值????????Jperiod=+/- 2* Jp

那么,Cycle-Cycle抖動最大值??Jcycle??=+/- 4* Jp

3.2.?數據的抖動(data jitter)

在高速SerDes領域每個人都在說抖動,因為抖動直接和誤碼率(BER)相關。

SerDes發送端的一個重要要求是抖動(jitter generation)----針對特定的碼型(pattern),速率和負載情況下,發送端所生成的抖動。

????信號經過信道(channel)到達接收端時,又會進一步放大抖動,不同的碼型(pattern)包含的頻率成分也不一樣,信道對不同頻率成分的傳輸延時也不一樣(非線性相位), 產生和數據pattern相關的確定性抖動。阻抗不連續產生的反射,相鄰信號的串擾和噪聲都會引起數據抖動。

????SerDes接收端的一個重要指標是抖動容忍能力(Jitter Tolerance)----針對特定的碼型和誤碼率要求(BER<10-12),SerDes接收端能夠容忍的抖動大小。對抖動評估時,會使用眼圖(eye-diagram),浴缸曲線(bath curve),抖動分布柱狀圖(PDF),抖動頻譜(jitter spectrum)等圖形手段。

有一點需要說明,在談論高速SerDes的數據抖動時(Tj,Rj,Dj etc.),是不包括低頻率抖動的。這是因為低頻率的抖動被認為是一種wander,可以被CDR跟蹤,不會引起誤碼。在用示波器(SDA)測量數據抖動的時候,可以設置示波器內嵌的CDR環路帶寬,示波器測量的抖動數據已經濾掉了低頻抖動。

根據抖動產生的原因和概率密度函數,常常將抖動分為幾類。對抖動進行分類的意義在于某些類型的抖動可以被校正,而其他類型的不能被校正。經典的,總抖動Tj(Total Jitter)被分類為確定性抖動Dj (deterministic jitter)和隨機抖動Rj (random jitter)。抖動以UI或者ps為單位,可以是均方根值,或者峰峰值。

3.2.1 Dj

Dj被進一步細分,

l??DCD(Duty cycle distortion)

占空比失真抖動。差分信號的正端負端的偏置電壓不一致,或者上升沿和下降沿時間不一致會導致占空比失真。因為DCD和數據pattern相關,是可以被校正的抖動。

l??DDJ(Data dependent jitter)

數據碼型相關的抖動,也稱 碼間干擾ISI(intersymbol interference)。DDJ是由于不理想的信道導致。是可以被均衡器校正的抖動。

l??Pj(Periodic jitter)

周期性抖動。Pj由電路上周期性干擾源導致。比如開關電源的開關頻率,時鐘信號的串擾等。雖然電源的開關頻率一般在CDR的跟蹤范圍內,但是低次諧波成分可能會落在環路帶寬外,或者jitter peaking區域, 更重要的是電源諧波對CDR內VCO的干擾是不能被抑制和跟蹤的,所以對于基于Ring VCO的CDR一定要盡可能的使用LDO供電。Pj不能被均衡器校正.

l??BUJ(Bounded uncorrelated jitter)

BUJ由非時鐘的干擾源引起。如果干擾源aggressor和victim是異步的,抖動的概率分布為有界的高斯分布,此時也稱作CBGJ(Correlated Bounded Gaussian Jitter)。BUJ/CBGJ不能被校正。

3.2.2 Rj

Rj有半導體本身的噪聲引起,一個重要特征就是Rj的概率密度函數是高斯分布的,沒有邊界,且和數據pattern無關。只有在一定誤碼率約束下,才可以被認為是有界的。

3.2.3 Tj

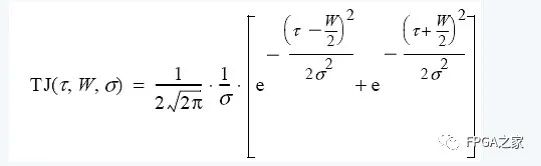

數學意義上,抖動的概率分布函數可以近視為高斯分布和雙底拉克分布的卷積。

對高斯分布有貢獻的抖動為:

n??Rj為高斯分布

n??大量Pj疊加的效果也為高斯分布

n??部分BUJ也為高斯分布

對雙底拉克分布有貢獻的抖動為:

n??DCD被近視為雙底拉克概率分布

高斯分布和雙底拉克分布的卷積:

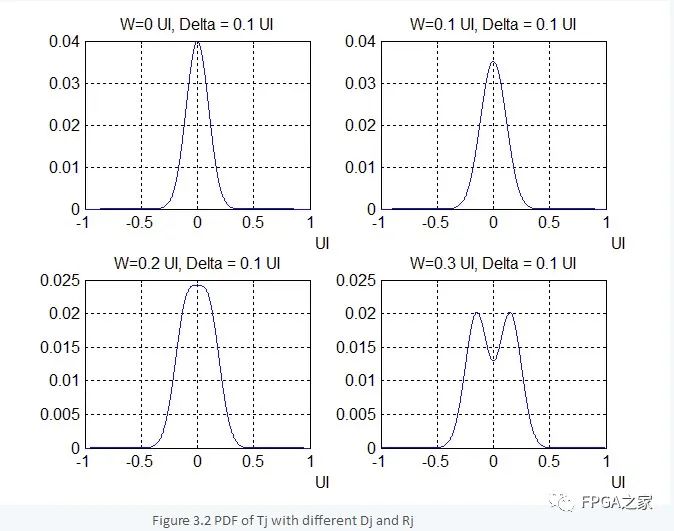

其中,W被認為是確定性抖動的峰峰值,δ是高斯分布的均方差。見圖3.2, 可以看到,隨著確定性抖動W的增加,概率密度分布曲線的頂部出現了雙峰。一般來講頂部曲線反映了確定性抖動的大小程度。

Figure 3.2 PDF of Tj with different Dj and Rj

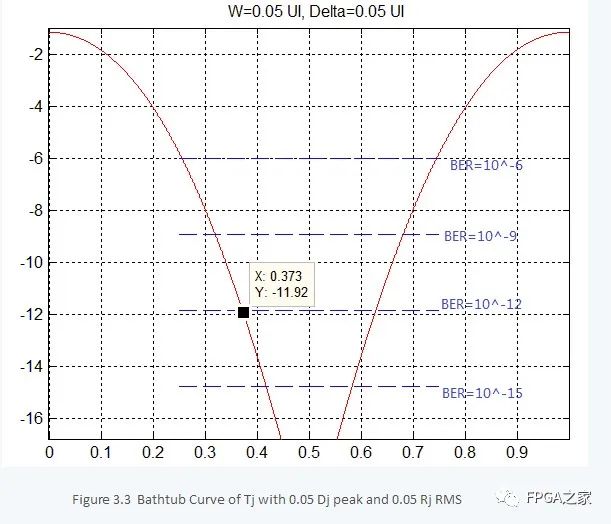

把一個UI內的兩個跳變沿處(0 UI處和1UI處)的概率分布函數放在一張圖中,就是抖動的浴缸曲線(bathtub curve)。因為對數的寬動態范圍,Y坐標以對數顯示。圖3.3為確定性抖動W=0.05UI, 高斯抖動方差0.05UI的浴缸曲線。

?????Figure 3.3??Bathtub Curve of Tj with 0.05 Dj peak and 0.05 Rj RMS

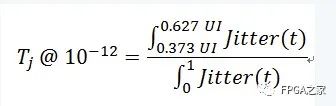

浴缸曲線還會標出對應的誤碼率BER坐標,比如圖中BER=10^-12的峰峰值抖動為Tj(p-p)=0.373*2 = 0.746 UI。曲線下面的面積占總面積的比率就是誤碼率。比如圖中,

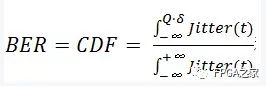

浴缸曲線的頂部主要為確定性抖動Dj的貢獻,越靠近底部,高斯抖動的貢獻越大,并以高斯曲線的斜率衰減,也因此常利用高斯分布的特性進行估算。下表為高斯分布? 和均方差關系。???????

和均方差關系。???????

?

在規定的BER內,利用該表可以快速估算均方差值和峰峰值之間的關系。比如高斯抖動的均方根0.05UI,誤碼率要求為10^-12 BER,查表可知Q=7,那么高斯抖動的峰峰值要求是0.05UI*7*2 = 0.7UI。

如前所述,W=0.05UI,Rj=0.05UI計算出的總抖動Tj=0.746UI;

????利用高斯特性估算的高斯抖動為0.7UI。

????如果按Tj = Rj(0.7UI)+Dj(0.05UI)計算得到0.75U,基本是一致的,差異是因為畫圖程序有量化誤差。

4.信號集成(SI)及仿真

4.1信道channel

SerDes信道關注的頻率范圍是0Hz到奈奎斯特頻率,也就是2倍的信號基頻。信號的基頻是信號線速率的一半,也就是說信號的奈奎斯特頻率就是線速率。信道對信號的損傷包括插入損失(insertion loss),反射 (reflection),串擾(crosstalk)等。這些損傷可以用S-parameter信道模型來表達。S-parameter可以有矢量網絡分析儀測量(Vector Network Analyzer)得到。信道不是一個純阻性網絡,還包括容性和感性。這樣對不同頻率里成分的時延也不一樣,從而產生和data pattern相關的抖動。

信道上的每一個不連續阻抗點都會產生反射,根據反位置的不同,反射信號會以不同的相位疊加在原始信號上,增加或者減小信號的幅度。

SerDes信號為差分形式,對共模干擾有較強的抑制。如果在+/-端上的干擾有差異,就會引入串擾。通常外部PCB可以保證SerDes數據和干擾源保持足夠的距離,但是芯片內部由于考慮到經濟性,很難保證SerDes信號和干擾源足夠的隔離距離,尤其是一個通道自己的發送信號干擾自己的接收信號。

4.2?芯片封裝Package

封裝package也是信道的一部分。芯片外部的信道可以通過VNA測量的到,而封裝的S-parameter通常有芯片制造商提供,仿真時可以把兩者級聯起來。封裝package由于距離較短,insertion loss通常不是主要問題,主要考慮的是阻抗匹配問題。

4.3 SI仿真

信號集成性(SI)仿真可以通過把SerDes發送端SPICE模型,封裝和信道的S-parameter模型,接收端SPICE模型級聯起來搭建仿真平臺,利用仿真工具對不同的激勵在不同的測試條件作電路仿真。通過測量SerDes接收端的眼圖來評估是否滿足設計需求。也可以通過實測接收端眼圖,檢驗是否滿足接收端的眼圖模板,或者協議規定的眼圖模板。圖4.1為一個實測的3.125Gbps信號的眼圖及模板,同時也包含了浴缸曲線和統計圖。

Figure 4.1 Rx-end Eye-diagram of A 3.125Gbps SerDes

對于高速SerDes(>5Gbps),這種傳統的電路仿真方法已經不能滿足設計的需求。首先,過量的碼間干擾ISI導致接收端眼圖完全閉合,但是通過芯片內的DFE均衡后,眼圖可能是很好的。其次,電路仿真(SPICE)的速度非常慢,即使是有辦法把DFE均衡加入仿真,由于DFE仿真需要足夠長時間的bits來訓練,此時,電路仿真的仿真時間是不可接受的。

對于高速SerDes的仿真需要借助統計分析 (statistical analysis) 的方法。統計分析的方法把發送端-信道-接收端的連接近視為線性系統,計算系統脈沖響應h(t),加入噪聲源來模擬抖動,然后用激勵對脈沖響應進行卷積,得到接收端的信號,這種方法可以把廠家私有的FFE,DFE自適應算法加入仿真。

統計分析 (statistical analysis)方法不能仿真電路的非線性和時變特性,所以高速SerDes往往要兩者結合起來仿真SI。更多關于統計分析 (statistical analysis)方法可以參考。

5.?結尾

有人講過,現在的汽車是如此復雜,以至于雖然每一個零件都有人懂,但是合起來作為整車卻沒人能夠全懂。近些年來,FPGA變的越來越復雜,對工程師的要求也越來越高。要成為一個合格的FPGA應用工程師,不僅要擅長數字電路的設計,還要懂得高速SerDes, 信號集成SI, DSP算法, 多核CPU, 嵌入式操作系統等。每一項技術背后都是一個專業領域,一個人不會在每一個領域內都是專家,只要比別人多學習一點,關鍵時候就會突出你的價值。本篇主要介紹了SerDes的基本結構和用好SerDes需要掌握一些的知識,希望對你的工作有所幫助。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論