叢秋波

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)的帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代 。然而,基于SERDES的FPGA往往價(jià)格昂貴,因?yàn)樗鼈兌际轻槍?duì)高端應(yīng)用的FPGA器件。萊迪思(Lattice )半導(dǎo)體公司在這應(yīng)用領(lǐng)域已經(jīng)推出兩款低成本帶有SERDES的 FPGA器件系列基礎(chǔ)上,日前又推出采用富士通公司先進(jìn)的低功耗工藝,目前業(yè)界首款最低功耗與價(jià)格并擁有SERDES 功能的FPGA器件――中檔的、采用65nm工藝技術(shù)的 LatticeECP3系列。

萊迪思高級(jí)副總裁兼高密度解決方案總經(jīng)理Sean Riley表示,LatticeECP3 FPGA系列擁有符合XAUI抖動(dòng)標(biāo)準(zhǔn)的多協(xié)議3.2G SERDES、DDR3存儲(chǔ)器接口、具有強(qiáng)大的DSP功能、高密度的片上存儲(chǔ)器,以及多達(dá)149K 的LUT,所有這些器件的功耗與價(jià)格僅是具有SERDES 功能FPGA的競(jìng)爭(zhēng)器件的一半。

Sean Riley介紹,LatticeECP3的靜態(tài)功耗與競(jìng)爭(zhēng)對(duì)手的同類產(chǎn)品相比要低于85%,總的功耗低于50%,其原因是在工藝制程上采用了可變的通道長(zhǎng)度、優(yōu)化了晶體管、改進(jìn)布線等方法,從而對(duì)功耗進(jìn)行了優(yōu)化,可實(shí)現(xiàn)以最低的功耗實(shí)現(xiàn)高速串行協(xié)議。

據(jù)了解,低功耗LatticeECP3 FPGA系列有5個(gè)成員,它們都能提供符合標(biāo)準(zhǔn)的多協(xié)議3G SERDES 、在同類產(chǎn)品中是首款擁有DDR/DDR2和DDR3存儲(chǔ)器接口、高性能級(jí)聯(lián)DSP slice適用于高性能射頻、基帶和圖像信號(hào)處理。LatticeECP3 FPGA還提供中檔FPGA系列中最快的LVDS I / O,能夠處理1Gbps速率的輸入和輸出信號(hào),還有高達(dá)6.8 M位的嵌入式存儲(chǔ)器。邏輯密度的范圍從17K LUT到149K LUT,用戶的I / O數(shù)目高達(dá)586個(gè)。

除此之外,LatticeECP3 FPGA系列的多種創(chuàng)新特性還體現(xiàn)在以下幾個(gè)方面:一是,符合10GbE XAUI抖動(dòng)標(biāo)準(zhǔn)的3.2G Gbps SERDES,每個(gè)SERDES模塊都具有混合并能夠匹配多種協(xié)議的能力。包括PCI Express、CPRI、OBSAI、XAUI、Serial RapidIO和千兆位以太網(wǎng)。二是,專門設(shè)計(jì)了SERDES /PCS塊,使短延遲變化的CPRI鏈路設(shè)計(jì)能用于遠(yuǎn)程射頻頭連接的無(wú)線基站。三是符合SMPTE串行數(shù)字接口標(biāo)準(zhǔn),每個(gè)SERDES通道都能單獨(dú)地支持3G 、HD和SD /DVB -ASI視頻廣播信號(hào),這種功能是萊迪思獨(dú)有的技術(shù)。擁有三速率支持功能且無(wú)需采用任何過(guò)采樣技術(shù),能盡可能少地消耗功率。四是通過(guò)組合多個(gè)DSP slice,可實(shí)現(xiàn)36位x 36位的乘法和累加模塊,每個(gè)slice都能以500MHz 的頻率工作。DSP slices還具有創(chuàng)新的級(jí)聯(lián)功能,能實(shí)行寬的ALU及加法樹(shù)的功能,且不會(huì)出現(xiàn)FPGA邏輯的性能瓶頸現(xiàn)象。五是具有800Mbps的DDR3存儲(chǔ)器接口,并有內(nèi)置的讀和寫可調(diào)余量的功能。六是輸入延時(shí)塊的1Gbps LVDS I / O,能與高性能的ADC和DAC 相連接。

Sean Riley說(shuō),LatticeECP3 FPGA由于擁有了這些功能,非常適合于大批量的成本和功耗敏感的無(wú)線基礎(chǔ)設(shè)施和有線接入設(shè)備的開(kāi)發(fā),以及視頻和圖像方面的應(yīng)用。

與此同時(shí),萊迪思還推出了ispLEVER 設(shè)計(jì)工具套件7.2版本的Service Pack 1支持LatticeECP3 FPGA系列。ispLEVER設(shè)計(jì)工具套件擁有全方位的設(shè)計(jì)環(huán)境。針對(duì)所有的設(shè)計(jì)任務(wù),提供了一套完整的功能強(qiáng)大的工具,包括項(xiàng)目管理、IP集成、設(shè)計(jì)規(guī)劃、布局和布線、在系統(tǒng)邏輯分析等。

審核編輯 黃宇

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)的帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代 。然而,基于SERDES的FPGA往往價(jià)格昂貴,因?yàn)樗鼈兌际轻槍?duì)高端應(yīng)用的FPGA器件。萊迪思(Lattice )半導(dǎo)體公司在這應(yīng)用領(lǐng)域已經(jīng)推出兩款低成本帶有SERDES的 FPGA器件系列基礎(chǔ)上,日前又推出采用富士通公司先進(jìn)的低功耗工藝,目前業(yè)界首款最低功耗與價(jià)格并擁有SERDES 功能的FPGA器件――中檔的、采用65nm工藝技術(shù)的 LatticeECP3系列。

萊迪思高級(jí)副總裁兼高密度解決方案總經(jīng)理Sean Riley表示,LatticeECP3 FPGA系列擁有符合XAUI抖動(dòng)標(biāo)準(zhǔn)的多協(xié)議3.2G SERDES、DDR3存儲(chǔ)器接口、具有強(qiáng)大的DSP功能、高密度的片上存儲(chǔ)器,以及多達(dá)149K 的LUT,所有這些器件的功耗與價(jià)格僅是具有SERDES 功能FPGA的競(jìng)爭(zhēng)器件的一半。

Sean Riley介紹,LatticeECP3的靜態(tài)功耗與競(jìng)爭(zhēng)對(duì)手的同類產(chǎn)品相比要低于85%,總的功耗低于50%,其原因是在工藝制程上采用了可變的通道長(zhǎng)度、優(yōu)化了晶體管、改進(jìn)布線等方法,從而對(duì)功耗進(jìn)行了優(yōu)化,可實(shí)現(xiàn)以最低的功耗實(shí)現(xiàn)高速串行協(xié)議。

據(jù)了解,低功耗LatticeECP3 FPGA系列有5個(gè)成員,它們都能提供符合標(biāo)準(zhǔn)的多協(xié)議3G SERDES 、在同類產(chǎn)品中是首款擁有DDR/DDR2和DDR3存儲(chǔ)器接口、高性能級(jí)聯(lián)DSP slice適用于高性能射頻、基帶和圖像信號(hào)處理。LatticeECP3 FPGA還提供中檔FPGA系列中最快的LVDS I / O,能夠處理1Gbps速率的輸入和輸出信號(hào),還有高達(dá)6.8 M位的嵌入式存儲(chǔ)器。邏輯密度的范圍從17K LUT到149K LUT,用戶的I / O數(shù)目高達(dá)586個(gè)。

除此之外,LatticeECP3 FPGA系列的多種創(chuàng)新特性還體現(xiàn)在以下幾個(gè)方面:一是,符合10GbE XAUI抖動(dòng)標(biāo)準(zhǔn)的3.2G Gbps SERDES,每個(gè)SERDES模塊都具有混合并能夠匹配多種協(xié)議的能力。包括PCI Express、CPRI、OBSAI、XAUI、Serial RapidIO和千兆位以太網(wǎng)。二是,專門設(shè)計(jì)了SERDES /PCS塊,使短延遲變化的CPRI鏈路設(shè)計(jì)能用于遠(yuǎn)程射頻頭連接的無(wú)線基站。三是符合SMPTE串行數(shù)字接口標(biāo)準(zhǔn),每個(gè)SERDES通道都能單獨(dú)地支持3G 、HD和SD /DVB -ASI視頻廣播信號(hào),這種功能是萊迪思獨(dú)有的技術(shù)。擁有三速率支持功能且無(wú)需采用任何過(guò)采樣技術(shù),能盡可能少地消耗功率。四是通過(guò)組合多個(gè)DSP slice,可實(shí)現(xiàn)36位x 36位的乘法和累加模塊,每個(gè)slice都能以500MHz 的頻率工作。DSP slices還具有創(chuàng)新的級(jí)聯(lián)功能,能實(shí)行寬的ALU及加法樹(shù)的功能,且不會(huì)出現(xiàn)FPGA邏輯的性能瓶頸現(xiàn)象。五是具有800Mbps的DDR3存儲(chǔ)器接口,并有內(nèi)置的讀和寫可調(diào)余量的功能。六是輸入延時(shí)塊的1Gbps LVDS I / O,能與高性能的ADC和DAC 相連接。

Sean Riley說(shuō),LatticeECP3 FPGA由于擁有了這些功能,非常適合于大批量的成本和功耗敏感的無(wú)線基礎(chǔ)設(shè)施和有線接入設(shè)備的開(kāi)發(fā),以及視頻和圖像方面的應(yīng)用。

與此同時(shí),萊迪思還推出了ispLEVER 設(shè)計(jì)工具套件7.2版本的Service Pack 1支持LatticeECP3 FPGA系列。ispLEVER設(shè)計(jì)工具套件擁有全方位的設(shè)計(jì)環(huán)境。針對(duì)所有的設(shè)計(jì)任務(wù),提供了一套完整的功能強(qiáng)大的工具,包括項(xiàng)目管理、IP集成、設(shè)計(jì)規(guī)劃、布局和布線、在系統(tǒng)邏輯分析等。

審核編輯 黃宇

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1662文章

22476瀏覽量

638355 -

芯片

+關(guān)注

關(guān)注

463文章

54281瀏覽量

468323 -

串行

+關(guān)注

關(guān)注

0文章

256瀏覽量

35500

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

從“價(jià)格戰(zhàn)”到“價(jià)值戰(zhàn)”!高性價(jià)比 MCU 新品井噴

電子發(fā)燒友網(wǎng)報(bào)道(文 / 吳子鵬)高性價(jià)比 MCU 是指那些在價(jià)格上具備競(jìng)爭(zhēng)力,同時(shí)在性能和功能方面也能滿足特定應(yīng)用需求的微控制器。因此,“高性價(jià)比” 的定義通常需從性能、功能、成本、

PIC16(L)F153XX:高性價(jià)比微控制器的卓越之選

PIC16(L)F153XX:高性價(jià)比微控制器的卓越之選 在電子工程師的設(shè)計(jì)工具箱中,微控制器是不可或缺的核心組件。PIC16(L)F153XX系列微控制器憑借其豐富的功能和高性價(jià)比,在眾多應(yīng)用場(chǎng)

英特爾Cyclone V器件:高效能與低功耗的完美融合

英特爾Cyclone V器件:高效能與低功耗的完美融合 在電子設(shè)計(jì)領(lǐng)域,FPGA(現(xiàn)場(chǎng)可編程門陣列)器件一直是實(shí)現(xiàn)高性能、靈活性和低功耗設(shè)計(jì)

英特爾Arria 10器件:高性能與低功耗的完美結(jié)合

英特爾Arria 10器件:高性能與低功耗的完美結(jié)合 在當(dāng)今電子技術(shù)飛速發(fā)展的時(shí)代,現(xiàn)場(chǎng)可編程門陣列(FPGA)和片上系統(tǒng)(SoC)在眾多領(lǐng)域發(fā)揮著至關(guān)重要的作用。英特爾的Arria 10器件

什么是低功耗設(shè)計(jì),如何評(píng)估低功耗MCU性能?

內(nèi)部不使用的功能是否可以徹底關(guān)掉,就是讓它不消耗額外的能量。

具備以上幾個(gè)特征的MCU,基本上都可以叫做低功耗MCU。

低功耗MCU一般平時(shí)都是處于休眠模式,只保持了一個(gè)可被喚醒的狀態(tài),每次喚醒

發(fā)表于 12-12 07:43

Amazon Connect發(fā)布多項(xiàng)Agentic AI新功能 打造無(wú)縫客戶體驗(yàn)

亞馬遜云科技在2025 re:Invent全球大會(huì)上,宣布Amazon Connect推出多項(xiàng)Agentic AI新功能,覆蓋四大領(lǐng)域:可在語(yǔ)音與數(shù)字渠道自主執(zhí)行操作的自動(dòng)化AI Agent;可

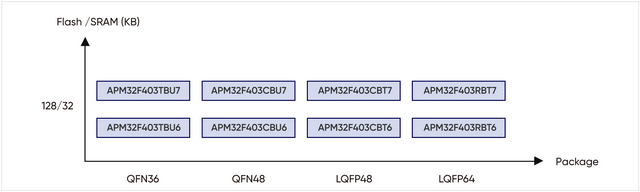

極海正式發(fā)布APM32F403系列高性價(jià)比MCU滿足低功耗低成本應(yīng)用需求

來(lái)源:半導(dǎo)體器件應(yīng)用網(wǎng) 作者:極海半導(dǎo)體 面向中高端工業(yè)應(yīng)用市場(chǎng),為兼顧客戶對(duì)性能、成本、功耗等綜合需求, 極海正式推出APM32F403系列高性價(jià)比MCU ,產(chǎn)品已通過(guò)IEC 60730

極海正式發(fā)布APM32F403系列高性價(jià)比MCU,滿足低功耗、低成本應(yīng)用需求

面向中高端工業(yè)應(yīng)用市場(chǎng),為兼顧客戶對(duì)性能、成本、功耗等綜合需求,極海正式推出APM32F403系列高性價(jià)比MCU,產(chǎn)品已通過(guò)IEC 60730/60335功能安全認(rèn)證,可提供符合Class B標(biāo)準(zhǔn)

極海半導(dǎo)體推出APM32F403系列高性價(jià)比MCU

面向中高端工業(yè)應(yīng)用市場(chǎng),為兼顧用戶對(duì)性能、成本、功耗等綜合需求,極海正式推出APM32F403系列高性價(jià)比MCU,產(chǎn)品已通過(guò)IEC 60730/60335功能安全認(rèn)證,集高性能實(shí)時(shí)處理能力、高集成度

高速/低功耗/高性價(jià)比的 HyperRam 應(yīng)用

,HyperRam 比 SDRAM 具有顯著優(yōu)勢(shì),使其適合低功耗應(yīng)用,如下圖所示:

HyperRam 提供比同等容量的 SDRAM 更高的性價(jià)比,使其成為成本敏感型應(yīng)用的首選

發(fā)表于 09-05 06:06

PY32F003國(guó)產(chǎn)單片機(jī)、外設(shè)豐富、高性價(jià)比的國(guó)產(chǎn)替代方案

PY32F003 是普冉半導(dǎo)體推出的一款高性價(jià)比國(guó)產(chǎn)32位微控制器,PY32F003是一款高性價(jià)比的國(guó)產(chǎn)替代方案,可以用來(lái)替換一些進(jìn)口MCU。芯片采用32 位 ARM? Cortex?-M0+內(nèi)核

發(fā)表于 08-21 11:50

電動(dòng)滑板車核心技術(shù)方案解析及高性價(jià)比芯片選型推薦SI24R1+AT2401C

,以低功耗和高性價(jià)比著稱,常用于物聯(lián)網(wǎng)和遙控設(shè)備。CB2401和AT2401C是射頻前端(RF FEM)芯片,可增強(qiáng)信號(hào)發(fā)射功率和接收靈敏度,適合提升電動(dòng)滑板遙控距離和抗干擾能力。推薦的方案是將

發(fā)表于 07-29 17:04

【文章轉(zhuǎn)載】CANoe產(chǎn)品體系19版本新功能(下) - 基礎(chǔ)功能與XIL測(cè)試

新版本持續(xù)為智能電動(dòng)網(wǎng)聯(lián)汽車軟件開(kāi)發(fā)測(cè)試帶來(lái)全新功能,IDE開(kāi)發(fā)環(huán)境支持.NET8.0、Python、MATLAB2024b,VisualStudioCode集成測(cè)試開(kāi)發(fā)和調(diào)試功能,支持

PPEC inside直流穩(wěn)壓電源,超高性價(jià)比「低 / 高壓大電流測(cè)試?yán)鳌?/a>

直流穩(wěn)壓電源廣泛應(yīng)用于需要克服電網(wǎng)波動(dòng)或負(fù)載變化影響、為精密電子設(shè)備提供穩(wěn)定直流電壓的場(chǎng)合。傳統(tǒng)實(shí)驗(yàn)室測(cè)試電源價(jià)格昂貴,森木磊石 PPEC inside 直流穩(wěn)壓電源,憑借其卓越性能及超高性價(jià)比

發(fā)表于 06-10 11:36

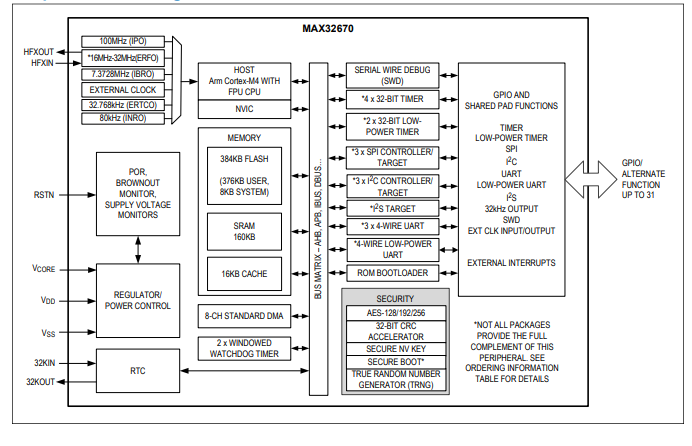

MAX32670高可靠性、超低功耗微控制器技術(shù)手冊(cè)

在Darwin家族中,MAX32670是一款超低功耗、高性價(jià)比、高可靠性的32位微控制器,在實(shí)現(xiàn)復(fù)雜的傳感器處理設(shè)計(jì)的同時(shí)不會(huì)影響電池壽命。器件集成了高度靈活性的多功能電源管理單元與

低功耗高性價(jià)比FPGA器件增添多項(xiàng)新功能

低功耗高性價(jià)比FPGA器件增添多項(xiàng)新功能

評(píng)論