01智多晶SerDes IP已經升級到2.0版本

為了滿足用戶對SerDes日益增漲和多樣化的要求。智多晶SerDes IP推出了2.0版本的升級,本次升級相比1.0版本主要帶來了以下的變化:

增加了對SerDes內部的不同通道單獨進行速率配置的功能

增加了同一路通道內部的TX和RX進行獨立參數的配置的功能

增加了對每個單獨通道的時鐘來源(QPLL/CPLL)選擇的功能

增加了從其他quad來的參考時鐘來源的選擇(North/South Route)功能

增加了選擇輸出時鐘路徑:PMA內部時鐘或直接輸出參考時鐘

增加了RX/TX方向64B/66B 相關的功能

增加了Bypass SerDes內部FIFO的功能(使用延遲線代替)

增加了Channel Bonding(多通道綁定同步傳輸)的功能

02智多晶Serdes IP 2.0界面介紹

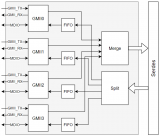

圖1 SerDes IP 多通道單獨頁面配置

智多晶SerDes IP采用了靈活的配置界面可以對每個SerDes通道(channel)進行靈活的配置。如圖1所示,用戶可以定制對每個channel的速率,參考時鐘頻率,CPLL/QPLL的選擇進行獨立的配置,用以滿足各種自定義項目中的需求。

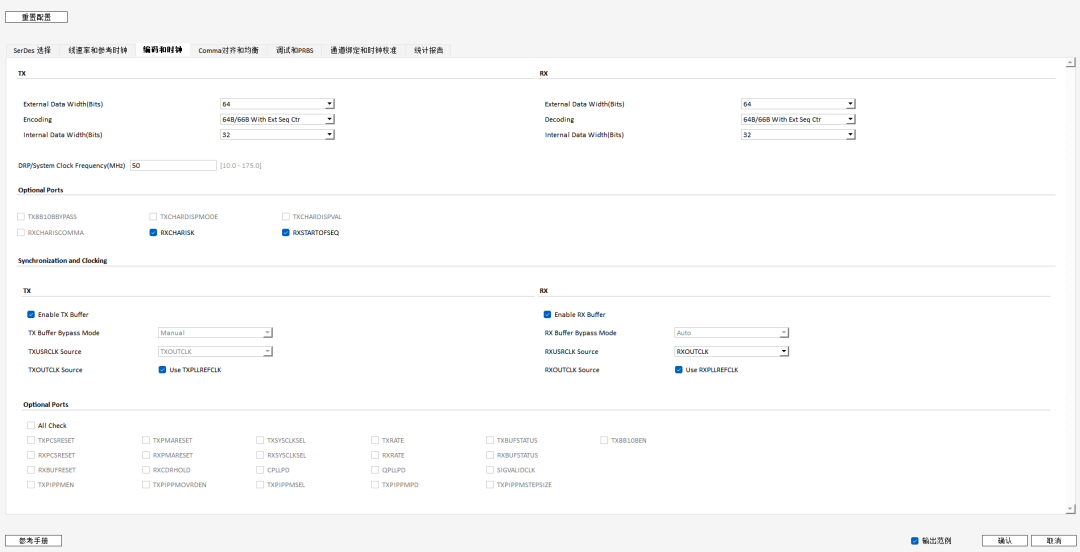

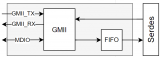

圖2 編碼選擇和時鐘輸出選擇

目前SerDes 2.0已經支持了對8B/10B編碼和64B/66B編碼(Gearbox層以下)的配置選項。用戶可以使用智多晶SerDes硬核的編碼器完成8B/10B和64B/66B(Gearbox層以下)的對應功能 。IP界面也提供了對外部位寬和內部位寬的定制化配置。用戶可以根據自己的系統和對應的上層協議來靈活的選取數據位寬。

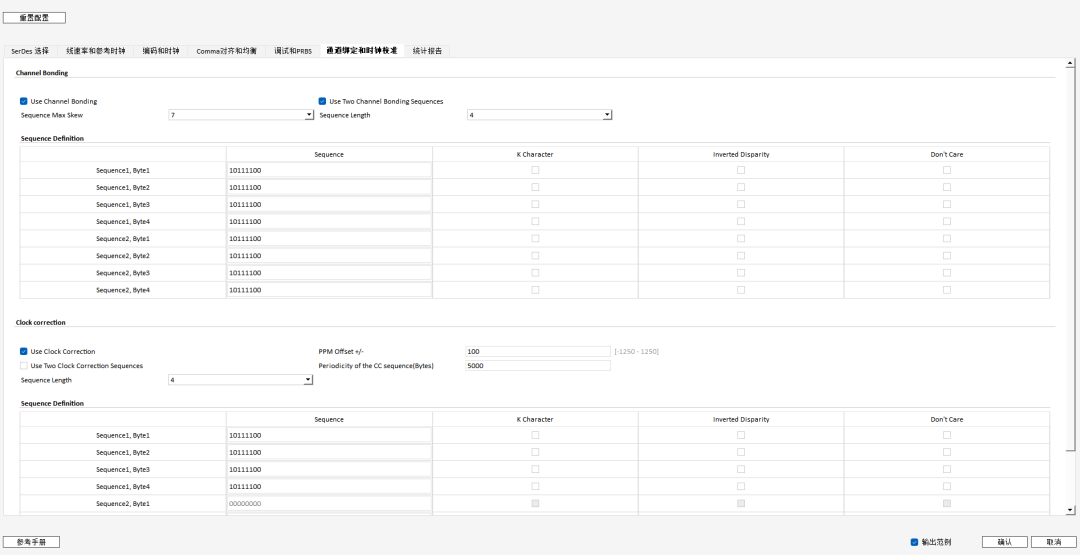

圖3 通道綁定和時鐘校準功能

目前SerDes 2.0已經支持了對通道綁定和時鐘校準的功能。用戶可以通過界面上的提示來完成相對應的配置。以通道綁定為例,可以設置具體的通道綁定所需要的碼形長度和具體數值等。

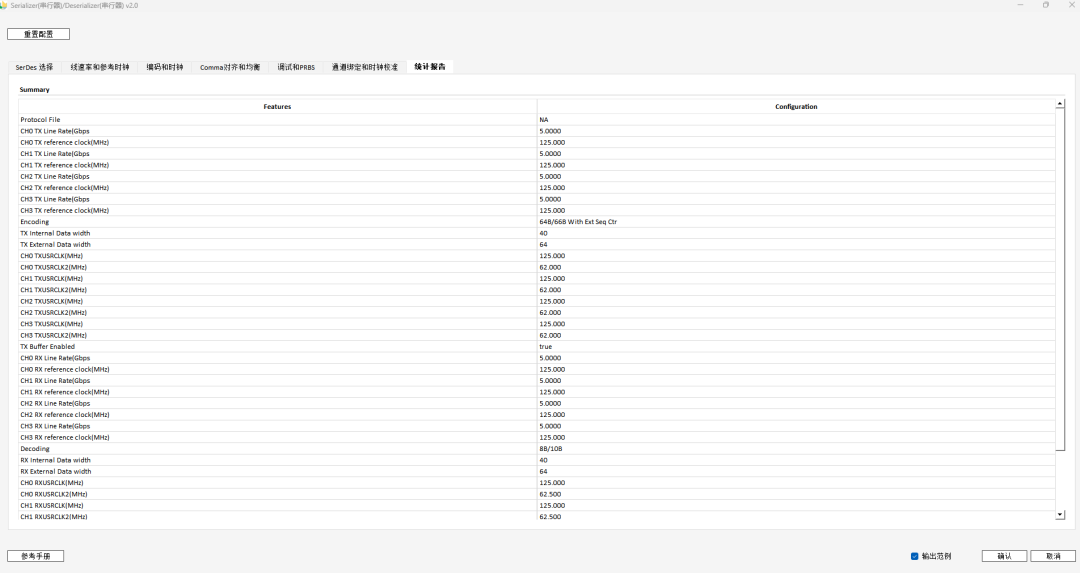

圖4 統計報告列表

在配置完成之后,SerDes 2.0 IP會生成對應的統計報告列表,用戶可以通過瀏覽生成的統計報告列表來驗證自己的IP是否滿足自己的配置要求。同時提供了輸出范例工程,供用戶作為參考使用。

03智多晶SerDes IP 2.0的常用場景

SerDes(Serializer/Deserializer)是一種高速串行通信技術,主要用于將多路低速并行信號轉換為高速串行信號,并通過傳輸媒體(如光纜或銅線)傳輸,然后在接收端再將串行信號轉換回并行信號隨著高速集成電路的發展,對高帶寬,低延遲的協議需求越來越大。目前多種高速協議都可以以Serdes 為基礎進行進一步的開發,用以完成高速通訊的目的。

目前常見的使用主要包括:

萬兆以太網

CPRI

JESD204B

QSGMII

SRIO

XAUI

PCIE

AURORA

DP/eDP

VByOne

目前智多晶Seal 5000系列產品SerDes的性能處于業界領先水平,SDM最大支持0.5-10.3125Gbps線速率,SDP最大支持0.5-6.6Gbps的線速率。SerDes最大速率受到PCB信號完整性設計,外界干擾等多種條件影響。如果要達到理論性能需要有相關設計保障,詳細信息請咨詢智多晶FAE。

-

IP

+關注

關注

5文章

1868瀏覽量

155975 -

時鐘

+關注

關注

11文章

1981瀏覽量

135076 -

SerDes

+關注

關注

8文章

234瀏覽量

36886

原文標題:“芯”技術分享 | 智多晶SerDes 2.0 IP介紹

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

智多晶Serdes IP的應用領域及工作原理

智多晶FIFO_Generator IP介紹

智多晶eSPI_Slave IP介紹

國產智多晶FPGA介紹及應用

HDMI_1.4_2.0_RX_Subsystem_IP介紹和基礎debug建議

IP_數據表(I-1):Combo Serdes PHY for TSMC 28nm HPM

為什么我們需要SERDES?SERDES的優點有哪些?

智多晶LPC_Controller IP介紹

智原科技推出最新SerDes IP持續布局聯電22納米IP解決方案

智原推出最新SerDes IP持續布局聯電22納米IP解決方案

智多晶QSGMII IP介紹

智多晶SGMII IP介紹

智多晶SerDes 2.0 IP介紹

智多晶SerDes 2.0 IP介紹

評論