串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。在過去幾年中已經看到有內置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價格昂貴。

本方案是以CME的低功耗系列FPGA的HR03為平臺,實現8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等特點。

1 硬件接口:

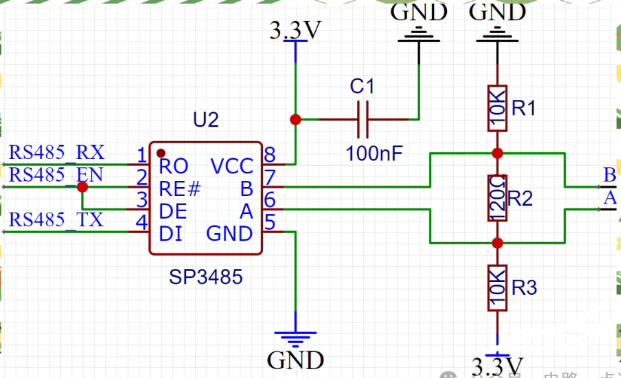

硬件的接口如上圖所示,主要包括發送與接收模塊。

發送模塊包括8b/10b編碼器,并串轉換器,鎖相環(PLL)頻率合成器和發送器,接收模塊包括 8b/10b解碼器,Comma 檢測器,串并轉換器,時鐘數據恢復器(CDR)和接收器。

8b/10b編碼器用于將從上層協議芯片發送過來的字節信號映射成直流平衡的 10 位8b/10b 編碼,并串轉換用于將 10 位編碼結果串行化,并串轉換所需的高速、低抖動時鐘由鎖相環提供,發送器用于將 CMOS 電平的高速串行碼流轉換成抗噪聲能力較強的差分信號,經背板連接或光纖信道發送到接收機。

在接收端,接收器將接收到的低擺幅差分信號還原為 CMOS 電平的串行信號,CDR 從串行信號中抽取時鐘信息,完成對串行數據的采樣,串并轉換利用 CDR 恢復的時鐘,將串行信號轉換成 10 位的并行數據,Comma 檢測器檢測特殊的 Comma 字符,調整字邊界,字邊界正確的并行數據經過 8b/10b 解碼,還原為字節信號,傳送到上層協議芯片,完成整個信息傳輸過程。

實際的設計中,CDR部分是由純邏輯電路完成的,為設計的的部分,下面將介紹數字CDR在HR03的實現方案。

2 數字CDR:

CDR模塊作用是從數據中恢復嵌入的時鐘,然后接收器按照恢復的時鐘進行數據位對齊并通過comma進行字對齊。,將數據進行8b/10b解碼,供系統使用。

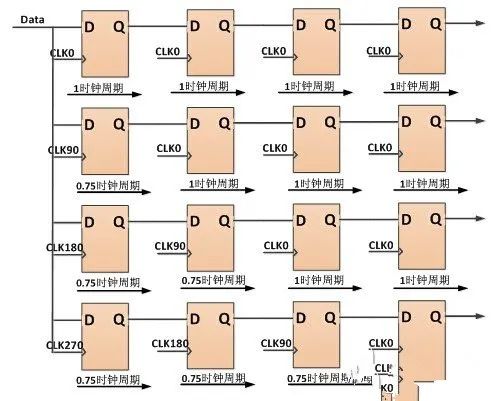

本方案采用同頻多相的時鐘采樣方法,具體實現過程利用PLL產生4個時鐘頻率相同,相位相差90度的時鐘,分別為clk0、clk90、clk180、clk270,這四個時鐘輸出完全同步,利用4個時鐘對數據進行采樣,以獲得4倍過采樣的效果,具體的實現過程如下圖所示:

在數據時鐘恢復時,將到來的數據分別輸入到四個觸發器,分別用4個不同的相位進行采樣,要注意保證從輸入引腳到四個觸發器的延遲基本一致。

列觸發器的觸發分別由時鐘CLK0、CLK90、CLK180、CLK270的上升沿觸發,按照這樣的方式來觸發就可以得到四個數據采樣點。這樣就將原始時鐘周期分成了四個單獨的90度的區域,如果系統時鐘為200MHz,上圖所示的電路就相當于產生了800MHz 的采樣速率。

僅通過一階的觸發器,輸出的采樣數據存在亞穩態的問題,因此需對采樣點作進一步的處理。這里可將四個采樣點通過進一步的觸發,除掉亞穩態的問題,從而使采樣點移到下一個相同的時鐘域。通常,亞穩態的去除要經過兩三級的處理,這就使得在有效數據輸出前會有數位無效的數據,在數據采樣的個階段,電路檢測數據線上數據的傳輸。當檢測到有數據傳輸時,對傳輸數據的有效性進行確認。確認數據有效后,輸出高電平來指示采樣點有數據傳輸。

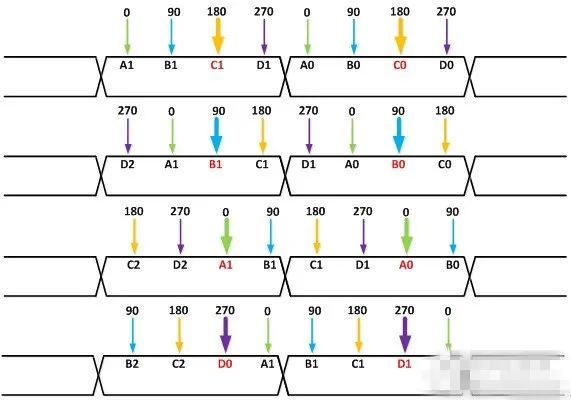

因為終有四個輸出,所以需要一個復用器來選擇數據。發送數據與采樣時鐘的對應關系如上圖所示,其對應關系分為4種情況,每種情況下對應一個的采樣時鐘,系統通過對數據邊沿位置信息的判斷,來確定哪路時鐘為采樣時鐘,并利用復用器從選定的時鐘域中選擇數據位,例如檢測電路確定從時鐘域A中采樣的數據有效,那么將時鐘域A中采樣的數據通過輸出端輸出。

3 結束語:

通過對純數字電路的CDR電路,在沒有硬核的支持下,完成了FPGA上SERDES的接口設計,并通過實驗的傳輸測試,在HR03的FPGA上,可完成100~200Mbps的數據傳輸。

?

?

?

?

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:基于FPGA芯片的SERDES接口電路設計

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636335

原文標題:基于FPGA芯片的SERDES接口電路設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高速車載SerDes企業完成新一輪融資,上汽入股

南芯科技發布車規級SerDes高速接口芯片SCP2550X系列

RS485接口電路設計要點

車載SerDes產業起飛!國產新品密集炸場

從SerDes到SoC,全場景適配的FCom差分晶振設計全解

時源芯微 接口濾波與防護電路的設計

FPGA從0到1學習資料集錦

FPGA的Jtag接口燒了,怎么辦?

車載SerDes重大突破,業內首款雙協議芯片誕生!

什么是SerDes?SerDes有哪些應用?

基于FPGA芯片的SERDES接口電路設計

基于FPGA芯片的SERDES接口電路設計

評論