這里將介紹SERDES的基本概念,并介紹SERDES相關(guān)的專有名詞:眼圖(Eye-diagram)、眼圖模板、抖動(dòng)(Jitter)、容忍度(tolerance)、功耗(Power Consumption)、預(yù)加重(Pre-emphasis)、均衡(Equalization)、8B/10B編碼等。

2018-01-30 08:55:54 24845

24845

速度最快的SerDes單一通道的帶寬已達(dá)112Gbps,支持PAM4編碼。如此高的速率,使得在整個(gè)系統(tǒng)中實(shí)現(xiàn)高速信號(hào)布線會(huì)面臨許多許多設(shè)計(jì)難題。

2020-03-22 15:37:00 4833

4833 Dialog推出了針對(duì)12V電機(jī)應(yīng)用的新型可配置混合信號(hào)IC(CMIC)SLG47105,該器件提供具有高電壓輸出的可配置模擬和可配置邏輯,采用2 mm x 3 mm QFN封裝。

2020-09-02 16:55:39 4792

4792 電子發(fā)燒友網(wǎng)報(bào)道(文/李寧遠(yuǎn))SerDes是SERializer串行器和DESerializer解串器的簡(jiǎn)稱,串行器/解串器在發(fā)送端將多路低速并行信號(hào)被轉(zhuǎn)換成高速串行信號(hào),經(jīng)過(guò)傳輸媒體,最后在接收端

2023-10-12 09:02:14 3513

3513 大家好:

現(xiàn)有6678與一片switch(IDT-cps1848)通信的的情況(6678和1848各一塊單板,通過(guò)高速接插件相連,已充分做到等長(zhǎng)等條件)。6678的參考時(shí)鐘為156.25MHZ,配置

2018-06-21 02:20:24

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立

2019-05-29 17:52:03

目前我們已經(jīng)發(fā)布了NXP的QorIQLS架構(gòu)系列的幾款平臺(tái),包含LS1046A、LS1043A、LS1028A、LS1012A。這幾款平臺(tái)都原生支持網(wǎng)口、PCIE、SATA等高速接口協(xié)議,很多

2021-12-20 06:01:37

SerDes的發(fā)送端TX的均衡原理是什么?怎樣利用高速接口SerDes去實(shí)現(xiàn)芯片間信號(hào)的有線傳輸?

2021-06-17 07:15:16

SERDES結(jié)構(gòu)是怎樣構(gòu)成的?高速SERDES接口在網(wǎng)絡(luò)方面有哪些應(yīng)用?

2021-04-28 07:19:38

SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 應(yīng)對(duì)未來(lái)高速

2021-11-12 06:46:26

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立

2019-10-23 07:16:35

Gowin 可配置功能單元(CFU)手冊(cè)主要描述了可配置功能單元的結(jié)構(gòu)、工作模式和原語(yǔ)。

2022-09-28 08:23:36

我看LS1028的serdes可以配置為2路PCIe3.0x2或1路PCIe3.0x4,請(qǐng)問(wèn)在哪兒配置,怎么更改配置呢,要改硬件電路嗎?沒(méi)有操作過(guò)這個(gè),請(qǐng)版主指點(diǎn)一下,謝謝。

2021-12-31 06:38:27

模式(使用帶有 SerDes 協(xié)議 0x1133 的 XFI)下運(yùn)行 PHY。現(xiàn)在我需要在運(yùn)行時(shí)在 1G 和 10G 之間切換。由于我無(wú)法在運(yùn)行時(shí)更改 RCW,我嘗試重新配置 SerDes 通道,但

2023-04-18 10:32:26

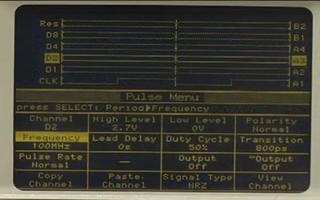

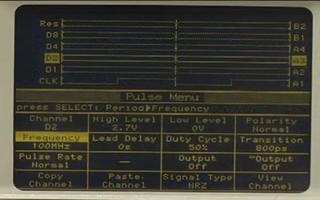

SerDes在93000平臺(tái)上量產(chǎn)測(cè)試。本文將介紹Nautilus UDI方案是如何實(shí)現(xiàn)高速SerDes測(cè)試的,包括UDI結(jié)構(gòu),輸入時(shí)鐘設(shè)計(jì),Load board設(shè)計(jì),socket選型等多個(gè)測(cè)試環(huán)節(jié)。

2021-05-10 06:58:55

,N=4,P=5,得到1G,選擇的是默認(rèn)high vco,

serdes pll配置MPY=20,N=4,rate選擇half,得到5G的line rate,請(qǐng)問(wèn)下這個(gè)有問(wèn)題么?

2024-12-13 08:02:07

1#ifndefCONFIG_H_2#defineCONFIG_H_34/*************************************************************************************************/5/****可配置參數(shù)...

2021-09-13 09:11:40

摘要針對(duì)FFT算法基于FPGA實(shí)現(xiàn)可配置的IP核。采用基于流水線結(jié)構(gòu)和快速并行算法實(shí)現(xiàn)了蝶形運(yùn)算和4k點(diǎn)FFT的輸入點(diǎn)數(shù)、數(shù)據(jù)位寬、分解基自由配置。使用Verilog語(yǔ)言編寫,利用ModelSim

2019-07-03 07:56:53

數(shù)字系統(tǒng)的設(shè)計(jì)師們面臨著許多新的挑戰(zhàn),例如使用采用了串行器/解串器(SERDES)技術(shù)的高速串行接口來(lái)取代傳統(tǒng)的并行總線架構(gòu)。基于SERDES的設(shè)計(jì)增加了帶寬,減少了信號(hào)數(shù)量,同時(shí)帶來(lái)了諸如減少布線

2019-05-21 05:00:13

針對(duì)高速無(wú)線數(shù)據(jù)通訊的實(shí)時(shí)性要求,提出采用FPGA來(lái)實(shí)現(xiàn)可配置均衡器的設(shè)計(jì),在設(shè)計(jì)過(guò)程中采用自頂而下劃分的設(shè)計(jì)方式,即方便了設(shè)計(jì)的需要,同時(shí)又滿足了性能的要求,在實(shí)際項(xiàng)目中收到很好的效果。

2021-04-29 06:48:32

技術(shù)所取代,而800G互聯(lián)技術(shù)更已經(jīng)近在眼前。帶寬需求連年暴漲,其底層的高速SerDes技術(shù)也因此備受矚目。 目前,速度最快的SerDes單一通道的帶寬已達(dá)112Gbps,支持PAM4編碼。如此高

2023-04-18 14:52:28

為 EMI 敏感和高速 SERDES 系統(tǒng)供電

2019-05-21 14:34:36

賽靈思 Artix-7 FPGA 是業(yè)界唯一的在低端器件上整合了高速收發(fā)器的方案,該方案提供了自適應(yīng)均衡、2D 眼圖以及IBIS-AMI仿真模型來(lái)簡(jiǎn)化針對(duì)成本敏感型應(yīng)用的高速串行設(shè)計(jì),觀看視頻,4分鐘教您搞定高速SerDes端口設(shè)計(jì)。

2016-07-27 17:29:59

請(qǐng)教:C6678的PCIE SRIO Hyperlink和SGMII模塊的配置中都涉及到對(duì)serdes模塊的配置,故希望知道以下幾個(gè)問(wèn)題:1、這些模塊的serdes是同一個(gè),還是各自有各自

2018-08-06 06:17:36

STM8可配置時(shí)鐘輸出寄存器

2020-11-10 08:03:29

請(qǐng)問(wèn)超高速SerDes在芯片設(shè)計(jì)中的挑戰(zhàn)是什么?

2021-06-17 08:49:37

的性能比以往的機(jī)架式儀器的性能要好。”Aeroflex 測(cè)試解決方案部門PXI產(chǎn)品經(jīng)理Tim Carey指出,“Aeroflex 3000 系列模塊化平臺(tái)具有靈活、高速的特點(diǎn),這為可配置儀器制定了一個(gè)新基準(zhǔn),為用戶帶來(lái)超乎想象的自由度。”

2019-06-28 06:39:18

(PCI Express root complex)標(biāo)識(shí),不可以配置沖突,舉例說(shuō)SerDes1配置為1163,SerDes2配置為5559,這是不可以的!因?yàn)镻CIe.1重復(fù)了。PCIe.nx4表示4條

2020-10-28 17:15:14

是RC(PCI Express root complex)標(biāo)識(shí),不可以配置沖突,舉例說(shuō)SerDes1配置為1163,SerDes2配置為5559,這是不可以的!因?yàn)镻CIe.1重復(fù)了。PCIe.nx4

2020-11-01 20:21:02

電路Bandgap/LDO/OSC/PLL/Serdes等的設(shè)計(jì)和仿真;3. 負(fù)責(zé)與版圖工程師溝通并完成電路的版圖設(shè)計(jì);4. 制定芯片的測(cè)試計(jì)劃,并在流片后配合芯片測(cè)試;5. 負(fù)責(zé)芯片設(shè)計(jì)過(guò)程中相關(guān)

2017-11-13 14:46:14

本文簡(jiǎn)要介紹了SoC 設(shè)計(jì)鏈面臨的挑戰(zhàn)以及對(duì)可配置IP 提出的新的要求。重點(diǎn)分析了如何利用Improv 系統(tǒng)公司開(kāi)發(fā)的VLIW架構(gòu)和包括Jazz DSP 平臺(tái)的工具套件進(jìn)行快速、低成本、高性能的

2009-12-14 10:25:55 14

14 串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)的帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

38 一種高速可配置實(shí)時(shí)總線的開(kāi)發(fā)及其應(yīng)用:為滿足工業(yè)生產(chǎn)中對(duì)現(xiàn)場(chǎng)總線柔性可重構(gòu)以及高速實(shí)時(shí)傳輸要求,討論了一種可在線配置高速實(shí)時(shí)總線的設(shè)計(jì)與實(shí)現(xiàn).本研究通過(guò)對(duì)SP

2010-03-18 15:56:36 20

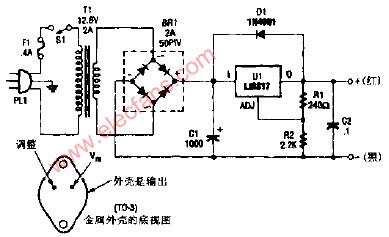

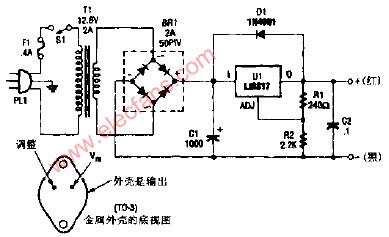

20 可配置電源

如果有必要的話,此可調(diào)

2009-09-30 12:07:59 895

895

可配置振蕩器,可配置振蕩器結(jié)構(gòu)原理是什么?

可配置振蕩器既具備可編程振蕩器交付時(shí)間短的優(yōu)勢(shì),又避免了其噪聲高的缺陷,其內(nèi)部結(jié)構(gòu)如圖2

2010-03-22 14:34:20 1018

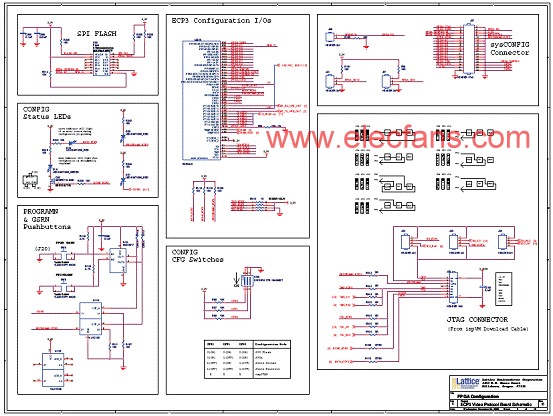

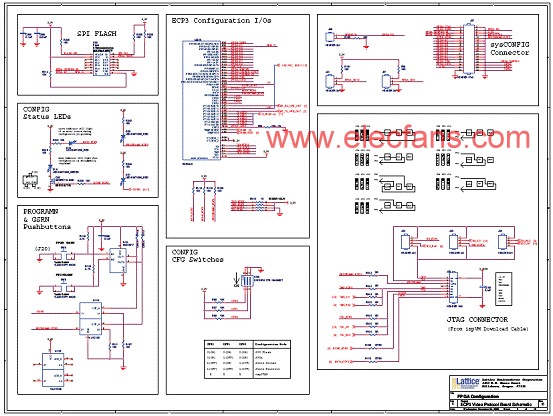

1018 本文介紹了LatticeECP3 FPGA系列主要特性,LatticeECP3-35簡(jiǎn)化方框圖以及LatticeECP3視頻協(xié)議板主要特性,方框圖和詳細(xì)的電路圖。

Lattice 公司的LatticeECP3 FPGA系列能提供高性能的特性

2010-10-15 15:09:04 3007

3007

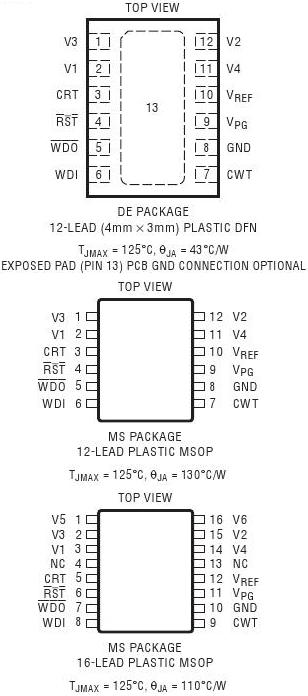

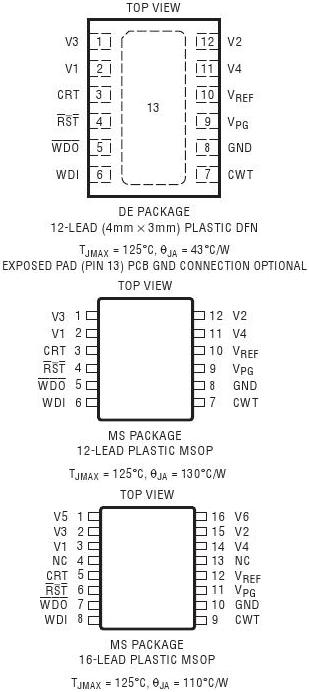

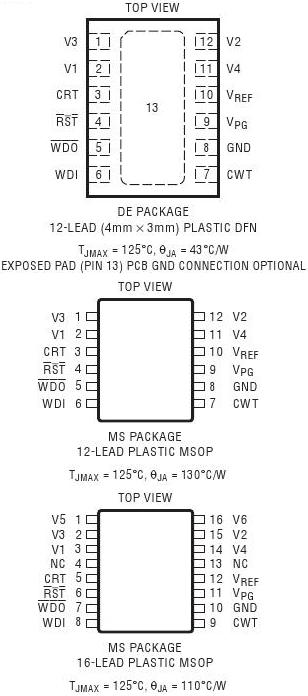

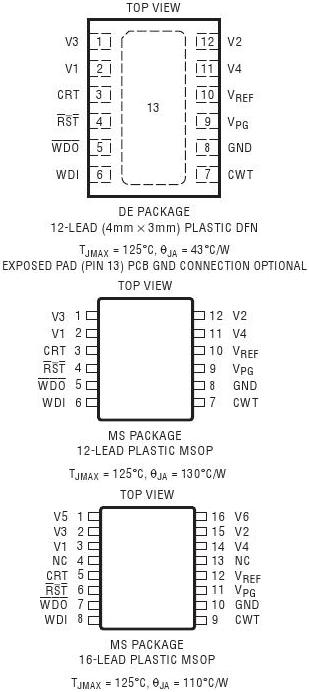

LTC2938描述

LTC®2938/LTC2939是可配置電源監(jiān)視器,面向那些具

2010-12-08 17:26:06 3291

3291

LTC2939描述LTC®2938/LTC2939是可配置電源監(jiān)視器,面向那些具有多達(dá)4個(gè)或6個(gè)需要進(jìn)行

2010-12-08 17:36:04 901

901

LatticeECP3系列是來(lái)自萊迪思半導(dǎo)體公司的第三代高價(jià)值的FPGA,在業(yè)界擁有SERDES功能的FPGA器件中,它具有最低的功耗和價(jià)格

2011-03-23 10:41:36 1465

1465 Xtensa可配置處理器架構(gòu)是可配置可擴(kuò)展的微處理器技術(shù),可以用于片上系統(tǒng)SOC設(shè)計(jì)。現(xiàn)在的SOC需要更高系統(tǒng)性能、更高輸入/輸出帶寬和更高功耗利用率

2011-04-19 11:51:16 2464

2464

萊迪思半導(dǎo)體公司(NASDAQ: LSCC)今天用宣布推出下一代LatticeECP4?FPGA系列,由其重新定義了低成本,低功耗的中檔FPGA市場(chǎng)

2011-12-02 09:02:59 950

950 致力于中端和低密度FPGA產(chǎn)品開(kāi)發(fā)的萊迪思半導(dǎo)體公司日前再推力作下一代LatticeECP4 FPGA系列。其具有6Gbps的SERDES、采用低成本wire-bond封裝、功能強(qiáng)大的DSP塊和具有基于硬IP的通信引擎,適

2011-12-14 09:58:45 1666

1666 萊迪思半導(dǎo)體公司日前宣布,即可獲取增加至非常成功的LatticeECP3 FPGA系列的低功耗、高速和迷你封裝器件。

2012-02-03 09:25:38 715

715 萊迪思半導(dǎo)體公司(NASDAQ: LSCC)近日宣布,即可獲取增加至非常成功的LatticeECP3?FPGA系列的低功耗、高速和迷你封裝器件。

2012-02-04 09:59:34 1019

1019 針對(duì)WIMAX系統(tǒng)中變長(zhǎng)子載波的特點(diǎn),通過(guò)采用流水線乒乓結(jié)構(gòu),以基2、基4混合基實(shí)現(xiàn)了高速可配置的FFT/IFFT。將不同點(diǎn)數(shù)的FFT旋轉(zhuǎn)因子統(tǒng)一存儲(chǔ),同時(shí)對(duì)RAM單元進(jìn)行優(yōu)化,節(jié)約了存儲(chǔ)空間;此外

2012-02-29 11:29:06 5

5 LatticeECP4 系列:具有高級(jí)通信引擎和強(qiáng)大的 DSP 模塊的低成本、低功耗 FPGA 新的LatticeECP4系列是第四代具有高級(jí)通信引擎和功能強(qiáng)大的DSP模塊的高可靠、低成本、低功耗FPGA。創(chuàng)新的Latt

2012-06-06 09:51:38 2515

2515 一種可配置的老化預(yù)測(cè)傳感器設(shè)計(jì)_梁華國(guó)

2017-01-07 16:06:32 0

0 針對(duì)FFT算法基于FPGA實(shí)現(xiàn)可配置的IP核。采用基于流水線結(jié)構(gòu)和快速并行算法實(shí)現(xiàn)了蝶形運(yùn)算和4k點(diǎn)FFT的輸入點(diǎn)數(shù)、數(shù)據(jù)位寬、分解基自由配置。使用Verilog語(yǔ)言編寫,利用ModelSim仿真

2017-11-18 06:32:43 12871

12871

傳統(tǒng)上,系統(tǒng)級(jí)芯片(SoC)設(shè)計(jì)師必須應(yīng)對(duì)剛性的非可配置核心技術(shù)。眾所周知,傳統(tǒng)的核心工藝在設(shè)計(jì)或制造過(guò)程中是不可配置的,并且不能按多種用途進(jìn)行定制。

2018-02-08 20:33:58 1808

1808

看看LatticeECP3 FPGA的功耗是多么的低,無(wú)論是在實(shí)驗(yàn)室中測(cè)量,還是利用萊迪思的功耗計(jì)算器軟件計(jì)算。 LatticeECP3是業(yè)界最低功耗的配備SERDES的FPGA。

2018-06-15 13:36:00 5850

5850

隨著通信技術(shù)的飛速發(fā)展,高速數(shù)據(jù)傳輸系統(tǒng)成為了當(dāng)前研究的熱點(diǎn),而高速 SERDES 接口芯片的研究則是其中一個(gè)重要的組成部分。SERDES 接口芯片的主要功能是將低速的并行信號(hào)轉(zhuǎn)換成為高速低壓差分信號(hào)(LVDS)并通過(guò)串行鏈路發(fā)送,同時(shí)能夠接收串行輸入 LVDS 數(shù)據(jù)并正確的轉(zhuǎn)換為低速并行信號(hào)。

2019-06-24 08:00:00 12

12 芯片功能的增加和數(shù)據(jù)吞吐量的要求, 促使芯片行業(yè)從較低數(shù)據(jù)率的并行連接, 轉(zhuǎn)向較高速度的串行連接。SERDES(Serializer-Dese rializer ,) 是經(jīng)高速差分對(duì),而不是經(jīng)較低

2020-10-09 17:25:07 20

20 LatticeECP3 (經(jīng)濟(jì)型加第三代)FPGA設(shè)備系列經(jīng)過(guò)優(yōu)化,以在經(jīng)濟(jì)的FPGA結(jié)構(gòu)中提供高性能功能,如增強(qiáng)的DSP架構(gòu)、高速SERDES和高速源同步接口。這種結(jié)合是通過(guò)器件結(jié)構(gòu)的進(jìn)步

2020-11-20 08:00:00 0

0 ADP2114: 雙通道2 A/單通道4 A、可配置同步降壓DC-DC調(diào)節(jié)器

2021-03-18 21:28:39 4

4 CN0314:采用微功耗儀表放大器的可配置4-20 mA環(huán)路供電發(fā)射器/接收器

2021-03-18 23:54:39 14

14 為 EMI 敏感和高速 SERDES 系統(tǒng)供電

2021-03-19 04:23:54 12

12 LTC3371:4通道8A可配置降壓型DC/DC,帶看門狗和上電重置數(shù)據(jù)表

2021-04-19 14:06:45 7

7 LTC3370:4通道8A可配置降壓型DC/DC數(shù)據(jù)表

2021-04-25 16:28:48 5

5 LTC3372:60V低智商降壓控制器加4通道8A可配置降壓DC/DC產(chǎn)品手冊(cè)

2021-04-27 14:48:41 3

3 可配置的7通道大功率PMIC

2021-05-08 10:46:21 1

1 帶按鈕控制的可配置喚醒定時(shí)器

2021-05-16 13:40:34 8

8 SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 應(yīng)對(duì)未來(lái)高速

2021-11-07 10:21:00 47

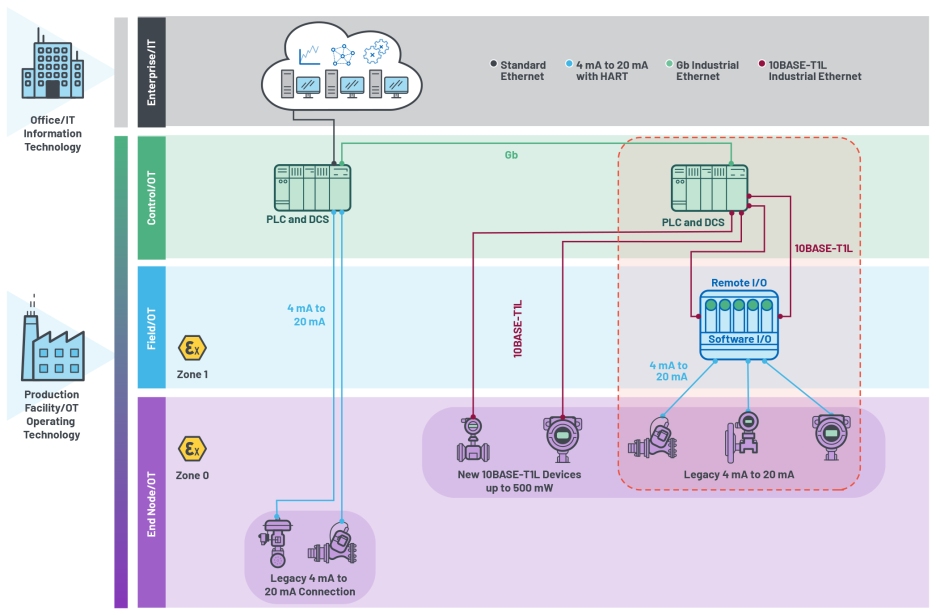

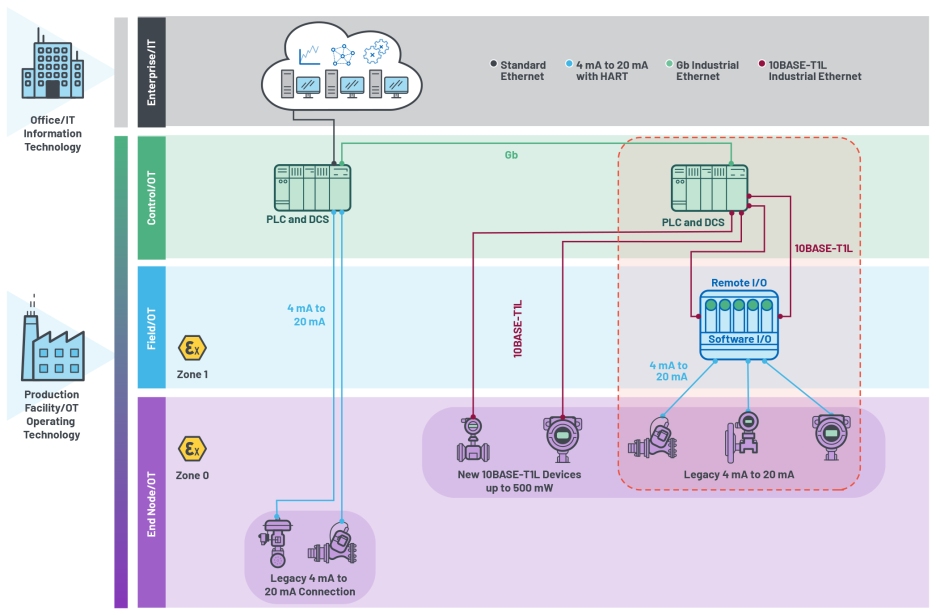

47 軟件可配置 I/O 系統(tǒng)提供從傳統(tǒng)模擬信號(hào)到工業(yè)以太網(wǎng)域的無(wú)縫過(guò)渡。

2022-08-12 15:37:07 1032

1032

電子發(fā)燒友網(wǎng)站提供《Gowin可配置功能單元(CFU)用戶指南.pdf》資料免費(fèi)下載

2022-09-14 14:21:31 2

2 電子發(fā)燒友網(wǎng)站提供《Compact系列CPLD可配置邏輯模塊(CLM)用戶指南.pdf》資料免費(fèi)下載

2022-09-26 10:06:25 4

4 電子發(fā)燒友網(wǎng)站提供《Logos系列FPGA可配置邏輯模塊(CLM)用戶指南.pdf》資料免費(fèi)下載

2022-09-26 09:29:56 17

17 可配置 AFE 改變電力線通信未來(lái)

2022-11-04 09:52:20 0

0 具有可配置電壓轉(zhuǎn)換的 4 位雙電源轉(zhuǎn)換收發(fā)器;三態(tài)-74AVC4T245

2023-02-16 20:43:02 0

0 具有可配置電壓轉(zhuǎn)換的 4 位雙電源轉(zhuǎn)換收發(fā)器;三態(tài)-74AVC4T245_Q100

2023-02-20 19:12:00 0

0 具有可配置電壓轉(zhuǎn)換的 4 位雙電源轉(zhuǎn)換收發(fā)器;三態(tài)-74AVCH4T245_Q100

2023-02-20 19:14:08 0

0 具有可配置電壓轉(zhuǎn)換的 4 位雙電源轉(zhuǎn)換收發(fā)器;三態(tài)-74AVC4TD245PW

2023-02-23 19:23:36 0

0 具有可配置電壓轉(zhuǎn)換的 4 位雙電源轉(zhuǎn)換收發(fā)器;三態(tài)-74AVC4TD245

2023-02-23 19:23:47 0

0 具有可配置電壓轉(zhuǎn)換的 4 位雙電源轉(zhuǎn)換收發(fā)器;三態(tài)-74AVCH4T245

2023-03-03 19:29:30 0

0 同時(shí)介紹一種采用光電集成技術(shù)的,即采用光SerDes而非電SerDes的高速收發(fā)器。

2023-04-01 09:28:58 3667

3667 首先我們要了解什么是SerDes,SerDes的應(yīng)用場(chǎng)景又是什么呢?SerDes又有哪些常見(jiàn)的種類?

2023-06-06 17:03:55 13765

13765

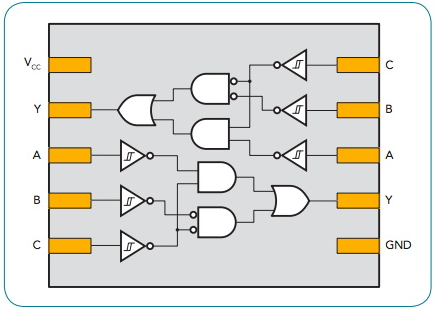

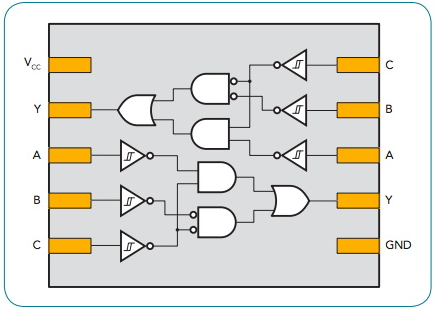

NXP 雙 PCB 可配置器件是一款具有施密特觸發(fā)器輸入的多門、多功能邏輯器件。每個(gè)器件包含兩個(gè)可配置門,每個(gè)器件可單獨(dú)配置為七種不同功能之一。每個(gè)系列(-57、-58、-97、-98)器件包含從 18 個(gè)獨(dú)特功能的總庫(kù)中選擇的 7 個(gè)邏輯功能。

2023-08-29 14:04:02 971

971

電子發(fā)燒友網(wǎng)站提供《PIC32系列參考手冊(cè)之可配置邏輯單元.pdf》資料免費(fèi)下載

2023-09-26 09:21:31 1

1 電子發(fā)燒友網(wǎng)站提供《可配置的4位雙電源轉(zhuǎn)換收發(fā)器74AVC4TD245PW數(shù)據(jù)手冊(cè).pdf》資料免費(fèi)下載

2024-01-31 09:40:29 0

0 電子發(fā)燒友網(wǎng)站提供《可配置多軌 PMIC TPS75003數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-04 14:11:24 0

0 電子發(fā)燒友網(wǎng)站提供《TPS650864可配置多軌PMU適用于多核處理器、FPGA和系統(tǒng)的TPS650861可配置多軌PMU數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-07 09:06:28 0

0 電子發(fā)燒友網(wǎng)站提供《具有可配置電壓轉(zhuǎn)換和3態(tài)輸出的4位雙電源總線收發(fā)器SN74AVCH4T245數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-05-31 09:22:19 0

0 電子發(fā)燒友網(wǎng)站提供《用于3D圖像的1至4可配置時(shí)鐘緩沖器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-08-23 10:43:55 0

0 電子發(fā)燒友網(wǎng)站提供《使用離散邏輯的可配置定時(shí)復(fù)位.pdf》資料免費(fèi)下載

2024-09-03 10:16:26 1

1 電子發(fā)燒友網(wǎng)站提供《如何使用可配置邏輯塊 (CLB) 實(shí)施定制串行接口.pdf》資料免費(fèi)下載

2024-09-09 10:07:48 0

0 電子發(fā)燒友網(wǎng)站提供《使用C2000可配置邏輯塊進(jìn)行設(shè)計(jì).pdf》資料免費(fèi)下載

2024-09-23 12:38:11 0

0 電子發(fā)燒友網(wǎng)站提供《74AVC4TD245-Q100具有可配置電壓轉(zhuǎn)換的4位雙電源轉(zhuǎn)換收發(fā)器規(guī)格書.pdf》資料免費(fèi)下載

2025-02-18 17:49:04 0

0 電子發(fā)燒友網(wǎng)站提供《74AVC4TD245具有可配置電壓轉(zhuǎn)換的4位雙電源轉(zhuǎn)換收發(fā)器規(guī)格書.pdf》資料免費(fèi)下載

2025-02-18 17:49:58 0

0 SerDes是一種功能塊,用于對(duì)高速芯片間通信中使用的數(shù)字化數(shù)據(jù)進(jìn)行序列化和反序列化。用于高性能計(jì)算(HPC)、人工智能(AI)、汽車、移動(dòng)和物聯(lián)網(wǎng)(IoT)應(yīng)用的現(xiàn)代片上系統(tǒng)(SoC)都實(shí)現(xiàn)了

2025-03-27 16:18:35 5285

5285

CDC1104是一個(gè) 1 到 4 可配置的時(shí)鐘緩沖器。該器件接受輸入?yún)⒖紩r(shí)鐘,并創(chuàng)建 4 個(gè)緩沖輸出時(shí)鐘,輸出頻率等于輸入時(shí)鐘的一半 頻率。四個(gè)控制輸入,S1、S2、S3、S4 時(shí)鐘輸出的可配置相位。

2025-09-16 09:37:34 658

658

概述 Millipacs? Plus 2mm Hardmetric連接器是一款極具創(chuàng)新性的產(chǎn)品,它提供了從3到25Gb/s的數(shù)據(jù)速率選擇,具備可配置和可擴(kuò)展的高速、低速信號(hào)、

2025-12-11 16:00:09 276

276

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論