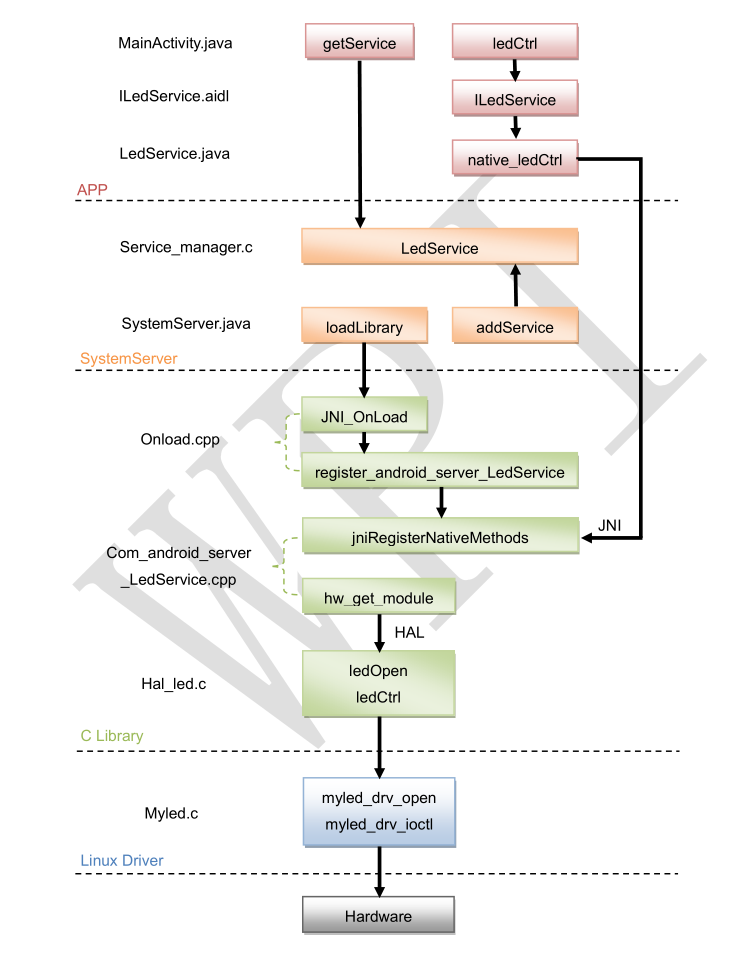

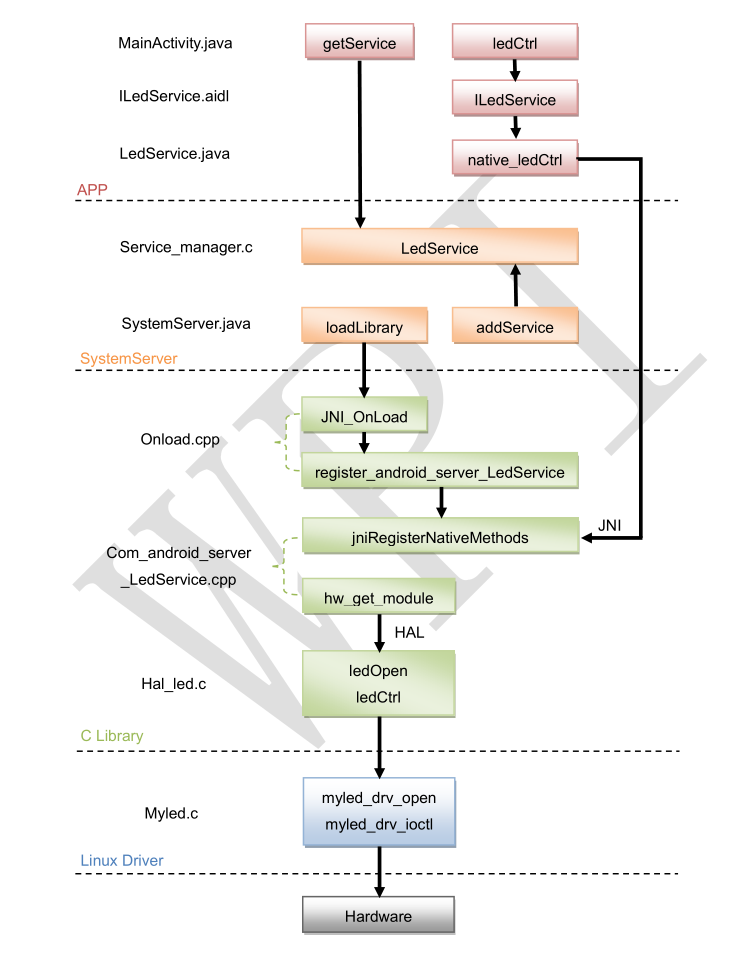

本文我們要講的是在用 i.MX8 平臺開發時,Android APP 如何進行訪問硬件驅動。

2023-12-04 13:50:10 3115

3115

FPGA 如何進行浮點運算

2015-09-26 09:31:37

的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮這種方法往往是不可取的,RTL驗證與驗證板設計必須是同步進行的,在驗證代碼出來時驗證的單板也必須設計完畢,也就

2012-08-11 10:27:54

制作成功,所以修改引腳分配是木有用的,這才是欲哭無淚的地方啊!!!!針對于這種情況,有沒有其他解決方案,而不是從新設計硬件PCB板的,求助!!!!!

2012-06-19 10:26:30

FPGA在Verilog程序寫完后,針對實物芯片,如何分配引腳?!在QtsII軟件中仿真后有引腳分配,但感覺和實際的引腳應該有區別吧?問,該如何區分?!

2013-04-03 13:14:13

分配引腳的四種方法:(Quartus II 13.0sp1(64-bit)) 1、常規方法,利用PinPlanner命令,適用于引腳使用比較少的工程,簡潔方便; 2、使用.csv文件進行引腳分配

2018-07-03 07:22:06

在FPGA芯片手冊中如何查詢芯片引腳分配在寫完硬件設計語言后進行I/O分配時,無法與芯片取得聯系

2018-10-04 08:28:39

FPGA如何對引腳進行分塊?是由VCC的電壓不同進行自行設計分塊?還是每個塊的引腳都是固定的?在進行DDR3與FPGA的硬件連接時,由FPGA的芯片手冊得采用SSTL_15電壓標準,即VDDQ

2021-11-29 16:10:48

分配fpga管腳時該怎么選擇,引腳有什么屬性需要考慮,quartus2中引腳有幾個屬性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-06-17 08:55:43

訪問。圖3 - 雙QSPI配置接口(11個引腳)允許配置位流在兩個QSPI器件之間進行分區,從而有效地將讀取數據傳輸速率提升一倍。當大型FPGA器件需要以最快的方式傳輸大配置(即高密度)配置比特流

2021-09-03 07:00:00

FPGA驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮

2024-01-10 22:40:14

在芯片的研發環節,FPGA驗證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從

2017-03-25 18:46:25

的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮這種方法往往是不可取的,RTL驗證與驗證板設計必須是同步進行的,在驗證代碼出來時驗證的單板也必須設計完畢,也就

2012-08-11 11:34:24

用tcl文件配置引腳后 點擊 Run 后就退出到代碼界面,然后查看了引腳是否分配成功發現沒有分配,這是怎么回事呢?要怎么解決?

2013-09-25 20:00:30

我是fpga開發板的新手,我想知道如何開始使用引腳分配,特別是u*** / serial引腳連接。任何其他pin信息都會有所幫助謝謝

2020-07-19 11:47:31

分配fpga管腳時該怎么選擇,引腳有什么屬性需要考慮,quartus2中引腳有幾個屬性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

Arduino Nano是什么?Arduino Nano有哪些引腳?Arduino Nano的引腳是怎樣進行分配的?

2021-10-19 07:59:21

有哪位大俠,能講解一下DMK如何進行硬件調試???(不是軟件設計,而是打開一個程序,要看看它運行到哪里了?該如何做?先前51單片機用的少,我查了一些資料,網上也搜了一下,都不是很具體。)

2014-05-03 16:06:59

EtherCAT總線運動控制器硬件是如何進行接線的?EtherCAT總線運動控制器有哪些參數設置?

2021-07-15 13:02:24

唯一一個由FPGA驅動到CPU的邏輯電路。我的推論是,由于該FPGA工程沒有對CPU相關的輸入輸出引腳進行時序約束,兩次編譯會導致雙向數據總線的輸出使能信號的響應差異,這一差異進一步影響了FPGA驅動

2012-02-24 10:49:28

USB OTG的工作原理是什么?IP設計原理是什么?如何進行IP模塊設計?USB OTG IP核有什么特性?如何對USB OTG IP核進行FPGA驗證?

2021-04-27 06:44:33

Intel 8253有哪些引腳?Intel 8253的工作模式是什么?Intel 8253與CPU是如何進行連接的?

2021-08-06 08:06:26

單片機和PLC的應用分別有哪些?PLC與單片機硬件通信的原理是什么?PLC與單片機硬件是如何進行通信的?

2021-08-12 07:34:23

在網上看到一個管腳分配的帖子,正好調自己的板子要用,方法夠簡單,共同學習,在編寫自己的管腳扽陪內容時候可以在AD中導出netlist,對應里面的內容進行簡單的編輯就可以做好自己的板子的TCL了。一

2018-07-03 12:56:11

STM32F407ZGT6的引腳是如何進行接線的?如何去實現STM32F407ZGT6串行通信的代碼?

2021-10-21 06:00:51

`Xilinx FPGA入門連載12:PWM蜂鳴器驅動之引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植復制

2015-10-14 12:23:31

管腳分配有兩種,一種就是手動,一個管腳 一個管腳的分配,還有一種就是使用腳本進行分配。一、手動引腳分配。菜單欄中:AssignmentsàPinPlanner出現如下的界面:在最下面,可以看到

2016-09-03 09:26:03

主存中存儲單元地址是如何進行分配的?存儲芯片的容量有多大?

2021-10-19 08:25:52

本文旨在以具體案例探討企業如何進行IPv6地址規劃與分配,從而合理和有效地使用IPv6地址資源。

2020-12-28 07:14:11

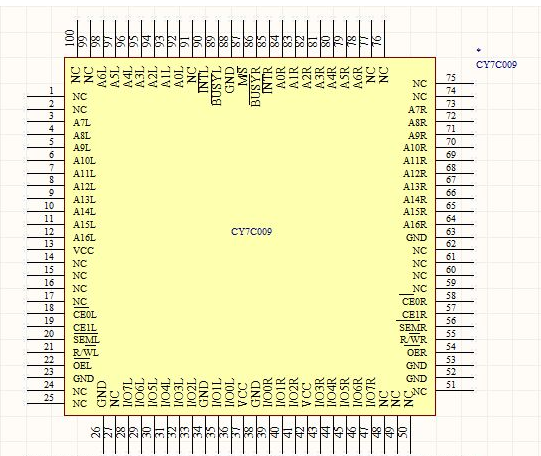

是基于什么?拍拍腦袋,隨心所欲?非也,引腳的分配一定是有理有據,那就是我們已經設計好的硬件原理圖。如圖3.21所示,這里FPGA所使用的時鐘信號ext_clk對應原理圖上的網絡名CLK_25M,它的FPGA引腳號是E15,那么我們就給它分配E15。 圖3.21 時鐘信號的引腳連接原理圖 `

2016-09-14 16:59:04

`例說FPGA連載33:PLL例化配置與LED之使用Tcl Console進行引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-17 17:50:15

`例說FPGA連載34:PLL例化配置與LED之使用TCL Scripts進行引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-23 09:34:42

剛開始學習fpga,對引腳分配的問題不是很理解,求高手給予幫助 例如fpga的線路板上23引腳接clk ,28引腳是空余的 ,那么在編程的時候我可以用 28引腳接clk 嗎?

2013-01-06 15:24:21

①蜂鳥FPGA約束文件是適用于MCU200T板子嗎?

②如果適用,那么在FPGA約束文件中的引腳約束是怎么對應到MCU 200T板子中?

eg:

比如這幾條約束是怎么對應到MCU 200T板子中的引腳呢?

2023-08-16 06:58:04

嵌入式LINUX驅動學習之12內核內存分配一、頭文件、函數及說明:一、頭文件、函數及說明://頭文件位置 : include/linux/slab.h/*申請內存函數:kmalloc()實現方式一般

2021-12-17 06:44:48

實際上輸出還是3.3V,我們不去設置它也行。圖7.6 引腳分配 查看SF-CY4開發板的原理圖,如圖7.7和圖7.8所示,這里BEEP對應FPGA引腳號是38,那么前面我們就在Location列輸入

2018-02-27 21:50:07

單片機存儲是如何進行分配的?stm32的啟動大致流程是怎樣的?有什么辦法來解決這個無效區域以縮小我們的固件大小呢?

2022-02-25 06:09:37

大家好,我剛開始學習FPGA并試圖弄清楚哪些FPGA引腳可以分配我的數據信號。我正在使用FPGA Spartan 6封裝TQG114器件LX9。查看產品規格,有102個可用的用戶I / O.這是

2019-04-23 06:55:23

在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是

2015-01-06 17:38:22

生成器進行計數,以實現完成短脈沖時鐘。任何人都可以指導我找正確的文章進行引腳分配然后將程序下載到主板上讓我做一些測試嗎?我是xilinx軟件的新手。我感謝你的幫助。謝謝

2019-10-29 10:09:50

文件為txt文件中共有10000個數據點,每個數據點由6個元素組成,分別對應6路信號即6條曲線,每個波形由200個數據點組成,每個文件中共有50個波形如圖后面那個 讀后標記 如何進行下次數據的讀取求解

2017-05-24 22:07:49

如何克服FPGA I/O引腳分配挑戰?

2021-05-06 08:57:22

我使用LX30T FF665-1 FPGA,我想使用GTP。當我在ISE 9.1.3中打開“assign package pins”時,我發現我無法為GTP分配端口的封裝引腳。我打開了“編輯約束

2020-05-29 14:39:22

引腳都將轉到fpga。我想將板作為第一步,以節省原型零件的費用,所以我試圖找出在不使用ISE YET的情況下為地址線,數據總線等分配引腳的最佳方法。不會使用RAM。謝謝!以上來自于谷歌翻譯以下為原文I

2019-01-21 06:02:55

請教一下,我想用ESP32-S2接8080顯示屏,對應的引腳需要怎么分配,有沒有相關的參考文檔?

2024-07-01 08:28:05

過程中必須平衡FPGA和PCB兩方面的要求,同時還要并行完成兩者的設計。 如果僅僅針對PCB或FPGA進行引腳布局優化,那么可能在另一方面引起設計問題。為了解引腳分配所引起的后果,需要以可視化

2024-07-22 00:40:11

計算機圖形系統的主要硬件是什么?軟件是如何進行配置的?

2021-10-11 09:35:59

在進行引腳分配時,看到如下圖,不知道P、n、L、D、Q、C、三角形、五邊形都代表什么意思,求大神解答,非常感謝

2019-03-20 06:35:15

想問問各位大神,在做FPGA的外圍電路時,除了專用引腳,每一個功能模塊對應的引腳是固定的嗎?還是說用戶I/O可以隨意分配引腳給外圍電路?

2019-04-08 08:43:16

我看第一個歷程就沒有講解對應的引腳分配實現,就是assignments-Pin Planner,難道是在其他的地方,我沒有找到嗎

2019-05-15 06:35:30

請問哈FPGA的輸入輸出信號跟端口引腳一定是一一對應的吧?

2019-04-16 04:46:22

、PF3對應三個LED燈,但我看板子上PF1、PF2、PF3對應的是三個引腳針,引腳到底怎么分配的?有文檔嗎?

2018-08-14 06:16:41

采用AFE0064和ADS8363加fpga結構,詳問如何進行控制?

2025-02-05 06:10:15

集成在一塊板子上的fpga和arm如何進行通信呢?

2022-11-07 15:31:04

在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮這種方法往往是不可取的,RTL驗證

2011-01-25 18:19:39 163

163 現在的FPGA向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。

2016-07-27 20:24:00 7371

7371 引腳和區域約束也就是LOC約束(location)。定義了模塊端口和FPGA上的引腳的對應關系。 那么我們應該怎么寫呢?

2018-07-14 02:49:00 11898

11898 現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

2017-05-18 10:51:54 31049

31049

眾所周知FPGA的硬件資源被劃分為若干個不同的bank,Xilinx一些高端的FPGA器件由22個甚至更多個bank組成,這樣設計主要是為了提高靈活性。FPGA的I/O支持1.8V、2.5V

2018-06-30 16:29:00 4602

4602 在芯片的研發環節,FPGA驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從

2017-11-25 07:38:18 3222

3222

在進行FPGA硬件設計時,引腳分配是非常重要的一個環節,特別是在硬件電路上需要與其他芯片通行的引腳。Xilinx FPGA從上電之后到正常工作整個過程中各個階段引腳的狀態,會對硬件設計、引腳分配產生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態進行分析。

2017-11-28 14:41:06 16918

16918

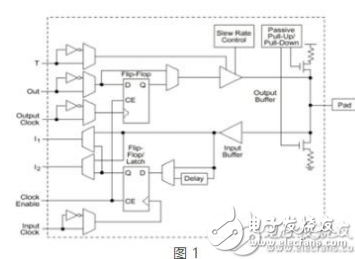

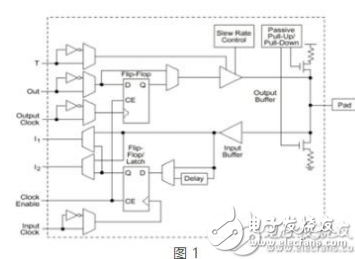

首先說IO standard:這個是用于支持對應不同的電平標準。FPGA IO口的電壓由IO bank上的VCC引入。一個bank上引入3.3V TTL電平,那么此時整個bank上輸出3.3V

2018-04-18 11:34:00 72013

72013

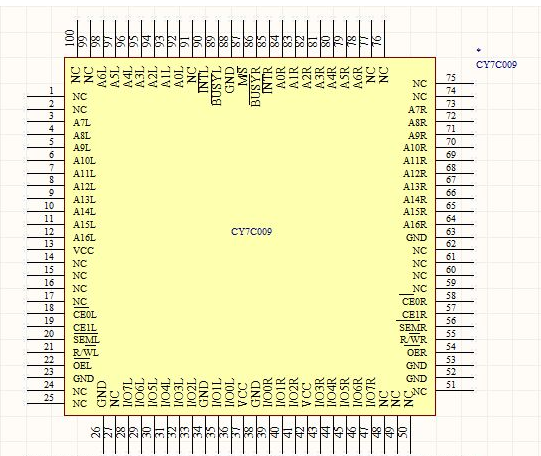

本文檔內容介紹了MagicSOPC主板FPGA-IO引腳分配表,供參閱

2018-03-15 15:50:59 7

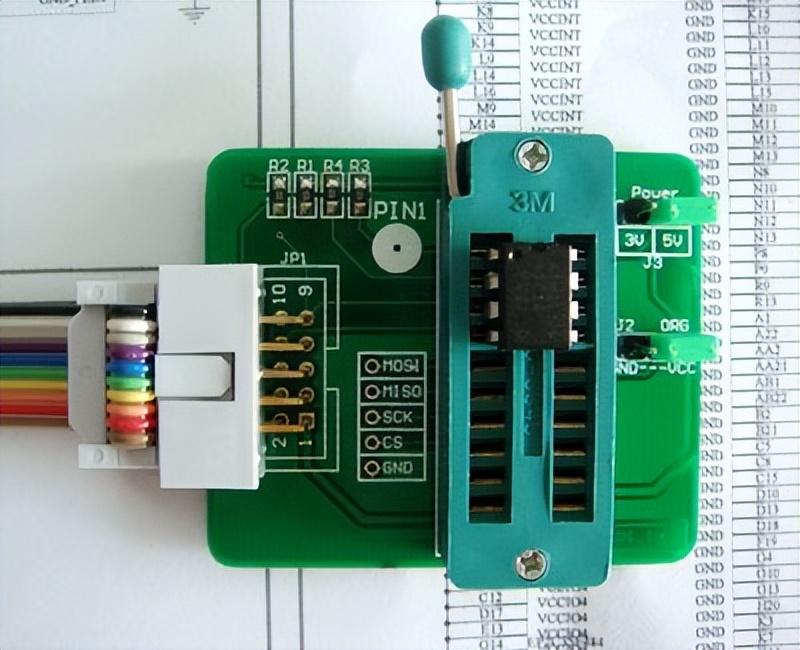

7 啟動馬達吧!快速,簡單,有趣!本視頻將向用戶展示如何進行硬件連接,啟動GUI并運行馬達。

2018-11-28 06:04:00 3640

3640 在進行FPGA硬件設計時,引腳分配是非常重要的一個環節,特別是在硬件電路上需要與其他芯片通行的引腳。Xilinx FPGA從上電之后到正常工作整個過程中各個階段引腳的狀態,會對硬件設計、引腳分配產生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態進行分析。

2020-09-02 09:20:21 16092

16092

介紹IO口與FPGA管腳對應關系表。

2021-03-18 10:02:26 12

12 AN-951: 使用SigmaDSP內置 GPIO引腳進行硬件控制

2021-03-19 09:00:36 2

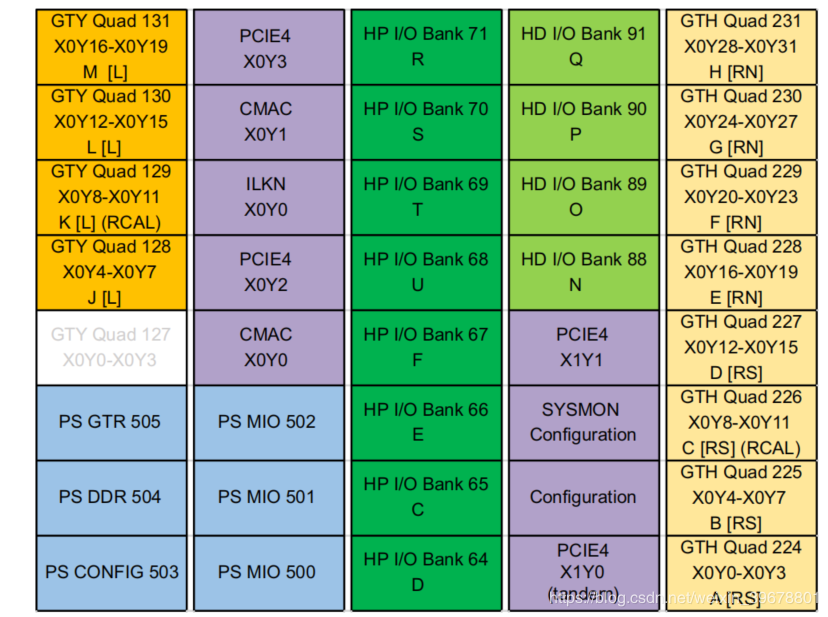

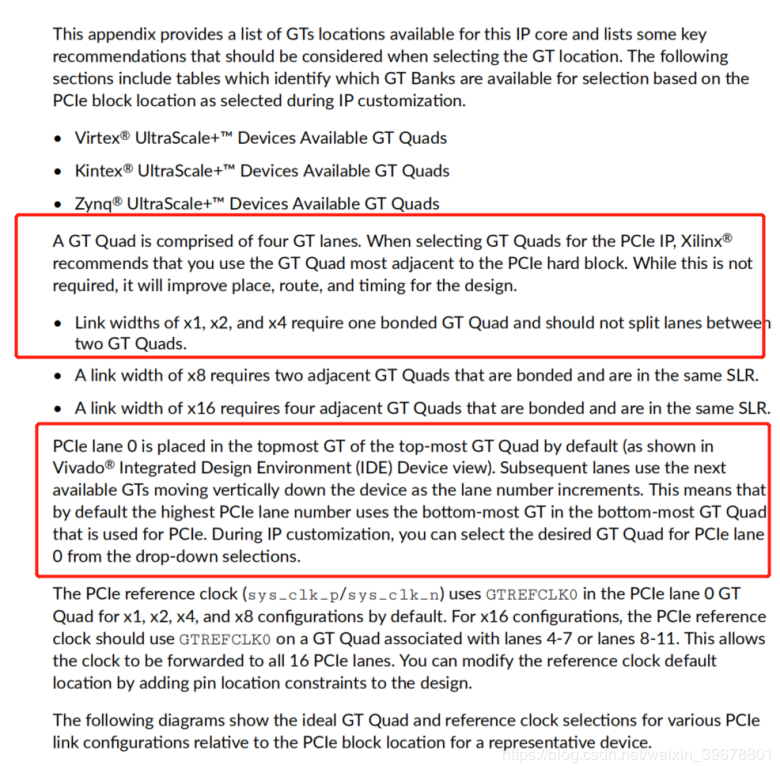

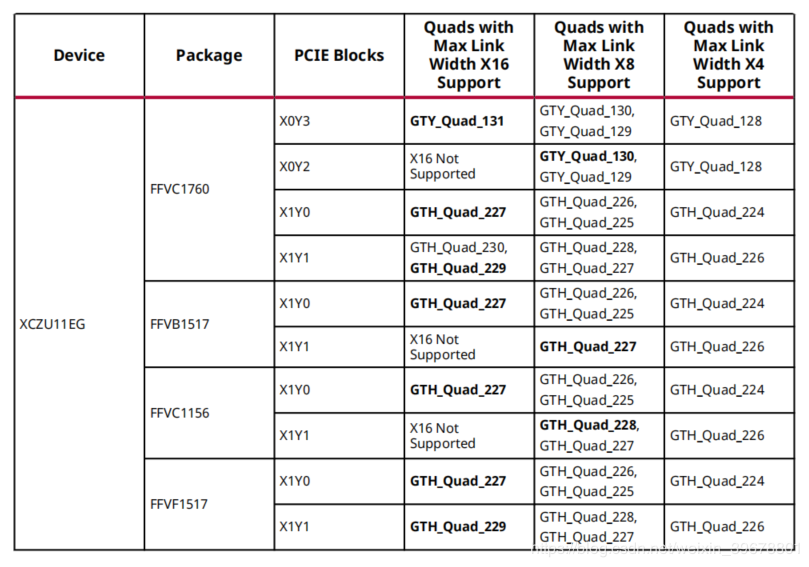

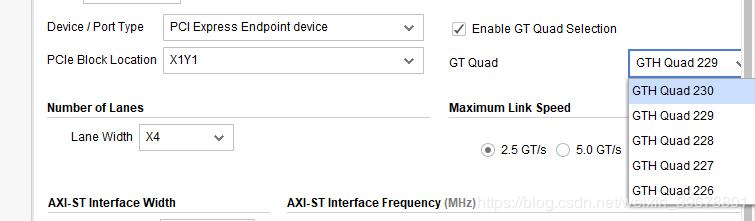

2 隨著FPGA的不斷發展,FPGA本身自帶的PCIE硬核的數量越來越多,本文以ZU11EG為例介紹,如何進行對應的硬件引腳分配。 設計目標:ZU11EG FFVC1760封裝,掛載4組NVME,接口為

2021-06-27 11:20:53 7533

7533

如何進行OPCDCOM配置(四會理士電源技術有限公司招聘)-如何進行OPCDCOM配置? ? ? ? ? ? ? ? ? ? ??

2021-09-18 14:23:09 11

11 Q: 如果系統中的FPGA/微處理器上只剩下一個GPIO,該如何進行模擬測量? A: 可以使用電壓-頻率轉換器代替模數轉換器。 在關注機器健康和其他物聯網(IoT)解決方案的現代應用中,隨著檢測功能

2021-11-21 10:02:52 2818

2818

而且現在的LUT都是4輸入或者6輸入,可以做成邏輯門的組合,跟普通的邏輯門個數肯定不會是一對一關系。今天我們來看下這個關系如果對應。

2022-11-01 09:11:29 1533

1533 ZYNQ擁有ARM+FPGA這個神奇的架構,那么ARM和FPGA究竟是如何進行通信的呢?本章通過剖析AXI總線源碼,來一探其中的秘密。

2023-02-16 09:26:57 14889

14889 在芯片的研發環節,FPGA驗證是其中的重要的組成部分,如何有效的利用FPGA的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發

2023-02-22 17:45:02 9859

9859 一個GT Quad由四個GT車道組成。為PCIe IP選擇GT Quads時,Xilinx建議您在最靠近PCIe硬塊的地方使用GT Quad。雖然這不是必要時,它將改善設計的位置,路線和時間。

2023-03-30 09:41:57 1444

1444 現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

2023-05-04 17:38:53 1487

1487 隨著 FPGA 的不斷發展,FPGA本身自帶的PCIE硬核的數量越來越多,本文以ZU11EG為例介紹,如何進行對應的 硬件 引腳分配。 設計目標:ZU11EG FFVC1760封裝,掛載4組NVME

2023-12-14 15:45:01 1381

1381 硬件調試是硬件系統設計、開發和制造過程中不可或缺的一環,旨在對可能出現的問題進行分析和解決。以下是進行硬件調試的一般步驟和方法: 一、準備階段 熟悉設計文檔:在開始調試之前,需要詳細閱讀和理解硬件

2024-11-10 10:17:40 2893

2893

電子發燒友App

電子發燒友App

評論