7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 3922

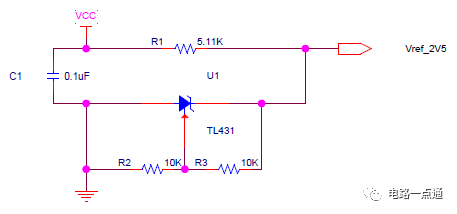

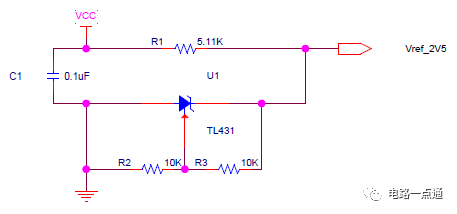

3922 本文將引導您采用極簡/簡單的方法進行開關電源設計,并介紹幾種利用 FPGA 資源和最小模擬電路發電的方法。

2023-02-20 09:14:50 1421

1421

“全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 1443

1443

FPGA 管腳分配需要考慮的因素FPGA 管腳分配需要考慮的因素 在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好

2012-08-11 10:27:54

解決方案工具包。它的主要工作是由軟件來自動生成、優化FPGA芯片的管腳分配,提高FPGA/PCB設計的工作效率和連通性。FSP完成兩項重要工作:一、可以自動生成FPGA芯片的原理圖符號(symbol

2011-10-18 11:44:31

FPGA管腳分配需要考慮的因素 FPGA 管腳分配需要考慮的因素 在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好

2012-08-11 11:34:24

在芯片的研發環節,FPGA驗證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從

2017-03-25 18:46:25

FPGA管腳分配需要考慮的因素.pdf

2012-08-20 19:23:04

FPGA的管腳主要包括:用戶I/O(UserI/O)、配置管腳、電源、時鐘及特殊應用管腳等。其中有些管腳可有多種用途,所以在設計FPGA電路之前,需要認真的閱讀相應

2019-09-18 07:34:49

各位大神,小弟最近在做一個項目,由于之前選用的FPGA資源不夠,現在需要將程序的資源占用率降下來。經過我的冥思苦想,也找不到好的方法,不知道各位大神平時工作中降低資源利用率的方法有哪些?求助啊!!!!

2015-04-04 00:32:57

的GC_CLKPIN,PAR就會報錯,反之,當一個信號分配的是GC_CLK PIN,無論是否扇出足夠大,都會加入IBUFG,這也其實是FPGA內部結構造成的,只有全局管腳上有IBUFG,所以只要該信號用了全局管腳

2019-07-09 08:00:00

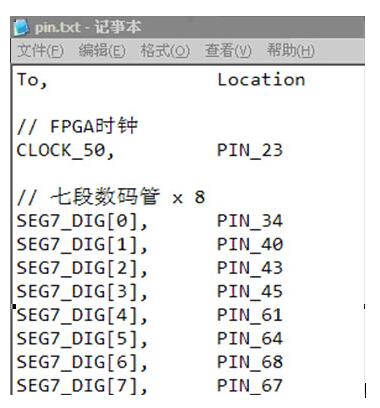

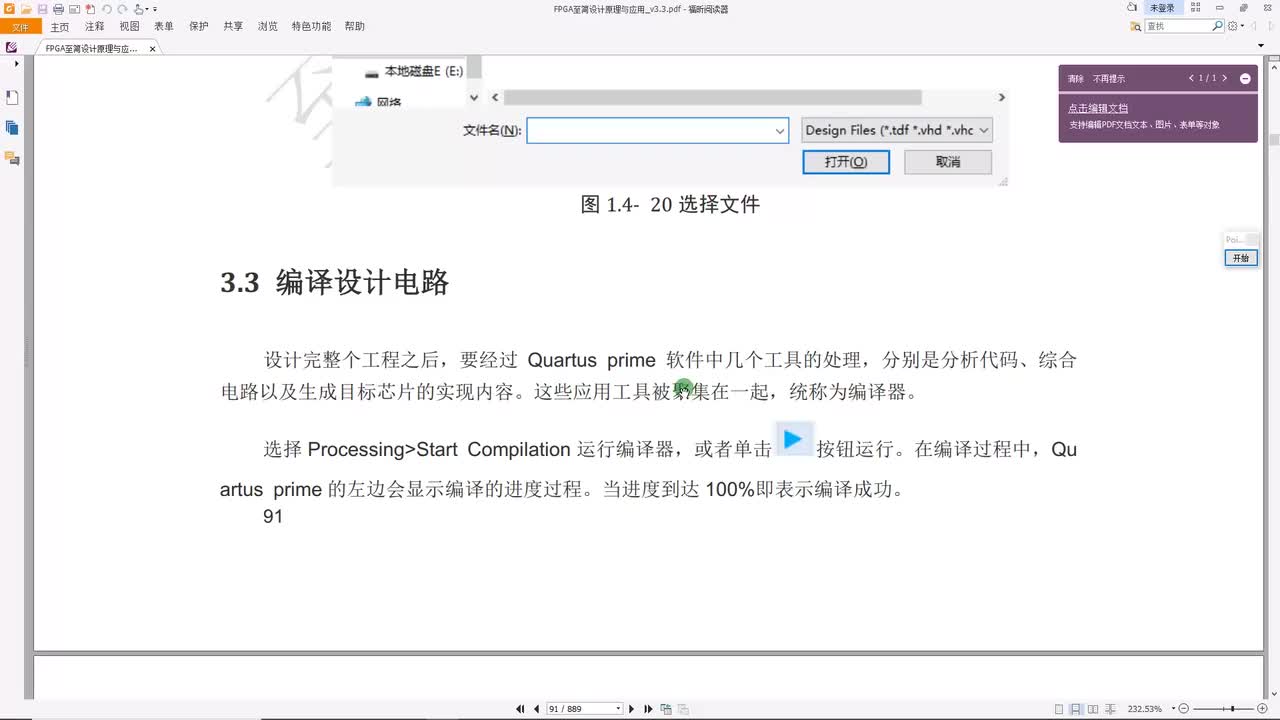

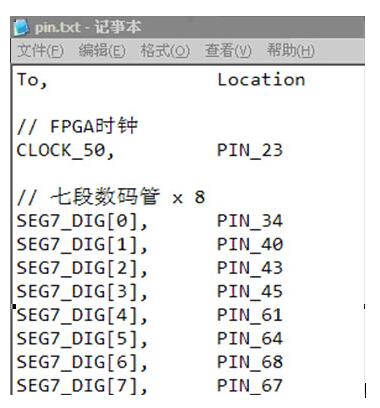

分配引腳的四種方法:(Quartus II 13.0sp1(64-bit)) 1、常規方法,利用PinPlanner命令,適用于引腳使用比較少的工程,簡潔方便; 2、使用.csv文件進行引腳分配

2018-07-03 07:22:06

FPGA驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮

2024-01-10 22:40:14

FPGA設計管腳分配注意點

2012-08-11 16:10:10

分配fpga管腳時該怎么選擇,引腳有什么屬性需要考慮,quartus2中引腳有幾個屬性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

NoC 去替代傳統的邏輯去做高速數據傳輸和數據總線管理。· 增加了 FPGA 的布線資源,對于資源占用很高的設計有效地降低布局布線擁塞的風險。· 實現真正的模塊化設計,減小 FPGA 設計人員調試

2020-09-07 15:25:33

管腳分配手冊,,

2017-09-30 09:08:11

BANK4 BANK5 掛了2片DDR2 芯片,分配好管腳編譯后QUARTUS FITTING報錯:Error (169223): Can't place VREF pin V9

2014-11-20 15:55:52

ARM在片上資源確定的情況下,能否具備類似FPGA自由分配管腳功能的能力?比如說集成UART的TX/RX可以分配到任意管腳,而并不是只能分配到指定的幾個管腳?謝謝

2022-08-01 14:17:49

求助大神!!!FPGA對于DDR3讀寫,FPGA是virtex6系列配置MIG IP 核時,需要管腳分配1.原理圖上dm是直接接地,管腳分配那里該怎么辦2.系統時鐘之類的管腳分配,是需要在原理圖上找FPGA與DDR3之間的連線嗎?還是?

2018-03-16 18:45:10

、摘要 將Quartus II中FPGA管腳的分配及保存方法做一個匯總。 二、管腳分配方法FPGA 的管腳分配,除了在QII軟件中,選擇“Assignments ->Pin”標簽(或者點擊按鈕

2018-07-03 12:56:11

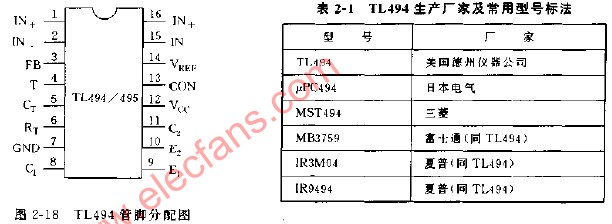

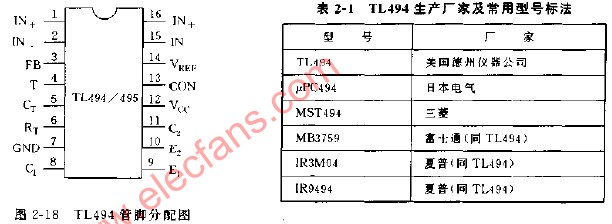

TL494管腳分配圖

2019-03-28 08:21:09

`Xilinx FPGA入門連載12:PWM蜂鳴器驅動之引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植復制

2015-10-14 12:23:31

管腳分配過后 編譯 在第二步布局布線的時候出現Error: Following feature(s) of I/O pin ~ALTERA_ASDO_DATA1~ has invalid

2013-08-16 14:40:55

使用xilinx spartan6,在工程中使用原語生成DDR控制器mig文件,DDR數據管腳定義發生改變,需要重新分配管腳,求告知,這個管腳分配要怎么弄

2016-07-19 09:54:37

`例說FPGA連載32:PLL例化配置與LED之使用Pin Planner進行引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-14 16:59:04

`例說FPGA連載33:PLL例化配置與LED之使用Tcl Console進行引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-17 17:50:15

初學者如何有效的閱讀FPGA的相關文檔?對于一個初學者,只是簡單的學過數電和verilog語法。在FPGA的使用上只會設計串口、I2C之類的簡單應用。FPGA的內部可能有非常多的資源,這些硬件資源

2019-09-30 17:44:24

`勇敢的芯伴你玩轉Altera FPGA連載38::Verilog代碼風格之雙向管腳的控制代碼特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-01-08 20:58:09

`勇敢的芯伴你玩轉Altera FPGA連載49:PWM蜂鳴器驅動之引腳分配特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD

2018-02-27 21:50:07

使用說明書V1.0中,這兩個管腳都定義為“axp_ctrl”想請教解惑,1、雙網口如何分配OTG相關管腳?2、所謂axp_ctrl的管腳分配如何體現? 或者應該從哪里可以找到相關的解釋信息?

2022-01-05 07:04:12

在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是

2015-01-06 17:38:22

;另一方面,已經分配或指配給現有很多無線業務的頻譜卻在時間和空間上存在不同程度的閑置。那么,如何有效地盤活那些閑置的頻譜資源,解決這一制約無線通信發展的新瓶頸?美國科學家Joseph Mitola博士提出了認知無線電(CR)的概念。

2019-08-02 08:21:06

時鐘信號與捕捉寄存器的有效數據窗口(從時序圖測量)之間的補償。Clk_offset = DlyRelSU – EdgeOffset利用上述公式,我們可以確定FPGA開發系統中PLL的相位偏移量,并執行

2009-04-14 17:03:52

求皓石FPGA開發板A4-PLUS原理圖或管腳分配表。

2020-10-13 18:17:10

spark動態資源分配

2019-05-23 08:36:02

盡量置于盡相關資源最近的地方。 然后看一下能否將某些I/O信號組合到接口,這對于引腳分配很有幫助。 最后,確定FPGA的配置模式。

步驟2: 定義引腳布局要求

一旦了解了主要的FPGA接口并創建

2024-07-22 00:40:11

至芯科技之altera 系列FPGA教程 第十四篇 分配管腳

2016-08-11 03:33:10

使用說明書V1.0中,這兩個管腳都定義為“axp_ctrl”想請教解惑,1、雙網口如何分配OTG相關管腳?2、所謂axp_ctrl的管腳分配如何體現? 或者應該從哪里可以找到相關的解釋信息?從數據手冊和原廠

2022-01-13 07:24:39

動態資源控制就是通過傳輸信道重配置、無線承載(RB重配置)等手段動態控制無線資源的過程,從而達到資源合理分配和有效利用。本章通過舉例方式說明動態資源控制流程

2009-05-30 17:18:10 5

5 網格資源調度和分配是一個非常復雜而且重要的研究問題,傳統的集中式管理方法很難適用于網格計算環境,基于經濟模型的資源和分配調度成為當前的研究熱點。文章分析了資

2009-08-07 08:59:43 17

17 針對OFDMA系統,在整數比特分配及用戶吞吐量公平分配的約束下,提出使系統吞吐量達到最大的有效無線資源優化方案,算法的仿真結果表明本文方法的有效性。關鍵詞:OFDMA;無

2010-01-17 09:40:58 23

23 在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約

2010-06-24 17:43:35 29

29 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 TL494管腳分配圖

2009-10-14 16:21:00 5004

5004

在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮這種方法往往是不可取的,RTL驗證

2011-01-25 18:19:39 163

163 OFDM資源分配概述

2011-11-11 17:32:32 19

19 通過實例在Matlab中展現了基于動態規劃法,解決電力資源合理分配的問題,使得現實中電力資源的分配問題得到簡化和程序化。結果顯示,動態規劃法在電力資源的合理分配問題上比較實用

2011-12-07 14:15:08 19

19 本文主要介紹了在FPGA開發過程中管腳分配時需要考慮的一些實際因素,減少后續開發過程中發生一些細節性的錯誤。

2016-05-25 10:01:13 18

18 電子專業單片機相關知識學習教材資料——使用tcl文件分配器件與管腳

2016-08-08 17:03:24 0

0 管腳分配手冊FPGA資料,又需要的下來看看

2016-08-09 14:45:44 65

65 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 設計過FPGA的原理圖,看FPGA的手冊,說管腳的分配問題,如時鐘管腳要用GC類管腳,而且單端時鐘輸入時要用P類型的管腳,不能用N類型管腳等等。

2017-02-11 03:48:34 12613

12613

基于令牌的共享資源分配算法_雷鳴

2017-03-16 10:53:10 0

0 資源之規劃。 由于物理層可用的帶寬較LTE少(180kHz一個載波),物理層程序也較以往大不相同,考慮到NB-IoT增強信號覆蓋需求,因此3GPP標準制定團隊利用「重復傳送」之方式獲取時域之增益,達到

2017-11-29 14:49:01 1460

1460

控制動態資源分配過程。首先,獲取歷史執行數據反饋和應用全局變量;然后,進行資源增減計算;最后,進行資源增減執行。實驗結果表明,所提策略能夠有效調整應用資源配額,且在穩定數據流和不穩定數據流兩種情況下,其處理延時相比原Spark平臺的Strea

2017-12-01 15:06:43 0

0 在對用戶的任務進行計算資源分配時,為了有效提高計算資源的利用效率,減少任務執行所需要的成本,提出了一種基于效益博弈的云計算資源動態可協調分配機制。該機制采用時間矩陣和費用矩陣作為任務效益的衡量指標

2017-12-06 17:21:17 0

0 本文針對目前云數據中心主機服務器在空轉時間段對能源消耗巨大的問題,建立了虛擬資源申請一分配模型,提出了一種虛擬資源分配的策略。該策略在滿足用戶需求前提下,對主機服務器最大化利用,以此來降低基礎設施

2017-12-08 10:15:39 0

0 針對云數據中心資源分配不均、效率不高、資源錯位等問題,為了滿足不同用戶的需求,達到多種資源分配的公平性,實現資源的高效利用,提出了全局優勢資源公平( GDRF)分配算法。GDRF算法采用多輪分配

2017-12-11 16:46:48 0

0 針對基于案例推理的動態資源分配的實際應用問題,本文利用SQL2008數據庫存儲案例、多目標優化結果以及效益函數,在MFC界面上動態顯示優化過程。VC++6.0選用ADO數據庫訪問技術訪問

2017-12-27 15:59:46 0

0 隨著無線通信的快速發展和移動通信終端的普及,適用于通信的無線電頻譜大多已經被分配占用,無線電頻譜資源變得日益稀缺。然而,另一方面,被授權使用的頻譜利用率卻很低,在某些時段、某些地點,這種情況頻譜浪費

2018-01-10 15:08:38 0

0 認知無線電是目前解決頻譜資源需求矛盾的一種有效技術。認知無線電網絡中,認知用戶可在不影響授權用戶工作的前提下,機會使用空閑頻譜。頻譜分配主要關注對感知到的空閑頻譜進行有效分配,提高頻譜資源的利用

2018-01-12 11:06:40 0

0 問題。 云計算服務提供者希望系統資源可以得到有效的分配、利用,例如,當某個虛擬機的資源需求量增加,可以利用其他空閑虛擬機的剩余資源,防止因資源分配不均衡造成瓶頸,從而影響用戶任務執行的費用和時間;從用戶的角

2018-01-18 16:16:56 0

0 算法對毫微微用戶和宏用戶分別進行子信道分配;利用分布式功率分配算法對完成信道分配的系統進行功率分配。仿真結果表明,該機制有效地抑制了Macro-Femto網絡中存在的跨層干擾及同層干擾,提升了平均速率,同時滿足了用戶的速率公平性需求,使用戶獲得更高的滿意度。

2018-01-26 17:58:23 0

0 認知無線電( CR)資源分配中二級用戶對主用戶造成的干擾源于兩方面,即帶外頻譜泄露和頻譜感知錯誤。濾波器組多載波( FBMC)技術和正交頻分復用(OFDM)技術相比,FBMC帶外泄露較小,頻譜利用

2018-02-27 14:28:33 0

0 ,據此在許可時間段內對K個接入路由器集合元素進行路由和資源分配,從而實現對未來后個目的地進行托管傳送。NS2平臺仿真實驗表明,在業務流量過飽和區域,可獲得延時和吞吐量等性能的近線性變化,總有效帶寬利用率超過DTN多播路由方案

2018-02-27 17:12:58 0

0 針對大規模多輸入多輸出(MIMO)正交頻分多址(OFDMA)下行移動通信系統,提出了一種基于能效最優的資源分配算法。所提算法在采用迫零(ZF)預編碼的情況下,以最大化系統能效的下界為準則,同時考慮

2018-03-12 14:14:12 0

0 本文考慮經典的單蜂窩超密集網絡場景,即單個蜂窩內擁有大量UE(如校園和辦公室)。用戶不僅可以通過傳統的蜂窩鏈路從基站獲取數據,也可以通過D2D鏈路從鄰近的用戶處獲取。考慮到移動用戶的具體位置是實時變動的,本文利用動態的CRP算法來對用戶分組和資源分配。

2018-03-12 16:58:43 8774

8774

將Quartus II中FPGA管腳的分配及保存方法做一個匯總。本文首先介紹了FPGA 的管腳分配方法,其次介紹了Quartus II自動添加管腳分配的方法,最后闡述了FPGA管腳分配文件保存方法,具體的跟隨小編一起來了解一下吧。

2018-05-16 11:44:41 52640

52640

窄帶蜂窩物聯網(NB-IoT)技術發 展迅猛,與原有的無線通信協議相比, NB-IoT的頻譜帶寬僅有180 kHz,因此,如何更有效地使用資源或頻譜(即資源分配和調度)成為NB-IoT技術的關鍵問題

2018-11-15 11:32:22 6

6 針對各種智能設備在移動蜂窩網絡中的普及及移動流量需求日益增長的問題,研究控制無線電帶寬并將其分配給多個無線電用戶設備,提出了一個基于軟件定義網絡(SDN)的資源分配框架,以及LTE/WLAN多無線電網絡中異構資源分配算法。

2018-11-15 11:32:39 10

10 在社會和科學技術日益發展的今天,電力資源的生產和分配成為人們所關注的問題之一,而發電機組的配置對其具有直接的影響。因此,為滿足社會對電力資源的需求,將一日內的 24 小時分為七個時間段,進行合理的生產和分配研究。

2018-12-04 14:53:28 4401

4401 英國蓋特威克機場計劃今年8月開展一項新的試點項目——機器人代客泊車服務,以便更加有效地利用機場的停車資源。

2019-01-27 09:21:02 2914

2914 在使用FPGA過程中,通常需要對資源做出評估,下面簡單談談如何評估FPGA的資源。

2019-02-15 15:09:05 4334

4334 管腳是FPGA重要的資源之一,FPGA的管腳分別包括,電源管腳,普通I/O,配置管腳,時鐘專用輸入管腳GCLK等。

2019-06-28 14:34:07 4404

4404 在使用 FPGA 過程中,通常需要對資源做出評估,下面簡單談談如何評估 FPGA 的資源。 FF 和 LUT 的數目:這個在寫出具體代碼之前,初學者通常沒法估算,但資深 FPGA 工程師會估算出一

2020-12-28 07:59:00 8

8 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 16

16 進行改進,設計聯合卸載決策與資源分配的 Improve-eGA算法。實驗結果表明,與 All local、 All offloadRANDOM和CGA等算法相比, Improve-eGA在迭代次數、任務周期數、任務傳輸數據量等影響因素下系統總成本均為最低,驗證了所提策略的有效性

2021-03-11 10:20:49 9

9 引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源

2021-03-22 10:16:18 6115

6115

為充分利用位于網絡邊緣各類設備上的閑散資源,同時擺脫傳統中心化管理模式帶來的單點故障及信任問題,需要以一種去中心化的模式對其進行有效管理和調配。區塊鏈因其在數據維護方面的去中心化、難以被篡改和可追溯

2021-03-25 14:19:53 20

20 范圍,利用屬性加密理論保護交易數據。在此基礎上,采用改進的蟻群算法為用戶合理規劃資源分配路徑從而實現頻譜資源的多目標分配。實驗結果表明,該機制可以為用戶的交易數據提供細粒度的保護,且具有較高的社會效益和較低的系

2021-04-27 14:23:44 6

6 現代超標量處理器通常設置有多套計算部件攴持指令并行執行,以提高程序的運行效率。運算資源分配策略在很大程度上決定了處理器能否充分利用計算部件并行加速計算,具有重要作用。就指令調度以及運算資源分配

2021-05-13 10:44:40 15

15 用戶請求的總成本并將其上傳至資源分配模塊,結合定價機制達到資源利用的最大化和用戶請求成本的最小化。仿真結果表明,該策略能提髙衛星網絡資源利用率及分配公平性,最大限度地實現資源的潛在價值。

2021-05-28 10:39:24 3

3 為在不完美頻譜檢測環境下對資源進行優化分配,提出一種分布式認知無線電網絡資源分配算法。根據葉斯理論給出子載波狀態信任指數與統計平均干擾功率的概念,利用拉格朗日對偶分解理論,將原分配問題分解為獨立的子

2021-06-11 11:25:28 11

11 基于拍賣的共享經濟預約模式資源分配

2021-06-11 15:11:42 3

3 容器云中基于改進遺傳算法的資源分配策略綜述

2021-06-29 16:02:45 5

5 【正點原子FPGA連載】第三章 硬件資源詳解 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-11-21 14:06:03 19

19 (06)FPGA資源評估1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA資源評估5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 FPGA基礎資源之IOB的應用 1.應用背景 在我們做時序約束時,有時候需要對FPGA驅動的外圍器件進行input_delay/output_delay進行約束。不知道,大家有沒有被以下這種

2022-12-25 16:30:02 6142

6142 在芯片的研發環節,FPGA驗證是其中的重要的組成部分,如何有效的利用FPGA的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發

2023-02-22 17:45:02 9859

9859 電子發燒友網站提供《PyTorch教程4.7之環境與分配轉變.pdf》資料免費下載

2023-06-05 15:40:45 0

0 FPGA的BRAM和LUT等資源都是有限的,在FPGA開發過程中,可能經常遇到BRAM或者LUT資源不夠用的情況。

2023-08-30 16:12:04 5313

5313

fpga芯片命名規則 FPGA芯片的命名規則因制造商和系列產品而異,但通常遵循一定的規律和格式。以下是一般情況下FPGA芯片命名規則的一些主要組成部分: 制造商標識:芯片名稱通常以制造商的名稱或縮寫

2024-03-14 16:54:17 3116

3116

電子發燒友App

電子發燒友App

評論