12.1前言

ZYNQ擁有ARM+FPGA這個(gè)神奇的架構(gòu),那么ARM和FPGA究竟是如何進(jìn)行通信的呢?本章通過剖析AXI總線源碼,來一探其中的秘密。

12.2AXI總線與ZYNQ的關(guān)系

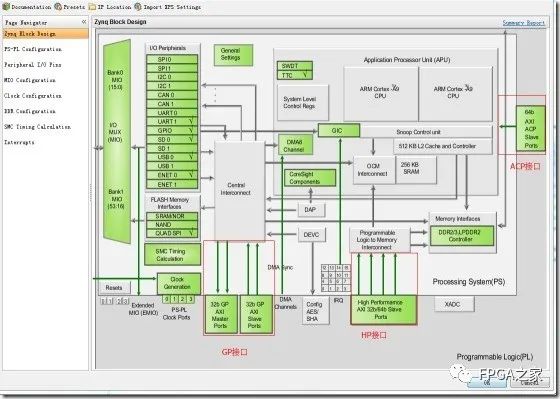

AXI(Advanced eXtensible Interface)本是由ARM公司提出的一種總線協(xié)議,Xilinx從6系列的FPGA開始對(duì)AXI總線提供支持,此時(shí)AXI已經(jīng)發(fā)展到了AXI4這個(gè)版本,所以當(dāng)你用到Xilinx的軟件的時(shí)候看到的都是“AIX4”的IP,如Vivado打包一個(gè)AXI IP的時(shí)候,看到的都是Create a new AXI4 peripheral。

到了ZYNQ就更不必說了,AXI總線更是應(yīng)用廣泛,雙擊查看ZYNQ的IP核的內(nèi)部配置,隨處可見AXI的身影。

12.3AXI總線和AXI接口以及AXI協(xié)議

總線、接口和協(xié)議,這三個(gè)詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。

總線是一組傳輸通道,是各種邏輯器件構(gòu)成的傳輸數(shù)據(jù)的通道,一般由由數(shù)據(jù)線、地址線、控制線等構(gòu)成。接口是一種連接標(biāo)準(zhǔn),又常常被稱之為物理接口。

協(xié)議就是傳輸數(shù)據(jù)的規(guī)則。

12.3.1AXI總線概述

在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當(dāng)然用的都是AXI協(xié)議。其中三種AXI總線分別為:

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數(shù)據(jù)突發(fā)傳輸;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個(gè)輕量級(jí)的地址映射單次傳輸接口,占用很少的邏輯單元。

AXI4-Stream:(For high-speed streaming data.)面向高速流數(shù)據(jù)傳輸;去掉了地址項(xiàng),允許無限制的數(shù)據(jù)突發(fā)傳輸規(guī)模。

首先說AXI4總線和AXI4-Lite總線具有相同的組成部分:

(1)讀地址通道,包含ARVALID, ARADDR, ARREADY信號(hào);

(2)讀數(shù)據(jù)通道,包含RVALID, RDATA, RREADY, RRESP信號(hào);

(3)寫地址通道,包含AWVALID,AWADDR, AWREADY信號(hào);

(4)寫數(shù)據(jù)通道,包含WVALID, WDATA,WSTRB, WREADY信號(hào);

(5)寫應(yīng)答通道,包含BVALID, BRESP, BREADY信號(hào);

(6)系統(tǒng)通道,包含:ACLK,ARESETN信號(hào)。

AXI4總線和AXI4-Lite總線的信號(hào)也有他的命名特點(diǎn):

讀地址信號(hào)都是以AR開頭(A:address;R:read)

寫地址信號(hào)都是以AW開頭(A:address;W:write)

讀數(shù)據(jù)信號(hào)都是以R開頭(R:read)

寫數(shù)據(jù)信號(hào)都是以W開頭(W:write)

應(yīng)答型號(hào)都是以B開頭(B:back(answer back))

了解到總線的組成部分以及命名特點(diǎn),那么在后續(xù)的實(shí)驗(yàn)中您將逐漸看到他們的身影。每個(gè)信號(hào)的作用暫停不表,放在后面一一介紹。

而AXI4-Stream總線的組成有:

(1)ACLK信號(hào):總線時(shí)鐘,上升沿有效;

(2)ARESETN信號(hào):總線復(fù)位,低電平有效

(3)TREADY信號(hào):從機(jī)告訴主機(jī)做好傳輸準(zhǔn)備;

(4)TDATA信號(hào):數(shù)據(jù),可選寬度32,64,128,256bit

(5)TSTRB信號(hào):每一bit對(duì)應(yīng)TDATA的一個(gè)有效字節(jié),寬度為TDATA/8

(6)TLAST信號(hào):主機(jī)告訴從機(jī)該次傳輸為突發(fā)傳輸?shù)慕Y(jié)尾;

(7)TVALID信號(hào):主機(jī)告訴從機(jī)數(shù)據(jù)本次傳輸有效;

(8)TUSER信號(hào) :用戶定義信號(hào),寬度為128bit。

對(duì)于AXI4-Stream總線命名而言,除了總線時(shí)鐘和總線復(fù)位,其他的信號(hào)線都是以T字母開頭,后面跟上一個(gè)有意義的單詞,看清這一點(diǎn)后,能幫助讀者記憶每個(gè)信號(hào)線的意義。如TVALID = T+單詞Valid(有效),那么讀者就應(yīng)該立刻反應(yīng)該信號(hào)的作用。每個(gè)信號(hào)的具體作用,在后面分析源碼時(shí)再做分析

12.3.2AXI接口介紹

三種AXI接口分別是:

AXI-GP接口(4個(gè)):是通用的AXI接口,包括兩個(gè)32位主設(shè)備接口和兩個(gè)32位從設(shè)備接口,用過改接口可以訪問PS中的片內(nèi)外設(shè)。

AXI-HP接口(4個(gè)):是高性能/帶寬的標(biāo)準(zhǔn)的接口,PL模塊作為主設(shè)備連接(從下圖中箭頭可以看出)。主要用于PL訪問PS上的存儲(chǔ)器(DDR和On-Chip RAM)

AXI-ACP接口(1個(gè)):是ARM多核架構(gòu)下定義的一種接口,中文翻譯為加速器一致性端口,用來管理DMA之類的不帶緩存的AXI外設(shè),PS端是Slave接口。

我們可以雙擊查看ZYNQ的IP核的內(nèi)部配置,就能發(fā)現(xiàn)上述的三種接口,圖中已用紅色方框標(biāo)記出來,我們可以清楚的看出接口連接與總線的走向:

12.3.3AXI協(xié)議概述

講到協(xié)議不可能說是撇開總線單講協(xié)議,因?yàn)閰f(xié)議的制定也是要建立在總線構(gòu)成之上的。雖然說AXI4,AXI4-Lite,AXI4-Stream都是AXI4協(xié)議,但是各自細(xì)節(jié)上還是不同的。

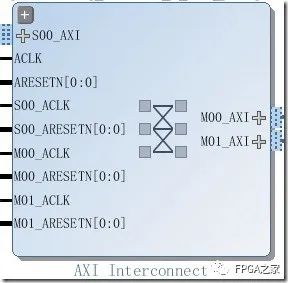

總的來說,AXI總線協(xié)議的兩端可以分為分為主(master)、從(slave)兩端,他們之間一般需要通過一個(gè)AXI Interconnect相連接,作用是提供將一個(gè)或多個(gè)AXI主設(shè)備連接到一個(gè)或多個(gè)AXI從設(shè)備的一種交換機(jī)制。當(dāng)我們添加了zynq以及帶AXI的IP后再進(jìn)行自動(dòng)連線時(shí)vivado會(huì)自動(dòng)幫我們添加上這個(gè)IP,大家應(yīng)該是不陌生了。

AXI Interconnect的主要作用是,當(dāng)存在多個(gè)主機(jī)以及從機(jī)器時(shí),AXI Interconnect負(fù)責(zé)將它們聯(lián)系并管理起來。由于AXI支持亂序發(fā)送,亂序發(fā)送需要主機(jī)的ID信號(hào)支撐,而不同的主機(jī)發(fā)送的ID可能相同,而AXI Interconnect解決了這一問題,他會(huì)對(duì)不同主機(jī)的ID信號(hào)進(jìn)行處理讓ID變得唯一。

AXI協(xié)議將讀地址通道,讀數(shù)據(jù)通道,寫地址通道,寫數(shù)據(jù)通道,寫響應(yīng)通道分開,各自通道都有自己的握手協(xié)議。每個(gè)通道互不干擾卻又彼此依賴。這也是AXI高效的原因之一。

12.3.4AXI協(xié)議之握手協(xié)議

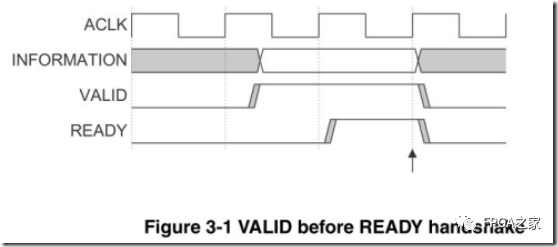

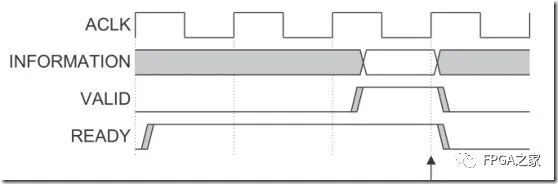

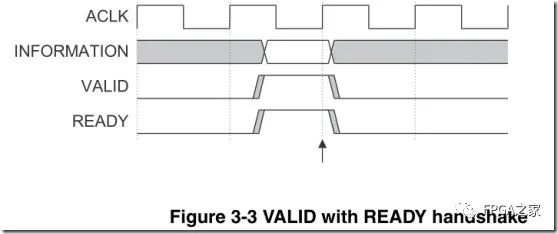

AXI4所采用的是一種READY,VALID握手通信機(jī)制,簡(jiǎn)單來說主從雙方進(jìn)行數(shù)據(jù)通信前,有一個(gè)握手的過程。傳輸源產(chǎn)生VLAID信號(hào)來指明何時(shí)數(shù)據(jù)或控制信息有效。而目地源產(chǎn)生READY信號(hào)來指明已經(jīng)準(zhǔn)備好接受數(shù)據(jù)或控制信息。傳輸發(fā)生在VALID和READY信號(hào)同時(shí)為高的時(shí)候。VALID和READY信號(hào)的出現(xiàn)有三種關(guān)系。

(1) VALID先變高READY后變高。時(shí)序圖如下:

在箭頭處信息傳輸發(fā)生。

(2) READY先變高VALID后變高。時(shí)序圖如下:

同樣在箭頭處信息傳輸發(fā)生。

(3) VALID和READY信號(hào)同時(shí)變高。時(shí)序圖如下:

在這種情況下,信息傳輸立馬發(fā)生,如圖箭頭處指明信息傳輸發(fā)生。

需要強(qiáng)調(diào)的是,AXI的五個(gè)通道,每個(gè)通道都有握手機(jī)制,接下來我們就來分析一下AXI-Lite的源碼來更深入的了解AXI機(jī)制。

12.3.5突發(fā)式讀寫

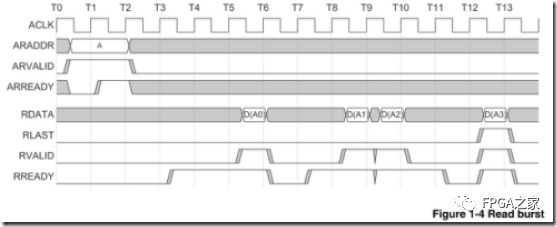

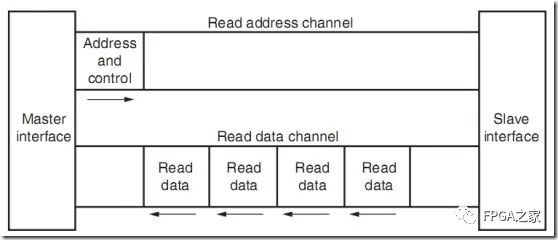

1、突發(fā)式讀的時(shí)序圖如下:

當(dāng)?shù)刂烦霈F(xiàn)在地址總線后,傳輸?shù)臄?shù)據(jù)將出現(xiàn)在讀數(shù)據(jù)通道上。設(shè)備保持VALID為低直到讀數(shù)據(jù)有效。為了表明一次突發(fā)式讀寫的完成,設(shè)備用RLAST信號(hào)來表示最后一個(gè)被傳輸?shù)臄?shù)據(jù)。

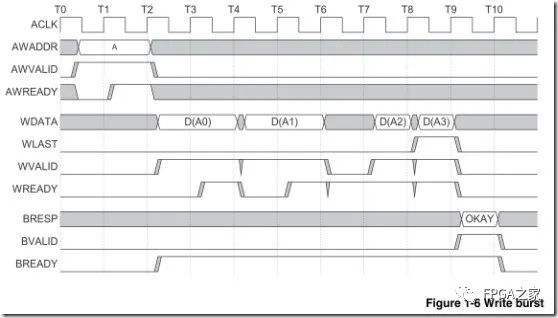

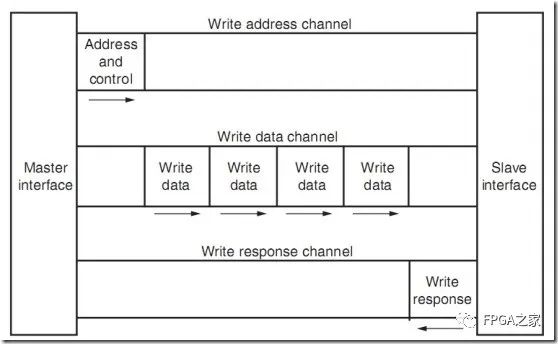

2、 突發(fā)式寫時(shí)序圖如下:

這一過程的開始時(shí),主機(jī)發(fā)送地址和控制信息到寫地址通道中,然后主機(jī)發(fā)送每一個(gè)寫數(shù)據(jù)到寫數(shù)據(jù)通道中。當(dāng)主機(jī)發(fā)送最后一個(gè)數(shù)據(jù)時(shí),WLAST信號(hào)就變?yōu)楦摺.?dāng)設(shè)備接收完所有數(shù)據(jù)之后他將一個(gè)寫響應(yīng)發(fā)送回主機(jī)來表明寫事務(wù)完成。

12.4AXI4-Lite詳解

12.4.1AXI4-Lite源碼查看

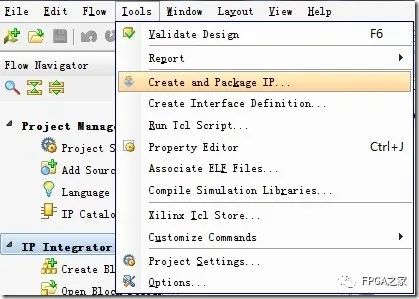

Step1:要看到AXI-Lite的源碼,我們先要自定義一個(gè)AXI-Lite的IP,新建工程之后,選擇,菜單欄->Tools->Creat and Package IP:

Step2:選擇Next

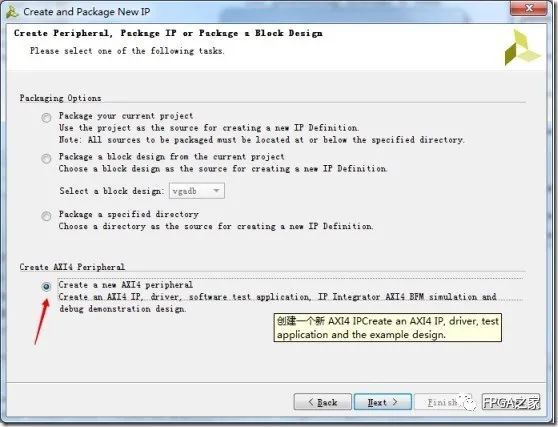

Step3:選擇Create AXI4 Peripheral,然后Next:

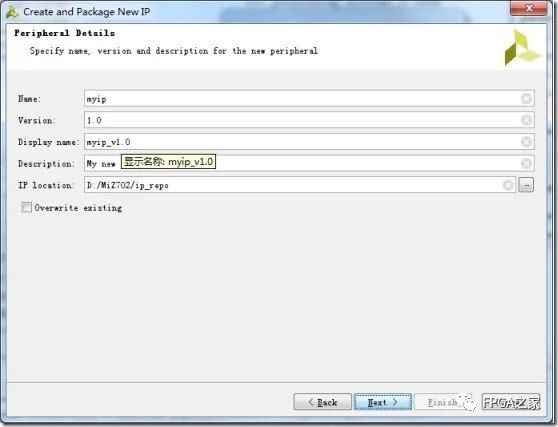

Step4:默認(rèn),選擇Next

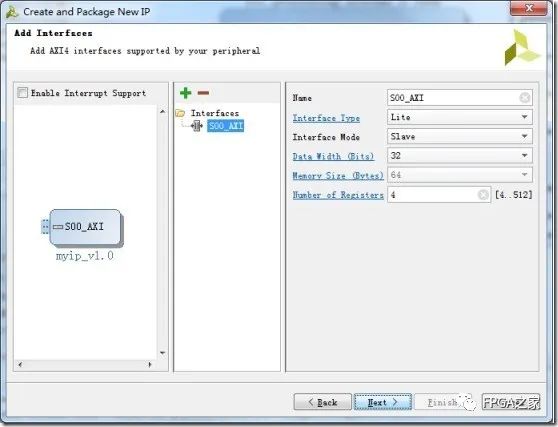

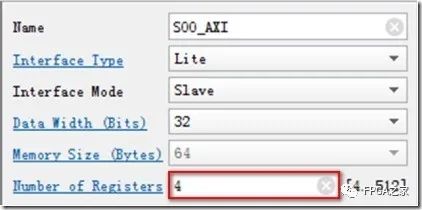

Step5:注意這里接口類型選擇Lite,選擇Next:

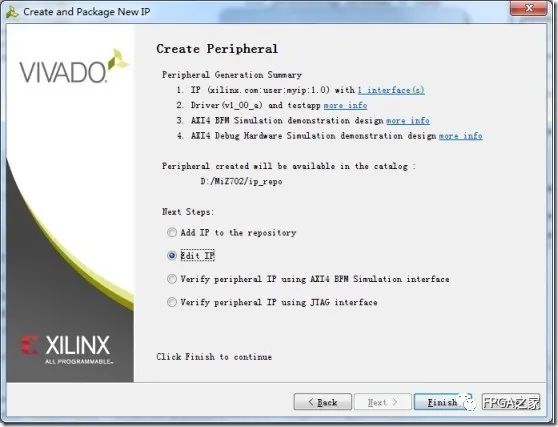

Step6:選擇Edit IP,點(diǎn)擊Finish:

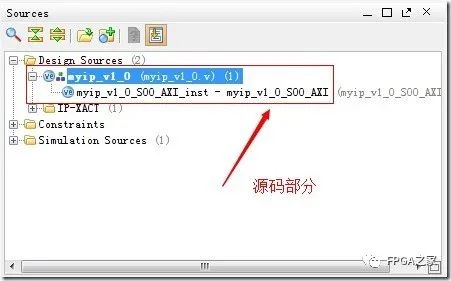

Step7:此后,Vivado會(huì)新建一個(gè)工程,專門編輯該IP,通過該工程,我們就可以看到Vivado為我們生成的AXI-Lite的操作源碼:

12.4.2 AXI-Lite 源碼分析

當(dāng)打開頂層文件的時(shí),映入眼簾的是一堆AXI的信號(hào),這些信號(hào)是否似曾相識(shí)?

|

input wire s00_axi_aclk, input wire s00_axi_aresetn, input wire [C_S00_AXI_ADDR_WIDTH-1 : 0] s00_axi_awaddr, input wire [2 : 0] s00_axi_awprot, input wire s00_axi_awvalid, output wire s00_axi_awready, input wire [C_S00_AXI_DATA_WIDTH-1 : 0] s00_axi_wdata, input wire [(C_S00_AXI_DATA_WIDTH/8)-1 : 0] s00_axi_wstrb, input wire s00_axi_wvalid, output wire s00_axi_wready, output wire [1 : 0] s00_axi_bresp, output wire s00_axi_bvalid, input wire s00_axi_bready, input wire [C_S00_AXI_ADDR_WIDTH-1 : 0] s00_axi_araddr, input wire [2 : 0] s00_axi_arprot, input wire s00_axi_arvalid, output wire s00_axi_arready, output wire [C_S00_AXI_DATA_WIDTH-1 : 0] s00_axi_rdata, output wire [1 : 0] s00_axi_rresp, output wire s00_axi_rvalid, input wire s00_axi_rready |

沒錯(cuò)筆者曾在《AXI總線概述》這節(jié)中提到了他們,這次通過源碼分析再次隆重介紹它們。

|

讀 通 道 |

地址通道 | 數(shù)據(jù)通道 | |||

| ARVALID | 讀地址有效。此信號(hào)表明該信道此時(shí)能有效讀出地址和控制信息 | RVALID | 讀數(shù)據(jù)有效。此信號(hào)表明該信道此時(shí)能有效讀出數(shù)據(jù) | ||

| ARADDR | 讀地址 | RDATA | 讀數(shù)據(jù) | ||

| ARREADY | 讀地址準(zhǔn)備好了。該信號(hào)指示從器件準(zhǔn)備好接受一個(gè)地址和相關(guān)聯(lián)的控制信號(hào) | RREADY | 讀數(shù)據(jù)準(zhǔn)備好了。該信號(hào)指示從器件準(zhǔn)備好接收數(shù)據(jù) | ||

| ARPROT | 保護(hù)類型。這個(gè)信號(hào)表示該事務(wù)的特權(quán)和安全級(jí)別,并確定是否該事務(wù)是一個(gè)數(shù)據(jù)存取或指令的訪問 | RRESP | 讀取響應(yīng)。這個(gè)信號(hào)表明讀事務(wù)處理的狀態(tài)。 | ||

|

寫 通 道 |

地址通道 | 數(shù)據(jù)通道 | 應(yīng)答通道 | ||

| AWVALID | 寫地址有效。這個(gè)信號(hào)表示該主信令有效的寫地址和控制信息。 | WVALID | 寫有效。這個(gè)信號(hào)表示有效的寫數(shù)據(jù)和選通信號(hào)都可用。 | BVALID | 寫響應(yīng)有效。此信號(hào)表明寫命令的有效寫入響應(yīng)。 |

| AWADDR | 寫地址 | WDATA | 寫數(shù)據(jù) | BREADY | 響應(yīng)準(zhǔn)備。該信號(hào)指示在主主機(jī)可以接受一個(gè)響應(yīng)信號(hào) |

| AWREADY | 寫地址準(zhǔn)備好了。該信號(hào)指示從器件準(zhǔn)備好接受一個(gè)地址和相關(guān)聯(lián)的控制信號(hào) | WSTRB | 寫選通。這個(gè)信號(hào)表明該字節(jié)通道持有效數(shù)據(jù)。每一bit對(duì)應(yīng)WDATA一個(gè)字節(jié) | BRESP | 寫響應(yīng)。這個(gè)信號(hào)表示寫事務(wù)處理的狀態(tài)。 |

| AWPROT | 寫通道保護(hù)類型。這個(gè)信號(hào)表示該事務(wù)的特權(quán)和安全級(jí)別,并確定是否該事務(wù)是一個(gè)數(shù)據(jù)存取或指令的訪問 | WREADY | 寫準(zhǔn)備好了。該信號(hào)指示從器件可以接受寫數(shù)據(jù)。 |

Vivado為我們生成的AXI-Lite的操作源碼,是一個(gè)例子,我只需要讀懂他,然后稍加修改,就可以為我們所用。

我們先來看一段WDATA相關(guān)的代碼:

|

always @( posedge S_AXI_ACLK ) begin if ( S_AXI_ARESETN == 1'b0 ) begin slv_reg0 <= 0; slv_reg1 <= 0; slv_reg2 <= 0; slv_reg3 <= 0; end else begin if (slv_reg_wren) begin case ( axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] ) 2'h0: for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 ) if ( S_AXI_WSTRB[byte_index] == 1 ) begin // Respective byte enables are asserted as per write strobes // Slave register 0 slv_reg0[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8]; end 2'h1: for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 ) if ( S_AXI_WSTRB[byte_index] == 1 ) begin // Respective byte enables are asserted as per write strobes // Slave register 1 slv_reg1[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8]; end 2'h2: for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 ) if ( S_AXI_WSTRB[byte_index] == 1 ) begin // Respective byte enables are asserted as per write strobes // Slave register 2 slv_reg2[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8]; end 2'h3: for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 ) if ( S_AXI_WSTRB[byte_index] == 1 ) begin // Respective byte enables are asserted as per write strobes // Slave register 3 slv_reg3[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8]; end default : begin slv_reg0 <= slv_reg0; slv_reg1 <= slv_reg1; slv_reg2 <= slv_reg2; slv_reg3 <= slv_reg3; end endcase end end end |

這段程序的作用是,當(dāng)PS那邊向AXI4-Lite總線寫數(shù)據(jù)時(shí),PS這邊負(fù)責(zé)將數(shù)據(jù)接收到寄存器slv_reg。而slv_reg寄存器有0~3共4個(gè)。至于賦值給哪一個(gè)由

axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB]決定,根據(jù)宏定義其實(shí)就是由axi_awaddr[3:2] (寫地址中不僅包含地址,而且包含了控制位,這里的[3:2]就是控制位)決定賦值給哪個(gè)slv_reg。

PS調(diào)用寫函數(shù)時(shí),如果不做地址偏移的話,axi_awaddr[3:2]的值默認(rèn)是為0的,舉個(gè)例子,如果我們自定義的IP的地址被映射為0x43C00000,那么我們Xil_Out32(0x43C00000,Value)寫的就是slv_reg0的值。如果地址偏移4位,如

Xil_Out32(0x43C00000 + 4,Value) 寫的就是slv_reg1的值,依次類推。

分析時(shí)只關(guān)注slv_reg0(其他結(jié)構(gòu)上也是一模一樣的):

|

for ( byte_index = 0; byte_index <= (C_S_AXI_DATA_WIDTH/8)-1; byte_index = byte_index+1 ) if ( S_AXI_WSTRB[byte_index] == 1 ) begin slv_reg0[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8]; end |

其中,C_S_AXI_DATA_WIDTH的宏定義的值為32,也就是數(shù)據(jù)位寬,S_AXI_WSTRB就是寫選通信號(hào),S_AXI_WDATA就是寫數(shù)據(jù)信號(hào)。

存在于for循環(huán)中的最關(guān)鍵的一句:

slv_reg0[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

當(dāng)byte_index = 0的時(shí)候這句話就等價(jià)于:

slv_reg0[7:0] <= S_AXI_WDATA[7:0];

當(dāng)byte_index = 1的時(shí)候這句話就等價(jià)于:

slv_reg0[15:8] <= S_AXI_WDATA[15:8];

當(dāng)byte_index = 2的時(shí)候這句話就等價(jià)于:

slv_reg0[23:16] <= S_AXI_WDATA[23:16];

當(dāng)byte_index = 3的時(shí)候這句話就等價(jià)于:

slv_reg0[31:24] <= S_AXI_WDATA[31:24];

也就是說,只有當(dāng)寫選通信號(hào)為1時(shí),它所對(duì)應(yīng)S_AXI_WDATA的字節(jié)才會(huì)被讀取。

讀懂了這段話之后,我們就知道了,如果我們想得到PS寫到總線上的數(shù)據(jù),我們只需要讀取slv_reg0的值即可。

那如果,我們想寫數(shù)據(jù)到總線讓PS讀取該數(shù)據(jù),我們?cè)撛趺醋瞿兀课覀兝^續(xù)來看有關(guān)RADTA讀數(shù)據(jù)代碼:

|

// Output register or memory read data always @( posedge S_AXI_ACLK ) begin if ( S_AXI_ARESETN == 1'b0 ) begin axi_rdata <= 0; end else begin // When there is a valid read address (S_AXI_ARVALID) with // acceptance of read address by the slave (axi_arready), // output the read dada if (slv_reg_rden) begin axi_rdata <= reg_data_out;???? // register read data end end end |

觀察可知,當(dāng)PS讀取數(shù)據(jù)時(shí),程序會(huì)把reg_data_out復(fù)制給axi_rdata(RADTA讀數(shù)據(jù))。我們繼續(xù)追蹤reg_data_out:

|

always @(*) begin // Address decoding for reading registers case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] ) 2'h0 : reg_data_out <= slv_reg0; 2'h1 : reg_data_out <= slv_reg1; 2'h2 : reg_data_out <= slv_reg2; 2'h3 : reg_data_out <= slv_reg3; default : reg_data_out <= 0; endcase end |

和前面分析的一樣此時(shí)通過判斷axi_awaddr[3:2]的值來判斷將那個(gè)值給reg_data_out上,同樣當(dāng)PS調(diào)用讀取函數(shù)時(shí),這里axi_awaddr[3:2]默認(rèn)是0,所以我們只需要把slv_reg0替換成我們自己數(shù)據(jù),就可以讓PS通過總線讀到我們提供的數(shù)據(jù)。

這里可能有的讀者會(huì)問了,slv_reg0不是總線寫過來的數(shù)據(jù)嗎?因?yàn)楣P者說過這個(gè)程序是Vivado為我們提供的例子,它這么做無非是想驗(yàn)證我寫出去的值和我讀進(jìn)入的值相等。但是他怎么寫確實(shí)會(huì)對(duì)初看代碼的人造成困擾。

最后筆者提出一個(gè)問題,為什么寫通道要比讀通道多了一列應(yīng)答通道,這是為什么呢?

首先,你要知道這個(gè)應(yīng)答信號(hào)是干什么用的?

寫應(yīng)答,主要是回復(fù)主機(jī)你這個(gè)寫過程是沒有問題的,那讀為什么不需要這個(gè)過程呢?

這時(shí)因?yàn)橹鳈C(jī)在讀取數(shù)據(jù)時(shí),從機(jī)可以直接通過讀數(shù)據(jù)通道給主機(jī)反饋信息,因此就沒有必要再來開辟一個(gè)單獨(dú)的應(yīng)答通道了。

小結(jié):

如果我們想讀AXI4_Lite總線上的數(shù)據(jù)時(shí),只需關(guān)注slv_reg的數(shù)據(jù),我們可自行添加一段代碼,如:

|

reg [11:0]rlcd_rgb; always @( posedge S_AXI_ACLK ) begin if ( S_AXI_ARESETN == 1'b0 ) begin rlcd_rgb <= 12'd0; end else begin rlcd_rgb <= slv_reg0[11:0]; end end assign lcd_rgb = rlcd_rgb; |

如果我們想對(duì)AXI4_Lite信號(hào)寫數(shù)據(jù)時(shí),我們只需修改對(duì)reg_data_out的賦值,如:

|

//寫總線測(cè)試修改!!!!!!!!! wire[31:0]wlcd_xy;// = {10'd0,lcd_xy}; assign wlcd_xy = {10'd0,lcd_xy}; assign slv_reg_rden = axi_arready & S_AXI_ARVALID & ~axi_rvalid; always @(*) begin // Address decoding for reading registers case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] ) 2'h0 : reg_data_out <= wlcd_xy;//slv_reg0;??? 2'h1 : reg_data_out <= slv_reg1; 2'h2 : reg_data_out <= slv_reg2; 2'h3 : reg_data_out <= slv_reg3; default : reg_data_out <= 0; endcase end |

最后強(qiáng)調(diào)下如果我們自定義的IP的地址被映射為0x43C00000,那么我們Xil_Out32(0x43C00000,Value)寫的就是slv_reg0的值。如果地址偏移4位,如

Xil_Out32(0x43C00000 + 4,Value) 寫的就是slv_reg1的值,依次類推。

目前這里只有4個(gè)寄存器,那是因?yàn)橹斑x擇的是4個(gè),其實(shí)我們可以定義的更多:

在ps的頭文件里可以看到我們自定義的IP的地址是有個(gè)范圍的

#defineXPAR_MYIPFREQUENCY_0_S00_AXI_BASEADDR 0x43C00000

#defineXPAR_MYIPFREQUENCY_0_S00_AXI_HIGHADDR 0x43C0FFFF

理論上只要基地址 + 偏移量不要超過HIGHADDR即可。

12.5 觀察AXI4-Lite總線信號(hào)

在第十章,我們封裝了一個(gè)AXI_Lite的GPIO,通過本章的分析,我們?cè)诘谑鹿こ痰幕A(chǔ)上通過添加一個(gè)ila核的方式,來具體看看AXI_Lite總線的信號(hào)。

Step1:做好第十章工程的備份,然后直接打開第十章的工程。

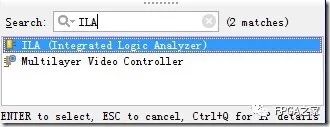

Step2:?jiǎn)螕鬒P icon  ?添加 ila CORE

?添加 ila CORE

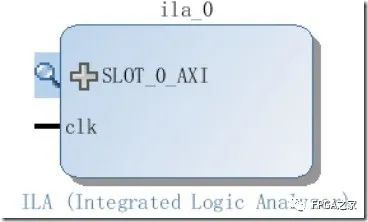

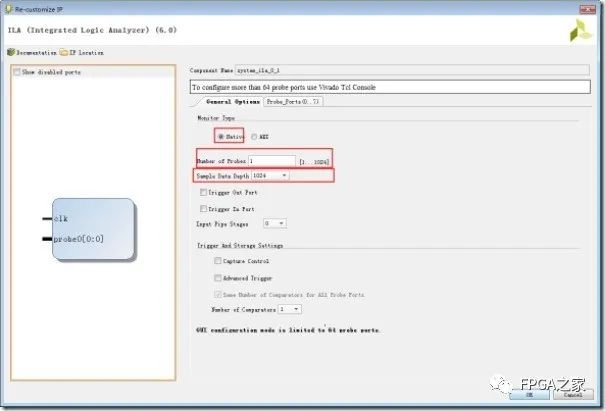

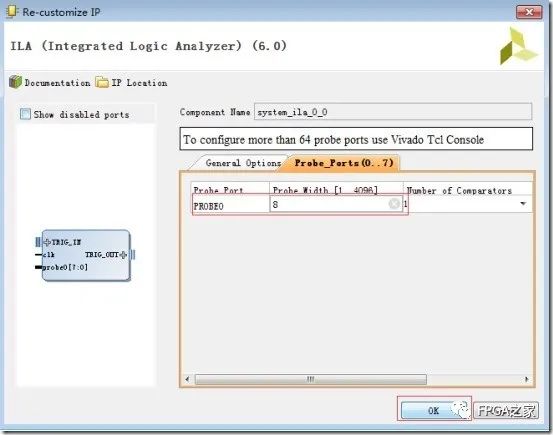

Step3:雙擊打開ILA CORE

Step4:雙擊打開ILA CORE

General Options設(shè)置如下

Probe_Ports設(shè)置如下,之后單擊OK

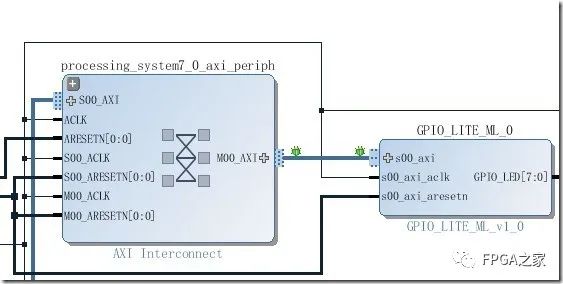

Step5:連接Probe0到GPIO_LED。

Step6:連接CLK接口到FCLK_CLK0接口

Step7:選中Processing_System7_0_axi_periph和GPIO_LITE_ML_0之間的S_AXI總線。

Step8:右擊選擇Mark Debug

Step9:接下來依然是,右鍵單擊Block文件,文件選擇Generate the Output Products。

Step10:繼續(xù)右鍵單擊Block文件,選擇Create a HDL wrapper,根據(jù)Block文件內(nèi)容產(chǎn)生一個(gè)HDL 的頂層文件,并選擇讓vivado自動(dòng)完成。

Setp11:單擊Run Synthesis,如果有 Save 對(duì)話框彈出選擇保存。

Setp12:綜合結(jié)束后選擇Synthesized Design option單擊 OK。

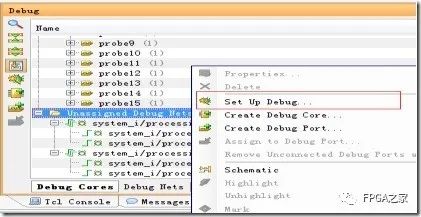

Step13:在如下對(duì)話框中找到Unassigned debug nets(如果對(duì)話框沒有出現(xiàn)選擇 菜單->Window > Debug)

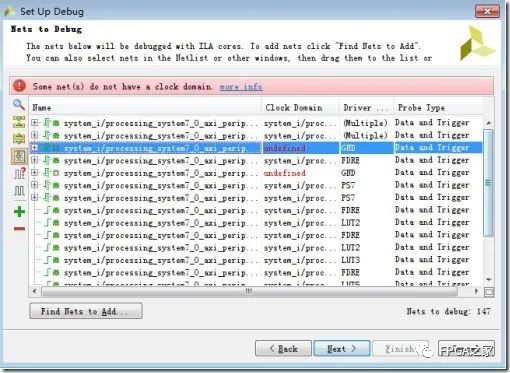

Step14:右擊 Unassigned Debug Nets 選擇Set up Debug… 之后單擊 Next

Step15:刪除紅色錯(cuò)誤的信號(hào)然后單擊Next 到結(jié)束

Step16:生成Bit文件。

12.6 加載到SDK

Step1:導(dǎo)出硬件。

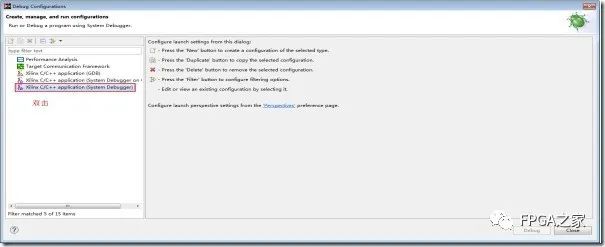

Step2:右擊工程,選擇Debug as ->Debug configuration。

Step3:選中system Debugger,雙擊創(chuàng)建一個(gè)系統(tǒng)調(diào)試。

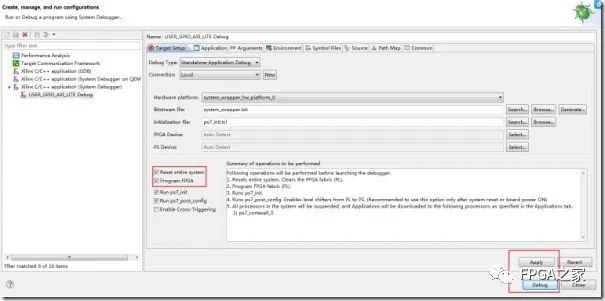

Step4:設(shè)置系統(tǒng)調(diào)試。

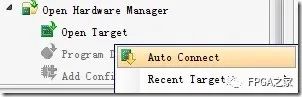

Step5:回到VIVADO單擊Open Target->Auto Connect

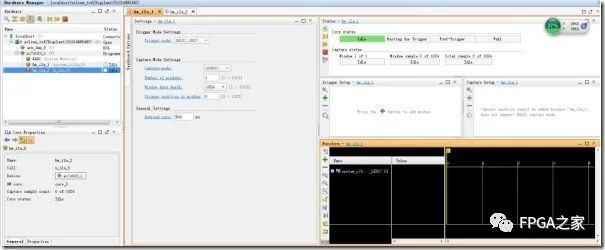

Step6:加載完成后的界面

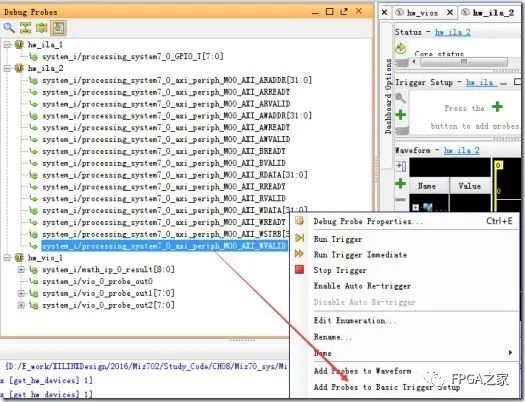

Step7:選擇菜單->window->Debugprobes 選擇AXI_WVALID和AXI_AWVALID做為觸發(fā)信號(hào)

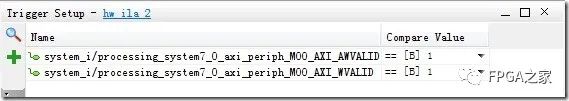

Step8:設(shè)置觸發(fā)條件為1

Step9:設(shè)置觸發(fā)位置為512

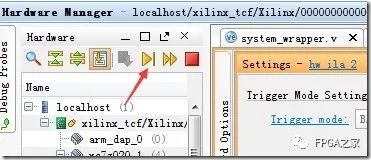

Step10:單擊箭頭所指向啟動(dòng)觸發(fā)

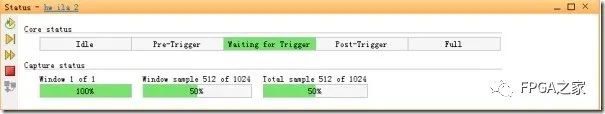

Step11:進(jìn)入等待觸發(fā)狀態(tài)

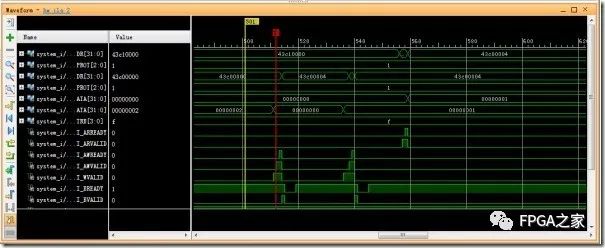

Step12:?jiǎn)螕暨\(yùn)行 后VIVADO ?HW_ILA2 窗口采集到波形輸出,可以看到AXI總線的工作時(shí)序。

后VIVADO ?HW_ILA2 窗口采集到波形輸出,可以看到AXI總線的工作時(shí)序。

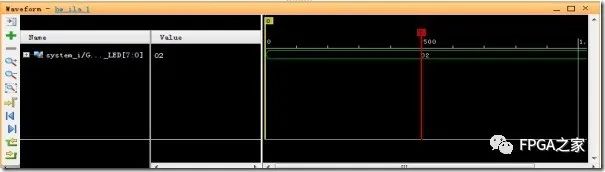

Step13:HW_ILA1 窗口采集到的數(shù)據(jù)是GPIO_LED的值為0x02,同時(shí)可觀察到開發(fā)板上的LED2亮起。

12.7 本章小結(jié)

通過本章的學(xué)習(xí),我們首先得認(rèn)識(shí)到總線和接口以及協(xié)議的區(qū)別,其次通過分析AXI4-Lite,AXI4-Stream,AXI4總線的從機(jī)代碼,對(duì)AXI協(xié)議有一定的認(rèn)識(shí),那么在后面學(xué)習(xí)AXI的一些IP時(shí)就不會(huì)有恐懼的心理。

最后,我們?cè)倮硪焕鞟XI總線和AXI接口的關(guān)系。在ZYNQ中,支持AXI4-Lite,AXI4和AXI4-Stream三種總線協(xié)議,這前面已經(jīng)說過了,要注意的是PS與PL之間的接口(AXI-GP接口,AXI-HP接口以及AXI-ACP接口)卻只支持AXI-Lite和AXI協(xié)議這兩種總線協(xié)議。

也就是說PL這邊的AXI-Stream的接口是不能直接與PS對(duì)接的,需要經(jīng)過AXI4或者AXI4-Lite的轉(zhuǎn)換。比如后面將用到的VDMA IP ,它就實(shí)現(xiàn)了在PL內(nèi)部AXI4到AXI-Stream的轉(zhuǎn)換,VDMA利用的接口就是AXI-HP接口。

??

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1662文章

22450瀏覽量

637665 -

ARM

+關(guān)注

關(guān)注

135文章

9573瀏覽量

392736 -

DDR

+關(guān)注

關(guān)注

11文章

759瀏覽量

69341 -

AXI總線

+關(guān)注

關(guān)注

0文章

68瀏覽量

14772 -

Zynq

+關(guān)注

關(guān)注

10文章

631瀏覽量

49508

原文標(biāo)題:S02_CH12_ AXI_Lite 總線詳解

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

同步電機(jī)的轉(zhuǎn)數(shù)同步究竟是與什么同步啊?

SVPWM調(diào)制波的數(shù)學(xué)表達(dá)究竟是怎樣的呢?

ARM和FPGA究竟是如何進(jìn)行通信的呢?

ARM和FPGA究竟是如何進(jìn)行通信的呢?

評(píng)論