本文介紹了FPGA在實現(xiàn)高清低碼流視頻編碼中的作用以及如何具體實現(xiàn)。目前現(xiàn)狀是高清視頻720p的碼流一般在2Mbps以上,1080p的碼流在4Mbps以上,要大幅度降低碼流,需要從幾個方面考慮。

2013-09-23 13:41:15 2588

2588 ,是近年信道編碼領(lǐng)域的研究熱點,目前已廣泛應(yīng)用于深空通信、光纖通信、衛(wèi)星數(shù)字視頻和音頻廣播等領(lǐng)域。LDPC碼已成為第四代通信系統(tǒng)(4G)強(qiáng)有力的競爭者,而基于LDPC碼的編碼方案已經(jīng)被下一代衛(wèi)星數(shù)字視頻廣播標(biāo)準(zhǔn)DVB-S2采納。

2020-03-03 10:30:27 2309

2309

的靈活性和較低的差錯誤碼特性,可實現(xiàn)并行操作,譯碼復(fù)雜度低,適合硬件實現(xiàn),吞吐量大,極具高速譯碼的潛力,在碼長較長的情況下,仍然可以有效譯碼。 目前常用的信道編碼體制有BCH碼、RS碼、卷積碼、Turbo碼和LDPC碼等。其中BCH碼和RS碼都屬于線性分組碼的范疇

2020-11-02 13:56:16 51171

51171

800Mbps準(zhǔn)循環(huán)LDPC碼編碼器的FPGA實現(xiàn)引言低密度校驗碼腸 ,碼 由于其接近香農(nóng)限的糾錯性能,使得其成為當(dāng)前信道編碼的研究熱點。 碼面臨的一個關(guān)鍵問題是其較高的編碼復(fù)雜度和編碼時延。 形耐

2012-08-11 11:44:45

,用FPGA實現(xiàn)VGA接口協(xié)議可在顯示器上顯示文字、圖型等;★PS/2鼠標(biāo),鍵盤接口:標(biāo)準(zhǔn)鼠標(biāo),鍵盤接口,提供的例程用VHDL實現(xiàn)在數(shù)碼管上同時顯示鍵盤掃描碼和ASCII碼,也可結(jié)合SOPC編程使其顯示

2009-10-23 15:15:24

:配備:★RS-232串口:用于與計算機(jī)的數(shù)據(jù)通信;★VGA接口:直接VGA與顯示器對接,用FPGA實現(xiàn)VGA接口協(xié)議可在顯示器上顯示文字、圖型等;★PS/2鼠標(biāo),鍵盤接口:標(biāo)準(zhǔn)鼠標(biāo),鍵盤接口,提供

2009-11-02 18:55:54

EP2S60F484I4N特價 EP2S60F484I4N貨期EP2S60F484I4N 價格EP2S60F484I4N國宇航芯特價訂貨EP2S60F484C4N國宇航芯特價訂貨

2020-01-06 09:07:44

論壇里面的大神們,有沒有已經(jīng)完成LDPC碼編譯碼算法的FPGA實現(xiàn),本人目前在做這方面的項目,時間比較緊,緊急求購IP核。。

2012-04-16 23:43:28

LDPC碼入門資料!

2013-09-21 13:20:43

請教各位大仙,sof和jic文件燒錄均正常,pof燒錄失敗,sof燒錄后可正常工作,但jic燒錄后無法正常工作,好像沒有任何數(shù)據(jù)輸出,這是為什么啊?fpga為EP2S60,配置芯片為epcs64,配置芯片也更換了,問題依舊。

2017-10-14 15:43:00

.基于該結(jié)構(gòu),本文實現(xiàn)了符合中國數(shù)字電視地面?zhèn)鬏敇?biāo)準(zhǔn)DTMB中LDPC譯碼器,在SMIC0.18um標(biāo)準(zhǔn)COMS工藝下,芯片面積約為8mm2;在時鐘頻率50MHz,迭代次數(shù)15次,8比特量化的條件下,吞吐率

2010-04-24 09:26:56

型。在高次脈沖編碼調(diào)制終端設(shè)備中廣泛使用CMI碼作為接口碼型,在速率低于8448kb/s的光纖數(shù)字傳輸系統(tǒng)中也被建議作為線路傳輸碼型。

2019-08-29 06:41:21

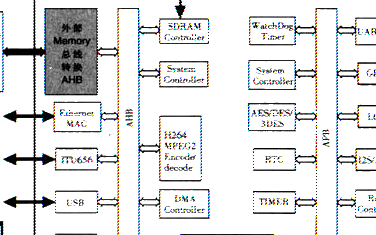

幀率提升、彩色空間轉(zhuǎn)換等處理。FPGA器件具有可重復(fù)編程的靈活性以及并行處理能力,并且隨著微處理器、專用硬件單元、DSP算法以及IP核的嵌入使其功能越來越強(qiáng)大。本系統(tǒng)的設(shè)計是基于Altera公司的EP2S60系列的開發(fā)板,板上集成兩片SDRAM存儲芯片、視頻輸入接口和VGA輸出接口。

2019-09-29 08:46:06

編碼器實現(xiàn)指標(biāo)分析LDPC碼編碼器實現(xiàn)編碼器方案驗證與優(yōu)缺點分析

2021-04-30 06:08:10

本設(shè)計方案采用了一種改進(jìn)的快速中值濾波算法,成功地在Altera公司的高性能Stratix II EP2S60上實現(xiàn)整個數(shù)字紅外圖像濾波,在保證實時性的同時,使得硬件體積大為縮減,大大降低了成本

2021-04-23 06:00:55

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于獲取雙通道數(shù)據(jù)采集,實現(xiàn)1路的Base CameraLink輸入,一路Base CameraLink

2012-06-13 11:39:49

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于獲取雙通道數(shù)據(jù)采集,實現(xiàn)1路的Base CameraLink輸入,一路Base CameraLink

2012-06-13 12:01:23

LDPC碼是近年來發(fā)展較快且日趨成熟的一種信道編碼方案,因其具有的優(yōu)越性能和實用價值而被人們認(rèn)知,但由于隨機(jī)結(jié)構(gòu)的LDPC碼編譯碼器硬件實現(xiàn)較為復(fù)雜,具有的準(zhǔn)循環(huán)特性QC_LDPC碼已成為IEEE802.11n(WiFi)、IEEE802.16e(WiMAX)、(DVB—S2)等眾多標(biāo)準(zhǔn)的信道編碼方案。

2019-09-30 07:19:45

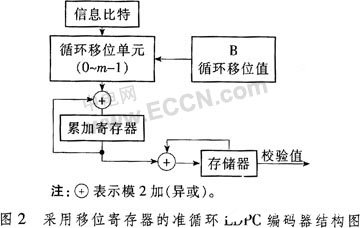

到了較多應(yīng)用。中國移動多媒體廣播(CMMB)中使用的就是LDPC糾錯編碼。在CMMB標(biāo)準(zhǔn)中,LDPC碼長為9216,可支持1/2和3/4兩種碼率。作者通過深入分析CMMB中LDPC碼校驗矩陣的特點,采用

2019-08-23 07:22:50

無線遙控器 常用的編碼方式有兩種類型,即固定碼與滾動碼兩種,滾動碼是固定碼的升級換代產(chǎn)品,目前凡有保密性要求的場合,都使用滾動編碼方式。下面簡單介紹無線遙控器采用滾動碼編碼方式的優(yōu)點: 1、保密型

2015-04-04 09:45:10

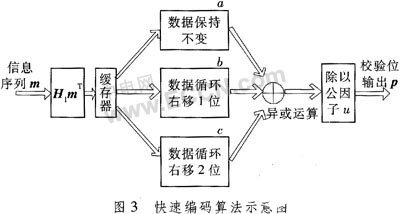

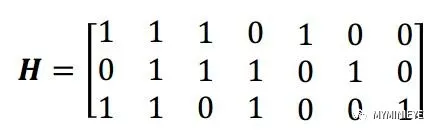

LDPC碼的通用編碼方法有哪些?準(zhǔn)循環(huán)LDPC碼的快速編碼方法是什么?

2021-04-25 07:16:26

Turbo碼編碼器的FPGA實現(xiàn)Turbo碼譯碼器的FPGA實現(xiàn)Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

本文在SvstemGenerator中對LDPC碼整個編譯碼系統(tǒng)進(jìn)行了參數(shù)化的硬件實現(xiàn),并構(gòu)建了超寬帶通信系統(tǒng)LDPC碼硬件仿真平臺,驗證了LDPC碼在UWB通信中的優(yōu)異性能。

2021-06-03 07:01:58

800Mbps準(zhǔn)循環(huán)LDPC碼編碼器的FPGA實現(xiàn)CCSDS星載圖像壓縮模塊的FPGA設(shè)計與實現(xiàn)FPGA和Nios_軟核的語音識別系統(tǒng)的研究RC4加密算法的FPGA設(shè)計與實現(xiàn)多FPGA系統(tǒng)中自定義

2012-02-02 17:26:14

最近想用音頻編碼解碼芯片實現(xiàn)快速傅里葉變換的功能,選了一款芯片AD1701用mini開發(fā)板。但是FFT功能能不能實現(xiàn)這個問題?現(xiàn)在一直沒有找到,也沒有看到更多的其它算法,有沒有大神給解答一下?

2018-12-20 09:19:48

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 針對LDPC碼與RS碼的串行級聯(lián)結(jié)構(gòu),提出了一種基于Chase的聯(lián)合迭代譯碼方法。軟入軟出的RS譯碼器與LDPC譯碼器之間經(jīng)過多次信息傳遞,性能可以逼近最大似然譯碼。模擬結(jié)果顯示:

2009-05-12 21:47:25 22

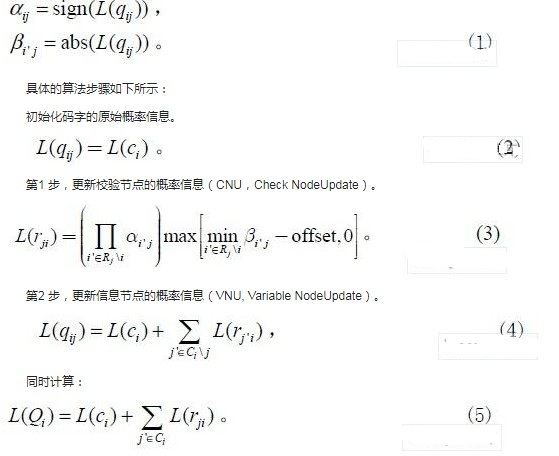

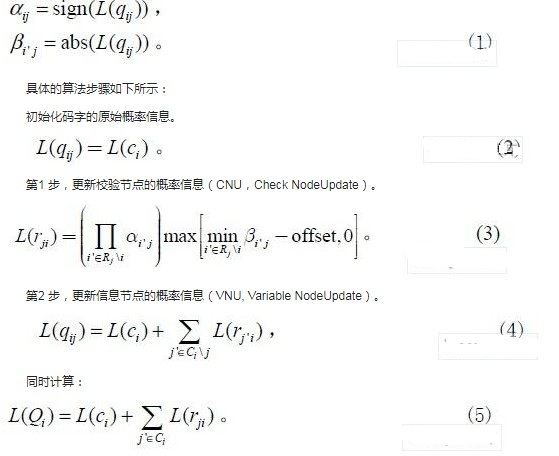

22 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架構(gòu),實現(xiàn)了碼率為1/2,幀長為1008bits的規(guī)則(3,6)LDPC碼譯碼器。所采用的最小-和算法相對于傳統(tǒng)的和-積算法在不損失譯碼性能的前提下,

2009-06-06 14:12:20 31

31 LDPC原理與應(yīng)用的主要內(nèi)容:

第一章 緒論第二章 信道編碼基礎(chǔ)第三章 LDPC碼概述第四章 LDPC碼譯碼第五章 結(jié)構(gòu)LDPC碼的編碼構(gòu)造第六章 各種編碼方法設(shè)計的LDPC碼

2009-07-24 15:07:06 0

0 An Introduction to LDPC Codeslow_power VLSI Decoder architectures for ldpc codesLow-Density

2009-07-24 15:45:40 0

0 VSPC-LDPC串行級聯(lián)碼的結(jié)構(gòu)與性能分析:提出了一種基于LDPC碼和縱向單奇偶校驗(VSPC)乘積碼的級聯(lián)編碼方法。該方法利用LDPC碼能否成功地譯碼的判定信息以取代常規(guī)乘積碼中的橫向校

2009-10-20 18:01:32 15

15 該文提出了一種可分解的碼率兼容LDPC 碼的構(gòu)造方法, 該方法構(gòu)造所得到的一個高碼率LDPC 碼的校驗矩陣中包含有若干低碼率LDPC 碼的校驗矩陣,而且一個高碼率的LDPC 碼又可以分解成

2009-11-19 16:47:41 14

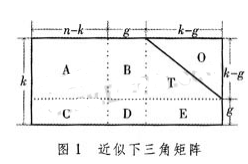

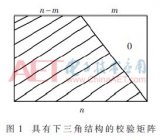

14 本文以CCSDS 推薦的7/8 碼率LDPC 碼為例,提出了一種適于高碼率LDPC 碼譯碼器的硬件結(jié)構(gòu)優(yōu)化方法。高碼率的LDPC 碼通常也伴隨著行重與列重的比例較高的問題。本方法是在拆分校驗矩

2009-11-25 15:21:25 26

26 該文從譯碼速率、硬件實現(xiàn)的復(fù)雜度和誤碼率3 個方面對比研究了兩種典型的高速譯碼算法:Turbo 型和積算法與并行加權(quán)比特翻轉(zhuǎn)算法。以準(zhǔn)循環(huán)LDPC 碼為對象,給出了Turbo 型和積算

2009-11-25 15:26:58 9

9 簡述了LDPC碼的研究現(xiàn)狀及編碼方法。在此基礎(chǔ)上分析了目前常用的編碼實現(xiàn)方式,并針對一類準(zhǔn)循環(huán)LDPC碼的特點,提出一種更簡潔的快速編碼算法及設(shè)計實現(xiàn)思路。

2009-12-02 16:25:14 22

22 規(guī)則LDPC碼的密度進(jìn)化方法及其高斯近似:密度進(jìn)化方法是分析現(xiàn)代高效糾錯編譯碼漸進(jìn)性能的新方法。在簡要闡述LDPC碼及其和積算法的基礎(chǔ)上,較系統(tǒng)的論述了密度進(jìn)化方法的基本

2010-01-12 18:55:09 18

18 本文提出了基于FPGA 正碼速調(diào)整的設(shè)計方案,采用格雷碼對地址編碼的異步FIFO設(shè)計,并利用MAXPLUSⅡ進(jìn)行編譯和仿真。結(jié)果表明,設(shè)計方法切實可行。

2010-01-13 15:16:07 25

25 該文用一種級聯(lián)碼模型描述了LDPC 編碼高階調(diào)制系統(tǒng)。該級聯(lián)碼模型以LDPC 碼為外碼,二-十進(jìn)制轉(zhuǎn)換碼為內(nèi)碼,再加一個刪余模塊構(gòu)成。基于這種級聯(lián)碼模型,該文給出了其聯(lián)合校驗

2010-02-08 16:06:44 11

11 Stratix II EP2S60 DSP Development Board

The Stratix® II EP2S60 DSP development board

2010-04-07 10:54:27 53

53 提出了一種基于IEEE802.16e的具有線性編碼復(fù)雜度的LDPC碼的硬件編碼器結(jié)構(gòu),并且在TSMC的0.18?滋m工藝庫的最惡劣情況下,通過Design Compiler工具綜合可以達(dá)到385MHz的速度。

2010-07-06 16:59:28 23

23 基于TMS320C6416高性能通用DSP,實現(xiàn)了對AWGN信道的信噪比(SNR)估計,并以此估計值設(shè)計了一種低密度奇偶校驗(LDPC)碼的譯碼系統(tǒng);詳盡介紹了集成SNR估計的譯碼系統(tǒng)的實現(xiàn)方案和流程;仿真

2010-07-27 16:28:32 11

11 低密度奇偶校驗碼(Low-Density-Parity-Checkcodes,簡稱LDPC碼)是第四代通信系統(tǒng)強(qiáng)有力的競爭者,它是一種逼近香農(nóng)限的線性分組碼,譯碼的復(fù)雜度較低;但它的直接編碼運(yùn)算量較大,

2010-08-09 15:06:22 0

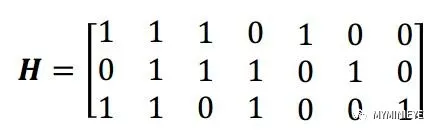

0 引言

低密度奇偶校驗(Low Density Parity Check Code,LDPC)碼是一類具有稀疏校驗矩陣的線性分組碼,不僅有逼近Shannon限的良好性能,而且譯碼復(fù)雜度較低, 結(jié)

2007-08-15 17:20:18 2135

2135

LDPC編譯碼LDPC碼是一種線性分組奇偶校驗碼,它采用基于因子圖的置信傳播(Belief Propagation,BP)迭代譯碼算法進(jìn)行譯碼。其性能接近Turbo碼,不規(guī)則LDPC碼甚至超過Tur

2009-03-01 17:36:05 2334

2334

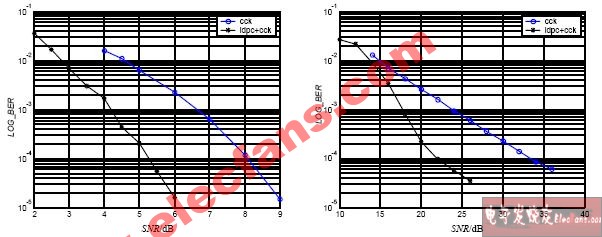

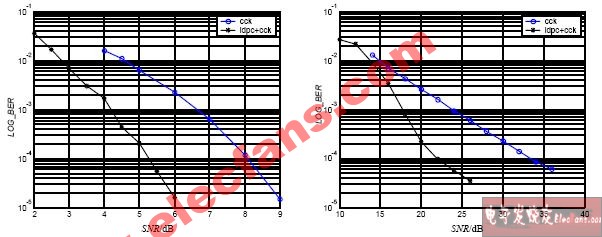

級聯(lián)LDPC和CCK碼的性能

從圖3可知,CCK在衰落信道下的性能很差,當(dāng)SNR=32 dB時,BER才近似為10-4。原因是因為CCK碼集合中各碼字間互相關(guān)特

2009-03-01 17:45:05 1865

1865

一種輸出格式可控的多碼率LDPC編碼器實現(xiàn)

0 引 言

目前,LDPC碼已廣泛應(yīng)用于深空通信、光纖通信、數(shù)字音視頻廣播等領(lǐng)域。由于有著較Turbo碼更優(yōu)秀的性能,

2009-11-25 09:56:43 1793

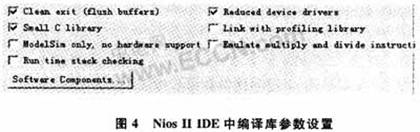

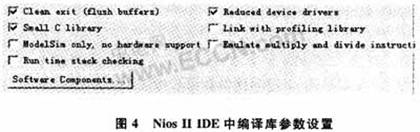

1793 為了提高設(shè)計性能(有時甚至只是為了達(dá)到設(shè)計要求),對所設(shè)計的SOPC系統(tǒng)進(jìn)行綜合優(yōu)化是非常必要的。論文結(jié)合具體工程,以Altera公司的FPGA EP2S60為例,探討了SOPC系統(tǒng)設(shè)計的綜合優(yōu)

2010-06-01 08:10:23 885

885

提出了一種基于FPGA并利用Verilog HDL實現(xiàn)的CMI編碼設(shè)計方法。研究了CMI碼型的編碼特點,提出了利用Altera公司CycloneⅡ系列EP2C5Q型號FPGA完成CMI編碼功能的方案。在系統(tǒng)程序設(shè)計中,首先產(chǎn)生m序列,然后程序再對m序列進(jìn)行CMI碼型變換。在CMI碼型變換過程中

2011-01-15 15:44:04 67

67 一、實驗?zāi)康?1、了解幾種常用的數(shù)字基帶信號。 2、掌握常用數(shù)字基帶傳輸碼型的編碼規(guī)則。 3、掌握常用CPLD實現(xiàn)碼型變換的方法。 二、實驗內(nèi)容 1、觀察NRZ碼、RZ碼、AMI碼、HDB3碼、

2011-03-24 15:28:15 0

0 LDPC(Low Density Parity Check)碼是Gallager最早于1962年提出的一種具有稀疏校驗矩陣的分組糾錯碼,亦稱Gallager碼。之后,在Turbo碼研究的巨大成功的帶動下,Mackay等人重新研究了LDPC碼,并發(fā)現(xiàn)

2011-03-31 16:15:53 32

32 本文設(shè)計實現(xiàn)了一種支持WIMAX標(biāo)準(zhǔn)的碼長、碼率可配置LDPC碼譯碼器,通過設(shè)計一種基于串行工作模式的運(yùn)算單元,實現(xiàn)了對該標(biāo)準(zhǔn)中所有碼率的支持

2011-06-08 09:52:17 2537

2537

本文研究高速 數(shù)據(jù)傳輸 中的低密度校驗(LDPC)碼編碼的原理、有效編解碼算法以及基于低密度校驗編碼的編碼調(diào)制系統(tǒng)的分析和設(shè)計方法。LDPC 碼是一類能夠達(dá)到Shannon 極限性能的線性分

2011-06-14 16:33:36 0

0 本文首先介紹了信道編碼的發(fā)展歷程,以及LDPC碼的基本原理和摹本概念,然后從校驗矩陣的構(gòu)造方法、迭代譯碼算法以及性能分析等幾個方面對LDPC碼進(jìn)行了討論, 介紹了相關(guān)技術(shù)的主

2011-08-26 11:44:01 0

0 本文提出了一種用FPGA實現(xiàn)糾錯編碼的設(shè)計思想,并以Altera MAX+PluslI為硬件開發(fā)平臺。利用FPGA編程的特點,用軟件編程方法,很好的解決了糾錯編碼中存在的碼速變換和實時性問題,實現(xiàn)

2011-11-10 17:10:59 61

61 根據(jù)IEEE802.16e標(biāo)準(zhǔn)中對LDPC碼的定義,利用FPGA對編碼器進(jìn)行了實現(xiàn)。所采用的算法使用了線性復(fù)雜度編碼,降低了邏輯資源占用量,并提高了編碼速度。

2011-12-07 14:06:14 33

33 建了一個基于Altera 的EP2S60硬件處理平臺,利用Altera提供的FFT IP核,在100 MHz系統(tǒng)時鐘下,數(shù)據(jù)吞吐率可達(dá)100 Ms/s。

2012-02-27 11:21:13 30

30 以Altera公司的FPGA EP2S60為例,探討了SOPC系統(tǒng)設(shè)計的綜合優(yōu)化方法。

2012-03-12 11:49:28 1720

1720

為實現(xiàn)某專用接口裝置的接口功能檢測,文中詳細(xì)地介紹了一種34位串行碼的編碼方式,并基于FPGA芯片設(shè)計了該類型編碼的接收、發(fā)送電路。重點分析了電路各模塊的設(shè)計思路。電路采

2012-06-18 12:37:09 41

41 在LDPC譯碼時,使用LLR BP算法其校驗節(jié)點的計算復(fù)雜度十分高,而且當(dāng)LDPC碼中有許多的短環(huán)時,譯碼性能也會降低。基于以上的這些問題提出了一個新的混合校驗變量過程,通過調(diào)整校

2012-07-06 16:44:03 42

42 上世紀(jì)60年代初,香農(nóng)的學(xué)生Gallager在他的博士畢業(yè)論文中首次提出了LDPC碼的概念和完整的譯碼方法,但是直到上世紀(jì)末期,隨著LDPC碼譯碼理論的進(jìn)步和計算機(jī)技術(shù)的發(fā)展,LDPC碼才以其

2012-11-07 15:05:11 0

0 本系統(tǒng)的設(shè)計是基于Altera公司的EP2S60系列的開發(fā)板,板上集成兩片 SDRAM存儲芯片、視頻輸入接口和VGA輸出接口

2012-12-16 10:07:31 1553

1553 香農(nóng)的學(xué)生Gallager首次提出了LDPC碼的概念和完整的譯碼方法,目前LDPC碼正向著高速高增益的方向發(fā)展。文中針對目前對高速LDPC碼譯碼技術(shù)的迫切需求,以CCSDS標(biāo)準(zhǔn)近地通信(8176,7154)

2013-07-26 11:17:00 0

0 這是verilog寫的可以實現(xiàn)卷積編碼1/2碼率的代碼,附帶測試文件0

2016-01-20 18:23:39 1

1 800Mbps準(zhǔn)循環(huán)LDPC碼編碼器的FPGA實現(xiàn)

2016-05-09 10:59:26 37

37 GA_高斯近似_LDPC_POLAR(極化碼)_構(gòu)造

2016-06-08 16:34:58 22

22 基于FPGA的經(jīng)濟(jì)型MPEG2運(yùn)動圖像編碼器IP核設(shè)計

2016-08-30 15:10:14 9

9 主要應(yīng)用于精密加工機(jī)械,紡織機(jī)械,機(jī)械手,自動化車庫等,EP50S系列外徑50mm軸型絕對值旋轉(zhuǎn)編碼器特點: 1、外徑50mm緊湊尺寸設(shè)計 2、多種輸出碼制:BCD碼,二進(jìn)制碼,格雷碼 3、多種高分辨率(720,1024) 4、IP64防護(hù)等級(防塵,防油污)

2017-09-28 14:33:07 9

9 的低運(yùn)算復(fù)雜度、低誤碼平臺譯碼的改進(jìn)算法。 該算法校驗節(jié)點的運(yùn)算采用修正最小和算法,外信息的更新采用串行方式,既保持了串行和積算法在有限迭代次數(shù)下譯碼門限低的優(yōu)點,又降低了節(jié)點運(yùn)算復(fù)雜度和誤碼平臺。用定點DSP芯片實現(xiàn)的非規(guī)則LDPC碼譯碼器的實測結(jié)果表明,該算法能以較低的實現(xiàn)復(fù)雜度獲

2017-10-20 10:41:11 0

0 咨詢委員會(CCSDS) 也將其推薦為應(yīng)用于深空通信的信道編碼方式。香農(nóng)指出,對于任何信道,只要采用隨機(jī)性編、譯碼方式,編碼長度接近無限大,在其信息傳輸速率不超過信道容量時,采用最佳的似然譯碼方案,必然存在一種編碼方式的誤碼率可以任意小。LDPC 碼之

2017-10-31 14:07:53 3

3 該文通過對低密度校驗(LDPC)碼的編譯碼過程進(jìn)行分析,提出了一種基于FPGA 的LDPC 碼編譯碼器聯(lián)合設(shè)計方法,該方法使編碼器和譯碼器共用同一校驗計算電路和復(fù)用相同的RAM 存儲塊,有效減少

2017-11-22 07:34:01 5141

5141

本文采用Altera公司Stratix II系列的EP2S90F1508C3芯片,以Quartus II 8.1為開發(fā)環(huán)境[4],采用硬件描述語言VHDL進(jìn)行SM3算法的FPGA實現(xiàn)。SM3算法實現(xiàn)

2017-11-24 15:33:59 3108

3108

信息協(xié)調(diào)是量子密鑰分發(fā)中的關(guān)鍵步驟,基于LDPC實現(xiàn)量子信息協(xié)調(diào)是當(dāng)前國內(nèi)外研究的焦點。目前QKD系統(tǒng)LDPC譯碼器普遍采用單碼字順序譯碼機(jī)制設(shè)計,且采用的是性能較差的準(zhǔn)循環(huán)LDPC碼,LDPC

2017-11-25 10:10:46 2

2 信道編譯碼技術(shù)可以檢測并且糾正信號在傳輸過程中引入的錯誤,能夠保證數(shù)據(jù)進(jìn)行可靠的傳輸[1]. LDPC碼的校驗矩陣具有稀疏的特性,因此存在高效的譯碼算法,其糾錯能力非常強(qiáng)。1981年,Tanner

2017-11-30 10:21:27 5864

5864

回路長度和回路數(shù)目的影響,回路的存在使譯碼信息重復(fù)迭代,性能下降。本論文通過計算機(jī)仿真,采用Matlab元胞數(shù)組,將二元校驗矩陣轉(zhuǎn)換為樹矩陣,實現(xiàn)了求解LDPC碼回路的算法。

2017-12-26 11:09:14 0

0 在衛(wèi)星通信中,如何提高抗干擾能力是需要重點關(guān)注的問題之一。多元域LDPC碼是通信界研究的熱點課題,較二進(jìn)制LDPC碼有更優(yōu)的糾錯性能。本文從衛(wèi)星通信的應(yīng)用角度出發(fā),對利用LU分解進(jìn)行編碼的通用編碼

2017-12-29 14:04:59 0

0 為設(shè)計出可近容量限傳輸且能普適應(yīng)用于慢、快衰落信道下的編碼協(xié)作方案,研究了基于卷積LDPC碼的編碼協(xié)作。基于卷積LDPC碼的鑿孔算法構(gòu)造出可2路傳輸?shù)姆执a字,實現(xiàn)編碼協(xié)作,并在第二幀分碼字傳輸階段引入了空時傳輸進(jìn)一步提升編碼協(xié)作的性能。仿真驗證了所提方案的有效性。

2018-01-16 14:38:02 0

0 準(zhǔn)循環(huán)結(jié)構(gòu);在此基礎(chǔ)上,使其與準(zhǔn)雙對角結(jié)構(gòu)相結(jié)合,構(gòu)造出的QC-LDPC碼圍長不會減小,且具有低復(fù)雜度可快速編碼的雙重特性。仿真結(jié)果顯示在加性高斯白噪聲( AWGN)和置信傳播(BP)譯碼算法下,所提方法構(gòu)造的QC-LDPC碼在誤碼率為10-5時,信

2018-01-16 18:48:05 0

0 出了一種基于FPGA并利用Verilog HDL實現(xiàn)的CMI編碼設(shè)計方法。研究了CMI碼型的編碼特點,提出了利用Altera公司CycloneⅡ系列EP2C5Q型號FPGA完成CMI編碼功能的方案

2018-05-31 04:38:00 3020

3020

的重視。基于準(zhǔn)循環(huán)LDPC(QC-LDPC)碼結(jié)構(gòu)特點,提出了一種支持多種碼率QC-LDPC 譯碼器的設(shè)計方法,并設(shè)計實現(xiàn)了一個能夠?qū)崟r自適應(yīng)支持三個不同H 陣的通用QC-LDPC 譯碼器。

2019-01-08 09:22:00 3913

3913

本文對2004年由王鵬提出的LDPC碼迭代編碼算法[11]進(jìn)行改進(jìn),轉(zhuǎn)變?yōu)檫m用于多元LDPC碼的編碼算法,稱為多元迭代編碼算法;2005年,Hu Xiaoyu提出了漸進(jìn)邊增長(Progressive Edge Growth,PEG)構(gòu)造算法[12],該算法譯碼性能好,但編碼復(fù)雜度較高。

2018-09-23 08:59:00 5484

5484

,低密度奇偶校驗碼)編碼,以水印方式嵌入到原始困像中;篡改檢測時,同樣對篡改圖像進(jìn)行線性隨機(jī)投影,得到的測量值作為邊信息,對提取的水印進(jìn)行LDPC譯碼。通過估計原始圖像和篡改圖像的壓縮測量值,并求解一個!范數(shù)問題,實現(xiàn)圖像的篡改檢測。仿真實驗證明,該算法不僅

2018-11-29 14:29:01 4

4 LDPC碼被認(rèn)為是當(dāng)今3D TLC和QLC存儲器中提高錯誤率的解決方案。然而它們并不適合每個市場。

2019-10-21 17:23:27 2511

2511 由于并行解碼性能與串行解碼在性能上并無差別,只是占用更多的硬件資源來換取更快的速度,并且每一種并行結(jié)構(gòu)只能針對具有某一特定校驗矩陣的LDPC碼。所以本文就以串行解碼硬件實現(xiàn)方式進(jìn)行實現(xiàn)分析。

2020-01-08 15:47:33 4473

4473

為塊準(zhǔn)循環(huán)結(jié)構(gòu),從而能夠并行化處理譯碼算法的行與列操作。使用這個架構(gòu),我們在Xilinx Virtex-5 LX330 FPGA上實現(xiàn)了(8176,7154)有限幾何LDPC碼的譯碼器,在15次迭代的條件下其譯碼吞吐量達(dá)到800Mbps。

2021-01-22 15:08:39 9

9 隨著硅片集成技術(shù)的高速發(fā)展,片上系統(tǒng)SoC(system-on-a-Chip)已經(jīng)成為現(xiàn)代數(shù)字系統(tǒng)設(shè)計的必然趨勢。SoC和一般數(shù)字系統(tǒng)最主要的區(qū)別是前者在單一硅片內(nèi)集成了獨(dú)立的嵌入式CPU,必要的存儲器控制器也要求集成到SoC芯片內(nèi),所以對SoC系統(tǒng)的軟硬件協(xié)同實時驗證便成為SoC設(shè)計的難點。

2021-03-17 17:04:25 3142

3142

結(jié)構(gòu)化LDPC碼可進(jìn)行相應(yīng)擴(kuò)展通過對編譯碼算法,優(yōu)化編譯碼結(jié)構(gòu)進(jìn)行調(diào)整,降低了編譯碼囂硬件實現(xiàn)中的關(guān)鍵路徑遲延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片實現(xiàn)了一個碼長10 240,碼率1/2的非正則結(jié)構(gòu)化LDPC碼編碼器和譯碼器。實現(xiàn)結(jié)果表明:該編碼器信息吞吐量為1.878 Gb/

2021-03-26 15:58:00 12

12 AD2S1210-EP:增強(qiáng)型產(chǎn)品數(shù)據(jù)表

2021-05-12 19:22:36 4

4 基于FPGA的800Mbps準(zhǔn)循環(huán)LDPC碼譯碼器

2021-06-08 10:31:31 26

26 瑞薩的RZ/A2M微處理器可以利用其獨(dú)特的動態(tài)可配置處理器(DRP)完美解決這一問題,實現(xiàn)了1280x720(1百萬)攝像頭輸入時,在8ms時間內(nèi)完成QR ,Micro QR, DataMatrix, AZTec 和漢信碼5種編碼格式的快速識別,下面讓我們看一下DRP是如何實現(xiàn)的。

2022-04-29 15:17:20 2535

2535

電子發(fā)燒友網(wǎng)站提供《基于FPGA的直接序列擴(kuò)頻和差錯控制碼編碼系統(tǒng)的實現(xiàn).pdf》資料免費(fèi)下載

2023-11-06 15:57:52 0

0

![]()

![]()

![]()

電子發(fā)燒友App

電子發(fā)燒友App

評論