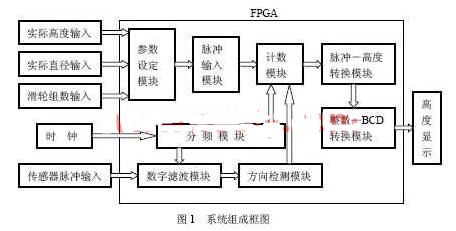

1. 概述

近些年來,各種電路功能,包括模擬電路和數(shù)字電路,越來越多地用單片集成電路來實(shí)現(xiàn)。采用單片集成電路不僅可以有效地提高電路可靠性和其它性能,而且也大大地降低了使用難度。許多單片集成電路的信息輸入和工作控制是通過數(shù)字信號(hào)實(shí)現(xiàn)的。常用的控制器件為微控制器和可編程邏輯器件。

由于微控制器一次只能執(zhí)行一條指令,因此它的主要局限性是工作速度。采用硬件方案設(shè)計(jì)的數(shù)字系統(tǒng)總是比軟件方案的數(shù)字系統(tǒng)的工作速度快。對(duì)數(shù)據(jù)的傳輸速率有較高要求的情況下,采用可編程邏輯器件是一種較好的選擇。可編程邏輯器件中的FPGA器件不僅提供通用邏輯單元,而且還提供了可以形成各種存儲(chǔ)器的嵌入式陣列塊。

2. nRF2401A無線收發(fā)芯片介紹

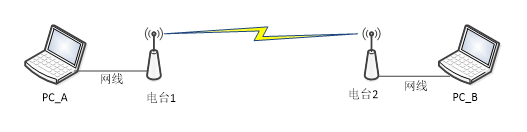

無線收發(fā)芯片nRF2401是挪威NORDIC SEMICONDUCTOR公司的產(chǎn)品,它把射頻收發(fā)電路集成在一塊芯片上,芯片內(nèi)部包含頻率綜合器、微波功率放大器、信號(hào)調(diào)制和解調(diào)器等部分。控制器件與nRF2401芯片之間的數(shù)字傳輸通過串行同步接口實(shí)現(xiàn)。nRF2401芯片作為一種單片無線收發(fā)芯片,它的射頻范圍為2.4GHz~2.5GHz,這個(gè)頻率范圍被稱作為工業(yè)—科學(xué)—醫(yī)療(Industrial-Scientific-Medical,ISM)頻帶,可以自由使用。

在正常工作模式下,發(fā)送端的nRF2401無線收發(fā)芯片可以從控制器件接收數(shù)據(jù),然后發(fā)射頻移鍵控(FSK)信號(hào);在接收端nRF2401無線收發(fā)芯片接收頻移鍵控信號(hào),然后把解調(diào)產(chǎn)生的數(shù)據(jù)送到控制器件。正常工作模式具有2種工作方式:ShockBurstTM方式和直接方式。

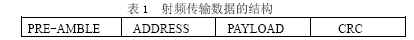

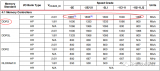

ShockBurstTM方式應(yīng)用片內(nèi)FIFO存儲(chǔ)器,從而使得控制器件與nRF2401芯片之間的數(shù)字傳輸可以采用較低的數(shù)據(jù)率,nRF2401芯片之間的數(shù)字無線電通信采用較高的數(shù)據(jù)率。這個(gè)優(yōu)點(diǎn)降低了射頻功率器件的工作時(shí)間,因此降低了電源的功耗,這在使用電池供電的場(chǎng)合非常重要。除此之外,ShockBurstTM方式對(duì)射頻傳輸數(shù)據(jù)幀的處理也比較簡(jiǎn)單。射頻傳輸數(shù)據(jù)幀包括4個(gè)部分,它的結(jié)構(gòu)如表1所示。這個(gè)結(jié)構(gòu)對(duì)于2種工作方式,ShockBurstTM方式和直接方式,都是一樣的。

PRE-AMBLE被稱為為前置代碼,這個(gè)部分的寬度為8位。當(dāng)工作在ShockBurstTM方式,發(fā)射芯片在發(fā)送數(shù)據(jù)時(shí)自動(dòng)把這個(gè)部分添加到射頻傳輸數(shù)據(jù)幀中;接收芯片從接收到的射頻傳輸數(shù)據(jù)幀中自動(dòng)取掉這個(gè)部分。

ADDRESS為用于接收的nRF2401無線收發(fā)芯片的地址,這個(gè)部分的最大寬度為40位。當(dāng)工作在ShockBurstTM方式,發(fā)射芯片在發(fā)送數(shù)據(jù)時(shí),控制器件向nRF2401無線收發(fā)芯片傳送的數(shù)據(jù)中必須包含這個(gè)部分;接收芯片從接收到的射頻傳輸數(shù)據(jù)幀中將自動(dòng)取掉這個(gè)部分。

PAYLOAD為實(shí)際需要傳輸?shù)男畔ⅰ.?dāng)工作在ShockBurstTM方式,這個(gè)部分包含的數(shù)據(jù)位數(shù)可以由下面公式計(jì)算。

PAYLOAD = 256 – ADDRESS – CRC

CRC為循環(huán)冗余檢查,這個(gè)部分的寬度可以為8位或者16位。循環(huán)冗余檢查功能只能在ShockBurstTM工作方式下使用,在直接工作方式下不能使用這個(gè)功能。發(fā)射芯片在發(fā)送數(shù)據(jù)時(shí)自動(dòng)把這個(gè)部分加到射頻傳輸數(shù)據(jù)幀中,它的寬度由芯片的配置字來決定;接收芯片從接收到的射頻傳輸數(shù)據(jù)幀中自動(dòng)取掉這個(gè)部分。

射頻傳輸數(shù)據(jù)幀中包含較長(zhǎng)的地址位和循環(huán)冗余檢查位雖然減少了實(shí)際需要傳輸?shù)男畔⑹褂玫臄?shù)據(jù)寬度,但是可以降低誤碼的發(fā)生概率。

3. 數(shù)字壓縮的實(shí)現(xiàn)

在采用16位接收地址和16位CRC編碼,可用于傳輸遙測(cè)數(shù)據(jù)的位數(shù)可由上式計(jì)算出,其數(shù)值為224位。為保證待傳輸?shù)臏y(cè)量信息具有足夠的動(dòng)態(tài)范圍,遙測(cè)系統(tǒng)的所有模擬/數(shù)字轉(zhuǎn)換都采用12位的模擬/數(shù)字轉(zhuǎn)換器。使用無線收發(fā)芯片nRF2401傳輸12位的PCM編碼,一次只能傳輸18路測(cè)量信號(hào)。

對(duì)于監(jiān)測(cè)的模擬信號(hào),小振幅信號(hào)比大振幅信號(hào)出現(xiàn)的可能性大,因此采用非線性編碼可以用較少的數(shù)據(jù)位數(shù)獲得需要的精度,即小振幅信號(hào)使用較多的編碼,大振幅信號(hào)使用較少的編碼。這樣的非線性編碼系統(tǒng)也被稱作為壓縮擴(kuò)展系統(tǒng),數(shù)據(jù)在傳輸之前先被壓縮,然后在接收端再被擴(kuò)展。

μ律壓縮擴(kuò)展是一種常用的算法,它的壓縮特性為:

![]()

式中,Vmax:最大未壓縮模擬輸入信號(hào)幅度;Vin:當(dāng)前模擬輸入信號(hào)幅度;μ:定義壓縮量的參數(shù);Vout:壓縮模擬輸出信號(hào)幅度。μ值越高,壓縮量越大,μ值為0時(shí),特性為直線,這時(shí)無壓縮。

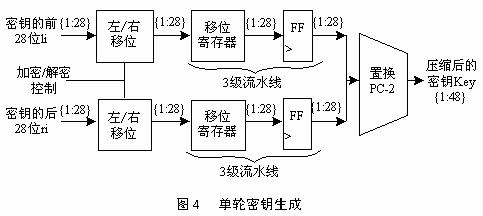

數(shù)字壓縮把12位線性編碼轉(zhuǎn)換成8位非線性編碼,這樣在同樣的一幀224位測(cè)量數(shù)據(jù)就可以容納28路信號(hào),比線性編碼多出10路。這里轉(zhuǎn)換的過程是使用8個(gè)直線段來近似μ值為255的模擬壓縮特性,每個(gè)直線段的斜率等于前一段的二分之一。

8位壓縮碼由3段標(biāo)識(shí)碼和5位幅度碼組成。表2給出12位到8位數(shù)字壓縮和擴(kuò)展編碼。12位線性編碼中標(biāo)為X的位在壓縮時(shí)被丟棄,標(biāo)為A、B、C、D和E的位被原樣傳輸。在段0和段1,數(shù)據(jù)沒有被壓縮,原始的12位線性編碼可以被完整地恢復(fù);在段2,壓縮比為2:1,64個(gè)線性編碼只生成32個(gè)壓縮編碼;在段3,壓縮比為4:1,128個(gè)線性編碼只生成32個(gè)壓縮編碼。依次類推,在段7,壓縮比為64:1,2048個(gè)線性編碼只生成32個(gè)壓縮編碼。

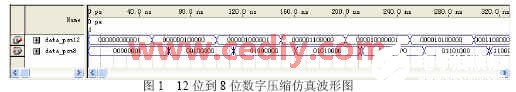

采用查表的方法是一種常用的編碼方法,但是對(duì)于表2所示的壓縮編碼,使用硬件描述語言更加簡(jiǎn)單,編碼速度更快、也節(jié)省可編程邏輯器件的資源。使用VHDL的并行條件信號(hào)賦值語句實(shí)現(xiàn)壓縮編碼的代碼如下,data_pcm12為12位線性編碼,data_pcm8為8位壓縮編碼。圖1給出使用ALTERA公司的EP1C3T100I7芯片的仿真波形圖,完成一次壓縮編碼只需要不到15ns的時(shí)間。

data_pcm8 《= “000” & data_pcm12(4 DOWNTO 0) WHEN data_pcm12 《“000000100000” ELSE

“001” & data_pcm12(4 DOWNTO 0) WHEN data_pcm12 《“000001000000” ELSE

“010” & data_pcm12(5 DOWNTO 1) WHEN data_pcm12 《“000010000000” ELSE

“011” & data_pcm12(6 DOWNTO 2) WHEN data_pcm12 《“000100000000” ELSE

“100” & data_pcm12(7 DOWNTO 3) WHEN data_pcm12 《“001000000000” ELSE

“101” & data_pcm12(8 DOWNTO 4) WHEN data_pcm12 《“010000000000” ELSE

“110” & data_pcm12(9 DOWNTO 5) WHEN data_pcm12 《“100000000000” ELSE

“111” & data_pcm12(10 DOWNTO 6);

4. nRF2401A無線收發(fā)芯片數(shù)據(jù)接口的設(shè)計(jì)

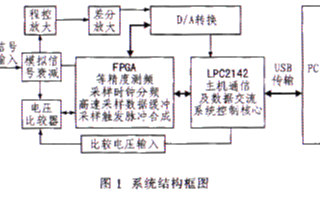

無線收發(fā)芯片nRF2401的ShockBurstTM工作方式可以使得控制器件與該芯片之間的數(shù)字傳輸可以采用較低的數(shù)據(jù)率,以降低對(duì)控制器件的要求;nRF2401芯片之間的數(shù)字無線電通信采用較高的數(shù)據(jù)率,最高為1Mbps,以降低電源的功耗。由于無線收發(fā)芯片nRF2401從控制器件獲取數(shù)據(jù)和發(fā)射頻移鍵控信號(hào)是分時(shí)進(jìn)行的,因此控制器件較低的工作速度將降低實(shí)際的數(shù)據(jù)傳輸速率。

nRF2401芯片的最高數(shù)據(jù)傳輸速率也為1Mbps,由于數(shù)據(jù)格式的非標(biāo)準(zhǔn),如果采用微控制器實(shí)現(xiàn)則只能采用位尋址指令來實(shí)現(xiàn),多條指令才能完成一位數(shù)據(jù)的傳送,使得達(dá)到較高的數(shù)據(jù)傳輸速率非常困難。應(yīng)用FPGA器件實(shí)現(xiàn)需要的串行同步接口非常方便,使用2MHz的時(shí)鐘,第一個(gè)時(shí)鐘用于準(zhǔn)備數(shù)據(jù),第二個(gè)時(shí)鐘用于產(chǎn)生同步時(shí)鐘,即可獲得1Mbps的數(shù)據(jù)傳輸速率。

采用有限狀態(tài)機(jī)(FSM)的時(shí)序電路模型,使用VHDL實(shí)現(xiàn)的nRF2401A無線收發(fā)芯片數(shù)據(jù)接口代碼格式如下:

IF (data_read = ‘0’) THEN

current_state 《= 0;

ELSIF (data_read = ‘1’) THEN

IF (clk_sys‘EVENT AND clk_sys = ’1‘) THEN

CASE current_state IS

??????

WHEN 83 =》

current_state 《= 84;

ce_read 《= ’1‘; data_addr 《= “00000”;

ce 《= ’1‘; clk1 《= ’0‘; data 《= pcm8_m(199); WHEN 84 =》

current_state 《= 85;

ce_read 《= ’1‘; data_addr 《= “00000”;

ce 《= ’1‘; clk1 《= ’1‘; data 《= pcm8_m(199);

??????

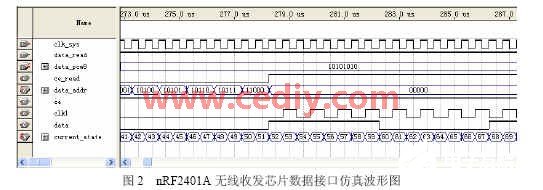

圖2是實(shí)現(xiàn)的nRF2401A無線收發(fā)芯片數(shù)據(jù)接口代碼模塊的仿真波形圖。遙測(cè)系統(tǒng)完成所有模擬/數(shù)字轉(zhuǎn)換器輸出數(shù)字信號(hào)的讀取,并把這些12位的數(shù)據(jù)壓縮為8位數(shù)據(jù)存入一個(gè)雙口RAM,接著產(chǎn)生一個(gè)讀數(shù)信號(hào)data_read。在讀數(shù)信號(hào)低電平期間有限狀態(tài)機(jī)狀態(tài)信號(hào)current_state清零,低電平過后,在時(shí)鐘信號(hào)clk_sys控制下實(shí)現(xiàn)nRF2401A的數(shù)據(jù)接口要求的時(shí)序。

在狀態(tài)機(jī)執(zhí)行過程中,首先產(chǎn)生雙口RAM的讀使能信號(hào)ce_read和地址信號(hào)data_addr,把數(shù)據(jù)轉(zhuǎn)存在一個(gè)具有200位的信號(hào)pcm8_m中;接著逐位向nRF2401A無線收發(fā)芯片傳輸16位地址和信號(hào)pcm8_m中包含的200位數(shù)據(jù)。完成所有信息的傳送以后,狀態(tài)機(jī)停在最后一個(gè)狀態(tài),等待下一個(gè)低電平的讀數(shù)信號(hào)data_read。

5. 總結(jié)

本文作者創(chuàng)新點(diǎn): 使用nRF2401A無線收發(fā)芯片使得人工從現(xiàn)場(chǎng)獲取數(shù)據(jù)改變?yōu)檫b測(cè)獲取數(shù)據(jù),利用FPGA器件獲得要求的數(shù)據(jù)傳輸速率。應(yīng)用ALTERA公司的FPGA器件EP1C3T100I7實(shí)現(xiàn)nRF2401A的數(shù)據(jù)接口占用了其2910個(gè)邏輯單元的358個(gè)(12%),器件還有足夠的資源實(shí)現(xiàn)模擬/數(shù)字轉(zhuǎn)換器的控制以及整個(gè)遙測(cè)系統(tǒng)的控制。EP1C3T100I7內(nèi)部的嵌入式陣列塊具有59904位,這些資源可以用于實(shí)現(xiàn)雙口RAM。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論