本文介紹了一種基于NIOS II軟核處理器實現對LCD-LQ057Q3DC02控制的新方法。在設計中利用FPGA的Altera的SOPC Builder定制NIOS II軟核處理器及其與顯示功能相關的“軟” 硬件模塊來協同實現顯示控

2011-11-09 11:30:07 2304

2304

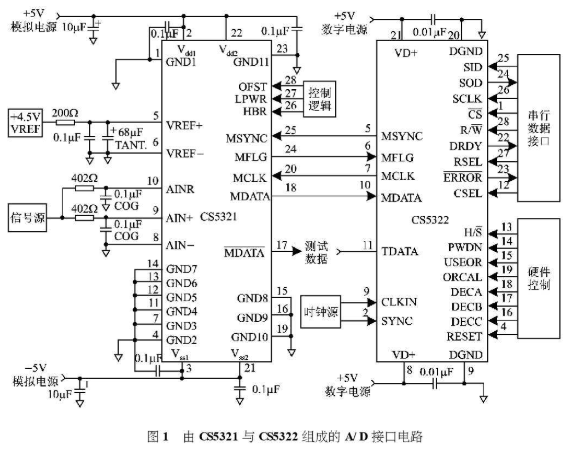

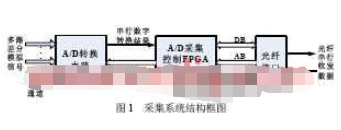

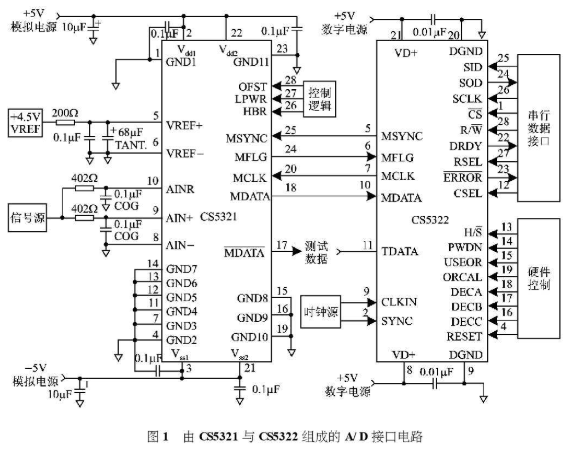

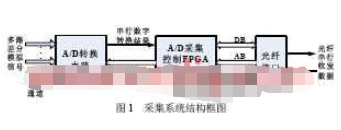

∑一△A/D轉換技術以其高分辨率和大的動態范圍在數據采集系統中得到了廣泛應用:但∑一△A/D轉換器通常采用串行傳輸,因此由它實現的采集系統大多包含串并轉換單元。為了達到系統設計簡化,降低系統成本的目的,探討一種直接用串行傳輸的多通道數據采集系統的方法十分有必要。

2020-06-26 09:51:00 3405

3405

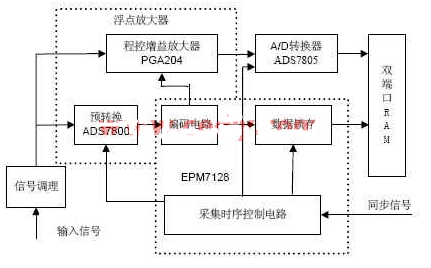

到限制。因此,本文利用可編程邏輯控制器CPLD,由硬件控制模數轉換和數據存儲,從而最大限度地提高系統的信號采集和處理能力。

2020-08-07 17:21:42 1879

1879

在測量、工業控制系統中,A/D變換器的數據采集精度對系統的性能有著至關重要的影響。傳統的A/D器件,大都采用逐次逼近方式,而CS5396/97采用了∑-Δ技術,可實現24位的高分辨率。∑-Δ技術

2021-03-22 16:42:38 4498

4498

偏硬件:接口電路中的門組合電路;偏軟件:算法、接口控制器實現中的狀態機群或時序電路。隨著邏輯設計的深入,復雜功能設計一般基于同步時序電路方式。此時,邏輯設計基本上就是在設計狀態機群或計數器等時序電路

2021-11-10 06:39:25

多個AD7656-1級聯形成菊花鏈實現多個通道同時進行數據采集,并通過一個或多個串口發送數據給主控處理器。以S3C2410A為主控處理器,多個AD7656-1組成菊花鏈實現多通道、高精度的ADC,在很大程度

2018-11-26 11:16:15

ARM I2C 總線接口模塊在數據采集中的應用在以ARM S3C44BOX為核心處理器的新型流量積算儀表的設計中,利用ARM自帶的12C總線接口模塊擴展了A/D轉換芯片

2009-03-14 18:06:30

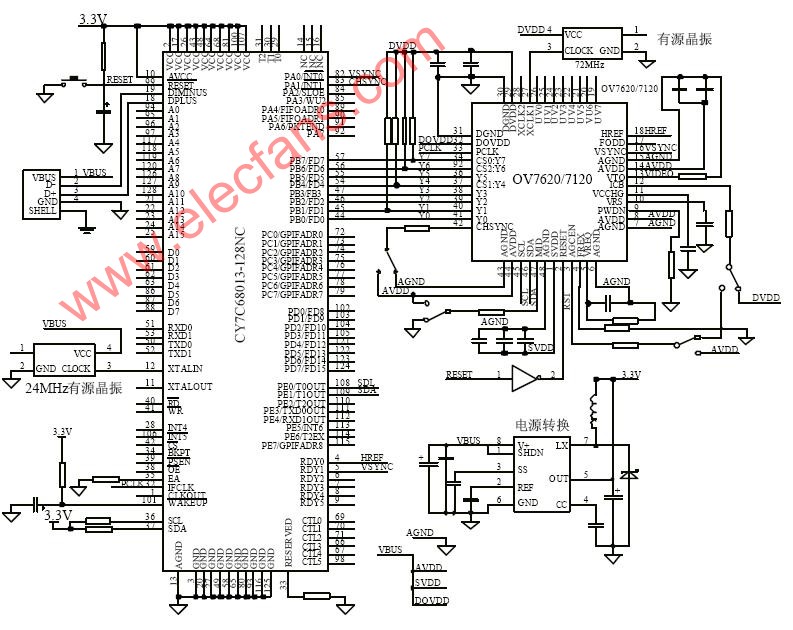

核心,以WinCE為軟件平臺,能實時、連續地采集清晰的視頻數據。1 系統結構框圖及視頻數據采集原理視頻數據采集系統結構如圖1所示。從圖1中可以看出。系統由嵌入式微處理器S3C2440、存儲器(包括

2019-08-06 08:30:15

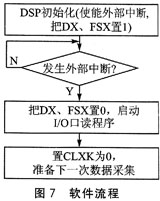

TMS320VC5509 為核心的數據采集處理系統,通過對FIFO、SDRAM 和TMS320VC5509 DMA 控制器的介紹,分別給出了具體的接口電路硬件設計和實際軟件的代碼示例。關 鍵 詞

2009-04-28 10:47:02

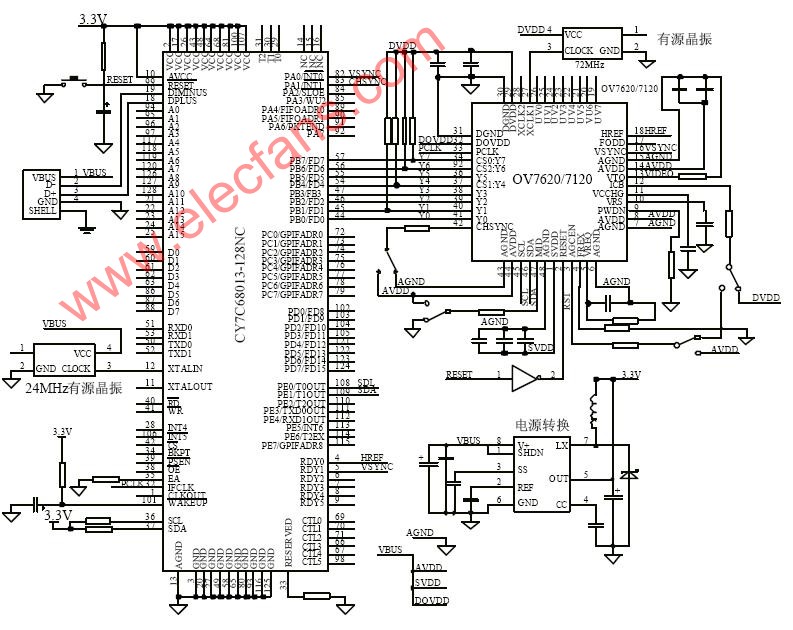

的EZ-USB FX2系列智能USB接口芯片。其作用是將主機所發送的命令序列經USB2.0端口輸出,實現對數據采集系統的控制;同時把A/D轉換器采集的數據以高速的數據序列形式發送到主機。其中,USB2.0端口

2020-01-07 07:00:00

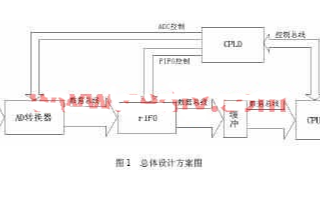

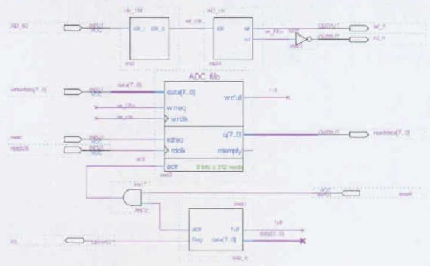

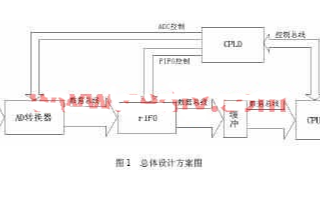

FPGA處理數據的時間,所以整個系統實現了流水線操作。1 系統的總體設計系統硬件主要由信號采集模塊、FIFO、FPGA和SEP3203處理器組成。信號采集模塊主要包括信號接收器和A/D轉換模塊。接收

2019-04-26 07:00:06

到IDT7202的寫端口。確保采集到的數據為有效數據。 圖3是SEP3203處理器輸入到FPGA內部的控制信號的仿真波形圖。in_rst_n_a是復位信號,in_we_n和in_cs_n是SEP3203

2018-12-05 10:13:09

圖像數據進入預處理模塊,經預處理后的圖像數據送入SDRAM存儲器,由Nios II處理器進行圖像的后續處理和控制。處理后的圖像經數模轉換在監視器上實時顯示。 1.1 圖像采集接口電路設計 本系統

2018-10-31 16:54:52

數據采集與控制單元,以CYPRESS公司的高速USB接口芯片CY7C68001為基礎,利用DSP片上A/D轉換器采集數據,經處理后把數據通過USB總線傳輸至PC機,PC機接收到數據后按照用戶的要求通過

2014-12-16 11:32:57

數據采集模塊、碰撞壓力處理電路等組成的外圍設備,還有以32位Nios II CORE為主體的核心邏輯兩個主要部分組成,系統終端硬件框圖如圖1所示。1.1 外圍設備外圍設備是指某些具體控制電路或模塊接口

2015-01-30 11:05:50

采集。對于兩路數據采集電路,A/D與DSP的接口連接是一樣的。兩個A/D同時將和路與差路信號采樣,并分別送入兩個FIFO;DSP分時從兩個FIFO中讀出采集的數據,完成數據的采集。1 數據采集系統組成

2012-12-25 15:45:49

`一、項目設計背景及概述 本文介紹了基于單片機的數據采集系統。數據采集技術是信息科學的重要分支之一, 它研究信息數據的采集、存儲、處理以及控制等問題。它是對傳感器信號的測量與處理, 以微型計算機等高

2014-01-11 18:15:49

基于NIOS II 軟核處理器的SOPC 技術摘要:介紹了基于NIOS II 軟核處理器的SOPC 技術,分析了傳統方法和基于SOPC 技術的方法實現擴頻收發機的優劣,詳細說明了嵌有雙NIOS II

2009-10-06 15:05:24

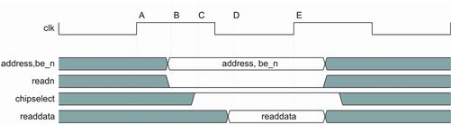

在FPGA系統中,實現對外部A/D數據采集電路的控制接口邏輯,由于其邏輯功能不是很復雜,因此可采用自定義的方式。采用這種方法進行設計有兩種途徑。①從軟件上去實現。這種方案將NIOS處理器作為一個主控制器

2019-04-17 07:00:01

在FPGA系統中,實現對外部A/D數據采集電路的控制接口邏輯,由于其邏輯功能不是很復雜,因此可采用自定義的方式。采用這種方法進行設計有兩種途徑。①從軟件上去實現。這種方案將NIOS處理器作為一個主控制器

2019-04-25 07:00:02

摘要:設計了一種在Nios II處理器上的CCD數據采集系統。電荷耦合器件(Charge-Coupled Device,CCD)采集到的信號經過前端的差分運放處理后再進行A/D轉換,轉換后的數據存儲

2019-06-03 05:00:06

CMOS傳感器件,本指紋采集系統采用傳感器的微處理器總線(MCU)模式,傳感器的8位數據線直接與DE2開發板的擴展口相接,采用Nios II自定義外設的接口形式來對FPS200指紋圖像傳感器進行初始化控制

2019-04-29 07:00:08

的網絡數據傳輸。3、 系統結構高速同步數據采集系統主要包括以下幾個部分:ARM控制器、存儲電路、FPGA邏輯控制電路、A/D轉換電路、FIFO緩存、電源電路、接口電路等。系統具備多通道數據采集接口

2010-08-31 09:14:55

接口,它使電路工作在更加平穩、簡潔而易丁控制,同時也提高了ARM的工作效率。為了提高通信速度,這里采用通用申行總線(USB)技術米與PC進行通信。ARM是用來控制主處理器的數據采集,數據的計算和數據傳輸。結果證明,整個系統能高效運作。該系統可應用于高速數據采集及多路模擬信號的工作環境下。

2023-09-26 07:41:28

/模轉換器DAC0832構成一個數據采集系統,并用CPLD/FPGA實現數據采樣、D/A轉換輸出、有關數據顯示的控制,單片機完成對A/D轉換數據運算。電路如圖1所示。系統功能如下:系統按一定速率采集輸入

2018-12-10 10:18:34

1 背景知識隨著信息技術的發展,特別是各種數字處理器處理速度的提高,人們對數據采集系統的要求越來越高,特別是在一些需要在極短時間內完成大量數據采集的場合,對數據采集系統的速度提出了非常高的要求

2018-08-09 14:28:00

了如何通過FPGA實現RS 232接口的時序邏輯設計。關鍵詞:FPGA;時序電路;RS 232;串行通信

2019-06-19 07:42:37

基于FPGA的數據采集系統IEE ... 介紹了數據采集系統中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設計,給出了系統硬件設計和FPGA邏輯設計,討論了IEEE1394總線

2012-08-11 15:43:47

的輸入輸出接口設計就顯得尤為重要。1 高速采集系統介紹 數據采集系統原理框圖如圖1所示,輸入的中頻信號經A/D采樣電路采樣后,轉換成LVDS信號送入FPGA中,或通過FPGA的端口RocketIO從高速接口

2018-12-18 10:22:18

數據采集與控制單元,以CYPRESS公司的高速USB接口芯片CY7C68001為基礎,利用DSP片上A/D轉換器采集數據,經處理后把數據通過USB總線傳輸至PC機,PC機接收到數據后按照用戶的要求通過

2018-12-26 07:00:05

A/D轉換器采集數據,暫存于數據緩沖區,再根據主機命令發給主機。這部分功能由一個單片機及接口來實現是最優方式。 數據通信部分應包含:簡單、高效、通用的數據通信模式和軟硬件支持。它應能在數據采集和數據處理

2018-07-02 05:07:53

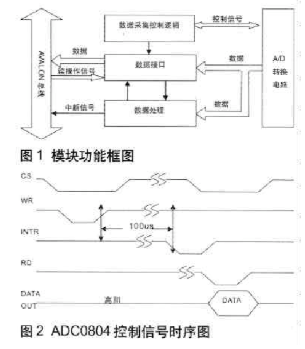

基于PIC單片機USB接口的數據采集系統設計 我們把所設計的數據采集系統功能分解為三大部分:數據采集部分、數據通信部分、數據處理部分。 數據采集部分應包含:A/D轉換器,時序、模式控制,數據緩沖

2017-08-23 11:30:01

.應用可編程邏輯器件EPM7128SLC和8路模擬多路選擇器ADG508A實現采集信號的選通設計,介紹單片機80C196KB內A/D轉換器在采集電路中的使用方法,使用雙端口存儲器IDT7130實現數據的雙機傳輸

2011-03-08 14:24:55

1 引言 圖像采集是數字圖像處理、圖像識別和機器視覺的基礎,其應用領域非常廣泛。主要采用CCD或CMOS等光電轉換器件把光學影像轉化為數字信號,然后利用相應的接口將數據輸入到處理器中進行圖像

2019-07-02 08:11:34

高質量的A/D采集卡及調理放大器是影響其發展的一個重要因素,如何設計一款基于USB接口的實用型數據采集卡?

2021-04-07 06:40:16

在FPGA系統中,如何實現對外部A/D數據采集電路的控制接口邏輯?如何設計NIOS系統外設方面?

2021-04-12 07:16:31

本文使用符合PCI電氣特性的FPGA芯片進行簡化的PCI接口邏輯設計,實現了33MHz、32位數據寬度的PCI從設備模塊的接口功能,節約了系統的邏輯資源,且可以將其它用戶邏輯集成在同一塊芯片,降低了成本,增加了設計的靈活性。

2021-05-08 08:11:59

前言FPGA 可以實現高速硬件電路,如各種時鐘,PWM,高速接口,DSP計算等硬件功能。這是Cortex-M 處理器軟件無法比擬的。要實現FPGA 的邏輯設計,對于嵌入式系統工程師又是比較復雜和具有

2021-12-21 06:13:49

的可編程邏輯器件EPM7256A完成對數據的緩存和傳輸的各種時序控制以及開關量采樣時序、路數判別。采用FIFO器件作為高速A/D與DSP處理器間的數據緩沖,有效地提高了處理器的工作效率。

2020-12-31 07:52:43

CLC5958的內部結構及基本特性CLC5958應用的注意事項有哪些采用可編程邏輯器件和A/D轉換器組成的高速數據采集卡的設計方案

2021-04-15 06:50:05

。FPGA - 包含數據采集控制和邏輯(包括觸發邏輯)、檢錯、DSP 接口、存儲器地址解碼器、計數器和輸出控制。控制邏輯選擇一個數據采集時鐘,處理各種觸發器,并將獲取的數據傳輸至數據采集通道的內部存儲器中

2012-12-12 11:48:15

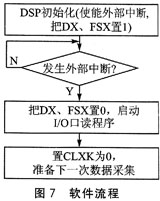

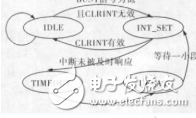

或者DSP為核心,控制數據采集并對數據進行相應處理,A/D轉換器的啟動、通道選擇、數據傳輸和讀取均依靠軟件編程來實現。

2019-08-15 07:07:46

或者DSP為核心,控制數據采集并對數據進行相應處理,A/D轉換器的啟動、通道選擇、數據傳輸和讀取均依靠軟件編程來實現。由于受MCU或者DSP執行指令時間的限制,這種采集方案的速率和效率較低,難以適應

2019-08-16 06:57:48

.ARM的功能過于復雜,適合于設計好的人機界面的場合.有些器件將接口協議處理器和采集卡處理器集成在一體,這些芯片應該有更好的使用價值.第五步,選擇數據采集電路。很多公司提供采樣芯片:ADI,TI

2013-02-27 15:02:06

數據采集邏輯原理圖/電路圖

2019-10-10 09:00:31

”的設備,既能充分滿足傳感器前端的模擬性能要求,又具備與系統主機處理器接口相連的足夠靈活性。這樣做還有更多好處。圖 1 闡述了這一理念及上述各種方法。 圖 1. 智能 ADC 數據采集系統的發展 小智慧

2018-11-01 14:40:19

”的設備,既能充分滿足傳感器前端的模擬性能要求,又具備與系統主機處理器接口相連的足夠靈活性。這樣做還有更多好處。圖 1 闡述了這一理念及上述各種方法。圖 1. 智能 ADC 數據采集系統的發展 小智慧有大作

2018-12-11 11:06:14

本文設計了一種在多處理器系統中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數據存儲器加載數據時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

的采集和處理,多數是以單片機或未處理器為控制核心,雖編程簡單、控制靈活,但缺點是單片機的速度慢、控制周期長。基于FPGA的數據采集系統設計具有開發周期短,靈活性強、通用性能好、易于開發、擴展等優點。下圖

2012-11-05 12:29:34

本系統的電原理如上圖,CH371是USB接口芯片,MAX197多路AD轉換器做數據采集,電腦對采集的數據進行處理。 CH371是南京沁恒電子出品的一種簡單易用的USB接口芯片,它包括芯片本身和計算機

2021-05-10 07:31:23

怎么實現A/D數據采集接口的設計?

2021-04-20 07:19:20

怎么設計一種高速數據采集系統?數據采集系統的組成及原理是什么?如何實現高速A/D轉換器與DSP的接口設計?

2021-04-12 06:10:22

的硬件邏輯和外部設備接口,以及整個系統設計的邏輯譯碼電路。達到高度集成的目的。本系統的特點是: 1)NIOSⅡ嵌入式微處理器成本低。開發周期短,提高了產品的性價比和研發速度。2)采用可編程邏輯器件使

2019-04-29 07:00:06

的硬件電路SD卡采用SPI總線方式與處理器連接,其電路原理如圖2所示。圖2 SD 卡接口電路圖1.5 NiosII的構建過程首先要考慮到的是使用什么樣的Nios II,Nios II分為幾個等級,有標準

2019-05-29 05:00:04

采用sopc內嵌32位的軟核處理器nios,實現了一個uart串行口和以太網接口的轉換器(以下簡稱轉換器),并基于microtronix公司針對nios處理器移植的μclinux開發了應用程序.其系統結構

2019-04-18 07:00:07

輸入信號經過信號調理電路濾波、放大后送給C8051F000,此單片機自帶的A/D轉換器將輸入的模擬信號轉換為數字信號,并通過USB接口傳送給計算機。計算機也可以通過USB接口向C8051F000發送

2019-05-23 05:01:03

文章介紹了基于USB接口芯片的數據采集和控制卡的設計,整個系統主要由六個部分組成:USB接口芯片、本地端控制器、A/D、D/A、計數器以及DIO口,通過主機應用軟件來控制USB口的讀

2009-06-29 08:39:54 25

25 介紹了一種用于磁懸浮軸承實時控制的數據采集與處理系統, 該系統采用數字信號處理器(DSP) 作為主控單元, 可對五路傳感器信號實現高速采集, 所采用的A öD 轉換器集成在DSP 內部

2009-07-03 09:06:31 11

11 本文以Nios II 嵌入式軟處理器為核心,利用USB 控制芯片CH372,設計了基于Nios II 嵌入式軟處理器的USB 通信接口。本文重點介紹了USB 接口的硬件實現方案,分析了CH372 的通信流程,并

2009-08-28 11:34:28 33

33 基于PLD芯片的時序邏輯設計與實現:原理圖輸入設計直觀、便捷、操作靈活;1-1、原理圖設計方法簡介QuartusII已包含了數字電路的基本邏輯元件庫(各類邏輯門及觸發器),宏

2009-10-29 22:03:10 0

0 針對圖像處理中數據采集與處理的現狀,介紹了基于DSP 和PCI 控制器的高速數據的實時采集、存儲和處理的方法,并分別對電路原理圖的硬件設計和PCI 接口的軟件設計做了闡述。

2009-12-31 14:15:32 22

22 在NIOS-II 系統中A/D 數據采集接口的設計與實現摘要:進行 SOPC 開發,很有必要學習一下定制NIOS 外設的方法和技巧。本文就是基于這種目的,詳細的論述了在NIOS 系統中A/D 數據

2010-02-08 09:55:43 23

23 摘要:給出了基于A S M 圖的數字集成電路控制器的設計的主要電路實現方法,并給出了目前最常采用的方法——EDA法.關鍵詞: A S M 圖; 邏輯設計; E DA; On e Ho t

2010-04-26 11:25:44 14

14 設計了一種以DSP嵌入式處理器為核心、基于FPGA技術的四通道數字式超聲探傷數據采集與處理系統。采用高速A/D轉換芯片,在對超聲回波信號采集的同時實現了采樣數據的在線壓縮,

2010-08-05 14:47:23 24

24 針對眾多低成本數據采集需求,采用帶有片上USB控制器和D/A轉換器的混合信號微處理器C8051F340,設計了一款可通過USB接口和LabVIEW圖形用戶界面實現與PC機聯機的數據采集器,同時借

2010-12-14 16:59:42 270

270 換體DMA高速數據采集電路的CPLD實現

介紹了換體DMA高速數據采集電路原理及其CPLD實現。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 1008

1008

數據采集邏輯原理圖/電路圖

2009-04-17 20:16:17 3339

3339

摘要: 提出了一種基于ISP技術實現高速數據采集的方法,給出了使用VHDL語言和原理圖完成數據采集模塊中地址發生器和比較電路的部分邏輯設計,只要將所設計的

2009-06-20 14:51:20 1008

1008

以太網接口的數據采集控制器

LabJack UE9--以太網接口的數據采集控制器。LabJack UE9 具有 USB ( 2.0 全速)和以太網的接口。內置的 4

2009-09-09 08:24:27 1065

1065 基于ADS8364的數據采集系統設計

開發了基于DSP和ADS8364的數據采集處理系統。該系統主要由信號調理模塊、A/D轉換模塊、DSP處理器模塊、CPLD邏輯控制模塊、Flash存儲器模

2009-09-19 09:30:20 1970

1970

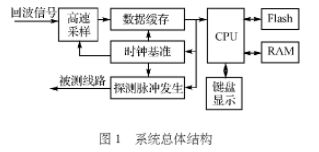

基于A/D和DSP的高速數據采集技術

中頻信號分為和差兩路,高速A/D與DSP組成的數據采集系統要分別對這兩路信號進行采集。對于兩路數據采集電路,A/

2009-10-17 10:17:41 1546

1546

本文設計了一種以嵌入式微處理器Nios為核心的電纜故障檢測儀,應用A/D器件和FPGA組成可變頻率的高速數據采集系統,利用低壓脈沖反射法原理來實現線纜的斷路、短路、斷路點、短路點

2011-04-23 10:47:07 1382

1382

基于Nios II 軟核處理器和USB 接口設計了一種工業CT 數據采集模塊測試系統. 論述了系統的方案設計、硬件設計、軟件設計. 利用Nios II 進行設計簡化了系統結構,提高了設計靈活性,優化了

2011-09-14 15:12:01 37

37 這里介紹了一種基于ARM7風機監測儀的數據采集接口方案,A/D芯片就是采用MAXl320,該監測儀的處理器采用Philips公司的LPC2290。

2011-09-27 11:42:29 5806

5806

Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實現僅需35美分。Altera的Stratix 、Stratix GX、 Stratix II和 Cyclone系列FPGA全面支持Nios II處理器,以

2011-11-30 16:33:33 6642

6642

中頻信號分為和差兩路,高速A/D與DSP組成的數據采集系統要分別對這兩路信號進行采集。對于兩路數據采集電路,A/D與DSP的接口連接是一樣的。兩個A/D同時將和路與差路信號采

2012-03-28 10:41:38 6328

6328

本文以帶有片上A/D轉換器的C8051F340處理器和USB接口芯片CH375為基礎,設計了一款可對100 kHz以下的低頻模擬信號進行10位深度采樣的低成本數據采集器。該數據采集器具有USB主機功能,可

2012-05-11 11:07:09 3607

3607

Nios II 系列處理器配置選項:This chapter describes the Nios II Processor parameter editor in Qsys and SOPC

2012-10-17 14:08:42 17

17 FPGA由于集成了超大規模集成電路和可編程器件的諸多優點,其在現代工業生產和科學研究中的數據采集和處理的應用越來越廣泛。本文針對SSI接口類傳感器數據采集與數理需求,設計了以FPGA為核心處理器的多

2015-12-18 15:48:43 138

138 基于軟核Nios_Ⅱ的SOPC數據采集系統的設計

2016-02-17 10:07:11 41

41 基于ARM處理器的USB數據采集系統

2017-09-25 13:41:09 5

5 設計了基于FPGA與ARM 芯片的數據采集系統,FPGA 負責控制A/D轉換器,保證了采樣精度與處理速度,ARM負責邏輯控制及與上位機交互的實現,并將采集到的數據通過USB高速上傳至主機進行實時處理。對模擬數據采集的測試結果達到了較高的采樣精度和速度,驗證了整個系統的高速性和可行性。

2017-11-18 12:47:10 5019

5019

在現代工業生產控制系統中,需要實現大量數據的實時采集和處理,以使生產過程得到及時控制。參考文獻[1]介紹了基于一個模擬開關CD4052和A/D轉換器AD574設計的數據采集卡,可以實現8路信號采集

2017-12-02 10:05:01 1126

1126

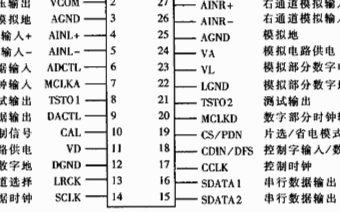

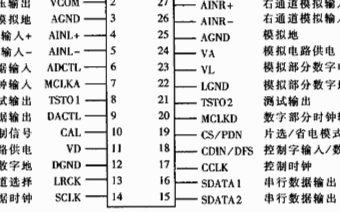

采樣,以減小采樣的相位差。數字信號處理器(DSP)采用TMS320F2812,實現對A/D轉換器AD73360的控制和讀取采樣數據,從而減少了邏輯控制電路。計算機接口電路采用RS232C和RS485標準串行口實現DSP與上位機之間的通信。

2018-06-15 11:20:00 5010

5010

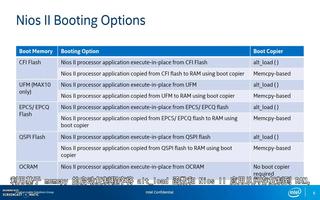

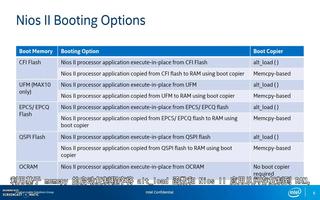

Nios II 處理器的各種啟動方法

2018-06-20 01:22:00 4338

4338

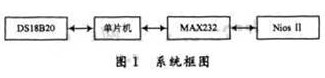

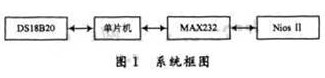

本設計是基于單片機和NiosⅡ軟核的溫度監控系統,其系統框圖如圖1所示。本系統采用Dallas單線數字溫度傳感器DS18B20采集溫度數據,打破了傳統的熱電阻、熱電偶再通過A/D轉換采集溫度的思路

2019-04-18 08:10:00 1995

1995

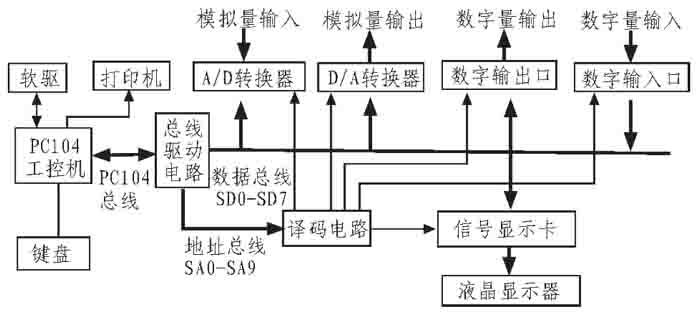

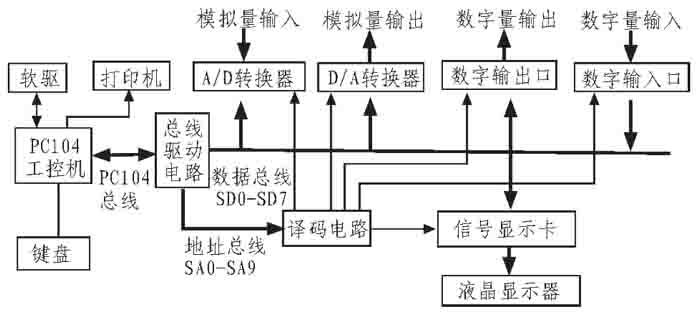

介紹了一個基于PC104 的數據采集與檢測電路的設計,它完成A/D 數據采集、D/A 數字/模擬轉換、數字量輸入/輸出、信號顯示卡以及LCD 顯示器的控制等功能。PC104 總線信號檢測電路對于改進

2018-09-03 08:44:00 8154

8154

本文檔的主要內容詳細介紹的是智能化控制系統PLC的數據采集技術詳細資料說明包括了:1. 數據采集系統基本結構,2. 測量放大電路,3. 模擬多路轉換器MUX,4. 采樣保持電路,5. A/D轉換器及其接口,6. 數據采集系統設計

2019-05-23 08:00:00 4

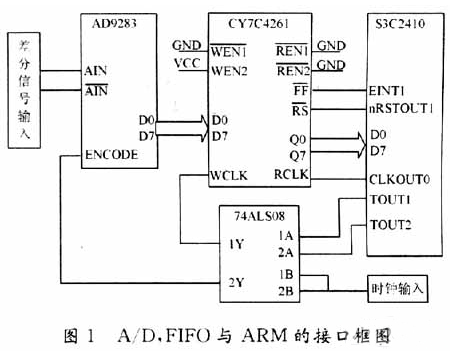

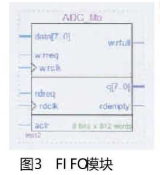

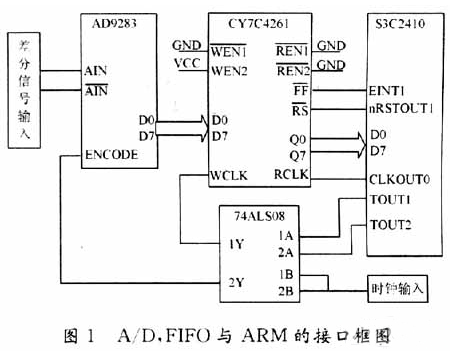

4 在高頻超聲波數據采集系統中,很多高速A/D轉換器往往不能直接與處理器相連接,這時就需要使用FIFO在處理器與A/D轉換器之間架一座橋梁,FIFO的先入先出特性可以方便緩存大量的數據塊。

2019-11-05 15:54:54 2965

2965

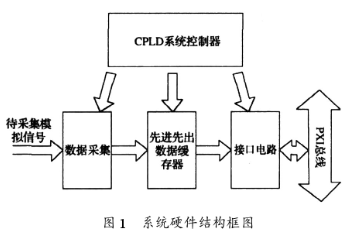

該數據采集系統的硬件結構框圖如圖1所示,該系統包括數據采集模塊、F先進先出數據緩存模塊、接口電路模塊和CPLD系統控制器模塊4個部分。待采樣的模擬信號經由數據采集模塊進行數據采集,采樣后經過轉換

2020-04-10 09:17:27 1516

1516

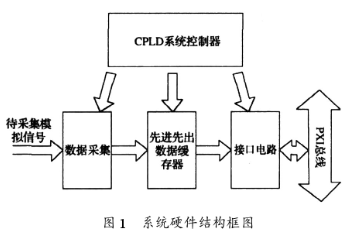

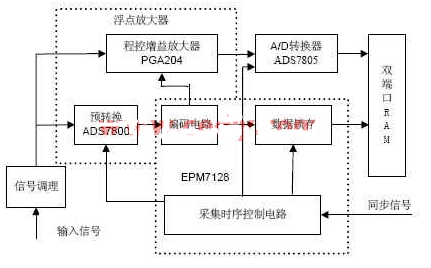

以往的數據采集系統多數采用單片機、DSP等微處理器產生A/D轉換芯片所需要的控制時序,以及通道轉換所需要的時序邏輯信號,這樣會占用CPU較多的時間。本文介紹基于CPLD的高速高精度數據采集系統

2020-07-31 17:23:48 1253

1253

數據采集系統是計算機測控系統中不可或缺的組成部分,是影響測控系統的精度等性能指標的關鍵因素之一。常用數據采集方案是以微處理器為核心控制多個通道的信號采集、預處理、存儲和傳輸,即用軟件實現數據的采集,這在一定程度上局限了數據采集的速度、效率及時序的精確控制。

2020-08-06 17:22:44 5270

5270

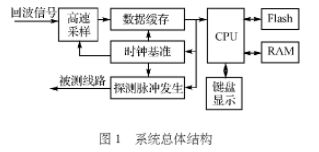

脈沖發生電路產生探測脈沖,高速的A/D轉換器對脈沖及其反射回波信號進行采樣,使用異步FIFO作為A/D采樣數據的緩存。軟核Nios作為系統核心,控制檢測任務的啟動和結束、脈沖發送接收模式的選擇、A

2020-08-24 15:46:53 1682

1682

基于FPGA+STM32雙處理器的高速數據采集系統

2021-06-25 10:38:04 81

81

電子發燒友App

電子發燒友App

評論