在FPGA開發板上都有幾種不同的存儲器,比如SDRAM,FLASH,EPCS,還有內部onchip memory,這幾種存儲器間是如何通信或者構建一個系統該如何搭配他們呢,不少人都問到這個問題。在這里我做個總結以方便初學者的學習。

首先看看在sopc builder中reset address

該如何搭配他們呢,不少人都問到這個問題。在這里我做個總結以方便初學者的學習。

首先看看在sopc builder中reset address和nios IDE中System Library中的program memory(.text)、read-only data memory(.rodata)等這幾個地址的關系和作用根據altera 的文檔解釋如下:

.text :代碼執行區

.rodata:只讀數據區,存放靜態全局變量

.rwdata:可讀寫數據區,存放可讀寫變量和指針變量

.bss:未初始化變量區

.text-the actual executable code

.rodata-where read only data used in the execution of the code

.rwdata-where read/write variables and pointers are stored

heap-where dynamically allocated memory is located

stack-where function call parameters and other temporary data

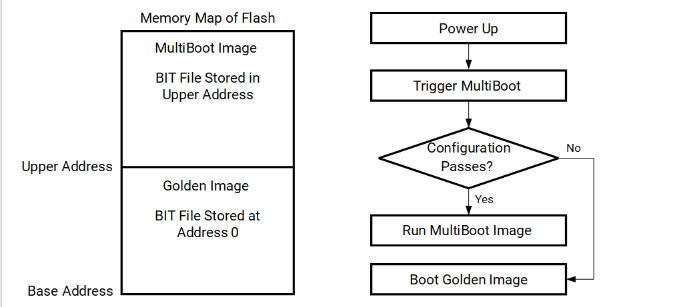

SOPC builder 在Nios II more "cpu_0" setting 標簽中的

reset address 決定了flash programmer 的下載存儲器(一般是選EPCS controller 或者CFI

flash),并且決定了程序從此處開始啟動。exception address 指定的是異常處理地址。當然,程序在運行前所有的數據都是存放在flash(EPCS 或者CFI FLASH)中如果你設計的系統resetaddress 與其它地址的設置不相同,比如reset address 和exceprion address,reset address和IDE 中的program memory(.text)設成不同的存儲器,那么系統從reset address 啟動時都會從flash 中把相關數據自動下載到相應的地址或者初始化相應地址。通過上面的認識,我們就比較清楚了各存儲器間可進行哪些搭配了,reset address 的選擇可選EPCS controllor 或者CFI flash;program memory(.text) 可選擇onchipmemory,SDRAM,CFI flash 等。如果reset address 為EPCS 則在使用flash progrrammer時程序是下載到EPCS 芯片中。如果reset address 選擇CFI flash,則flash progrrammer時程序是下載到CFI flash 芯片中。需要注意的是這里有個特殊情況。例如在開發板上經常有這么一個簡單的系統,CPU+

onchip memory+LED_PIO,reset address 選擇onchip memory;感覺整個系統都沒有用到flash。而且onchip memory 在系統斷電后數據就會消失,那么程序代碼是存在哪,系統如何從onchip memory 啟動聽呢?先來看看onchip memory 模塊的描述信息:在onchip_memory.v 中有這么一段the_altsyncram.init_file = "onchip_memory.hex",很明顯onchip memory 的初始數據來自"onchip_memory.hex",而"onchip_memory.hex"是在NiosIDE 的System Library 中存儲器有選擇onchip_memory( 至少有一項是選擇onchip_memory,如果都不選,就不會生成)時,在build 結束的時候生成的。于是當我們把System Library 中存儲器的選擇都選擇onchip_memory 時,在IDE 中build 結束后所有的程序代碼都生成在"onchip_memory.hex"中,再在QII 中全編譯一次時,系統通過onchip_memory.v 調用"onchip_memory.hex"從而把所有的程序代碼以及配制信息都生成在POF 和SOF 文件中,使用QII 的programmer 直接下載到EPCS 芯片或者FPGA 芯片內程序都會立即執行。因為這里的特殊性就有很多網友詢問了,reset address 選擇onchipmemory,而IDE 中把代碼區都選擇SDRAM 調試的時候程序正常運行,再在QII 全編譯后下載POF 文件就運行不了呢?問題就是出在這了,在這里可以總結出一點,要讓程序在onchip memory 之外的存儲器中運行,那么reset address 就必然選EPCS 或者CFI flash,并且要通過flash programmer 把程序下載到flash 中。

責任編輯:YYX

-

FPGA

+關注

關注

1660文章

22394瀏覽量

634941 -

存儲器

+關注

關注

39文章

7730瀏覽量

171506

發布評論請先 登錄

【ALINX 教程】FPGA Multiboot 功能實現——基于 ALINX Artix US+ AXAU25 開發板

【免費試用】正點原子STM32N647開發板免費試用

速通攻略 | RK3588開發板U-Boot階段的存儲設備文件讀取方法

基于FPGA開發板TSP的串口通信設計

RK3506開發板Linux開發板極致性價比之選

Pico2-ICE FPGA開發板的應用示例

Vivado無法選中開發板的常見原因及解決方法

ALINX AMD RFSoC射頻開發板選型指南

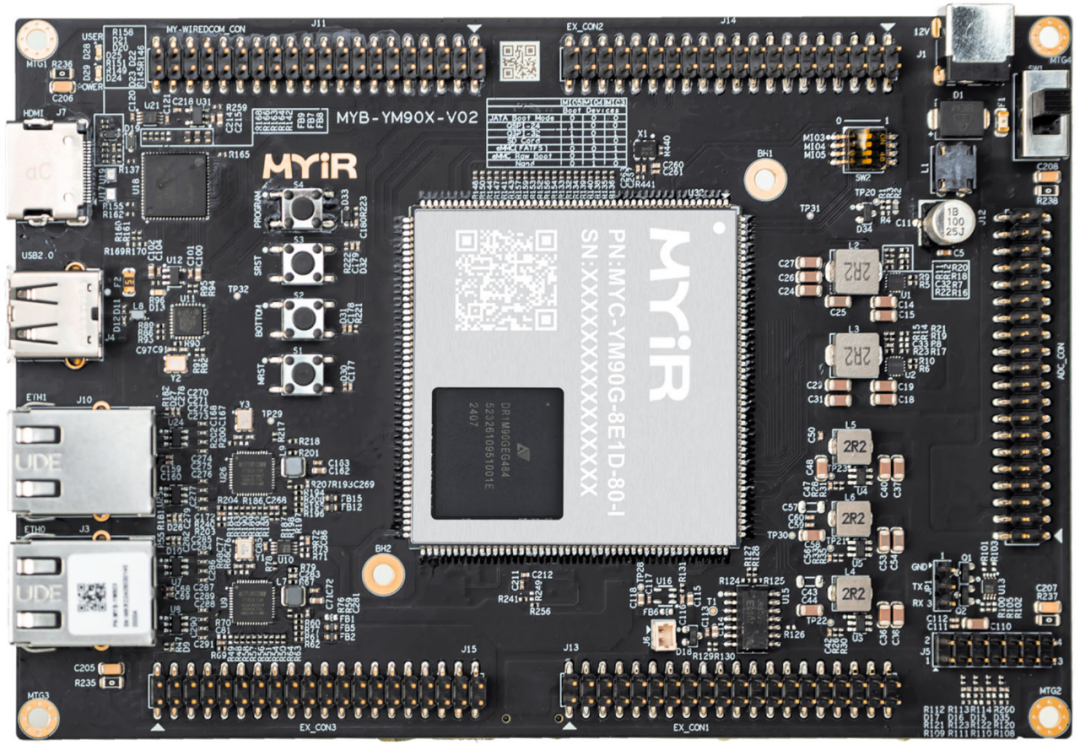

有ARM,NPU,FPGA三種核心的開發板 — 米爾安路飛龍派開發板

【干貨分享】:開源小巧的FPGA開發板——Icepi Zero

發布|CAE1200+FPGA開發板

FPGA開發板中幾種不同的存儲器

FPGA開發板中幾種不同的存儲器

評論