12月8日智譜AI發(fā)布并開源 GLM-4.6V 系列多模態(tài)大模型,沐曦股份曦云C系列GPU完成Day 0適配。

2025-12-17 14:28:41 381

381

信道活躍檢測(CAD)是一種無線喚醒技術(shù),這個(gè)功能一般是定時(shí)檢測么?還是一直檢測?

2025-12-10 06:53:53

近期,上海 AI 實(shí)驗(yàn)室 DeepLink 團(tuán)隊(duì)推出的 DLInfer 通過支持 LMDeploy 主流模型推理,助力沐曦股份曦云 C500 落地 MinerU 多模態(tài)數(shù)據(jù)生成場景,Graph 模式下實(shí)現(xiàn)性能加速 60%。

2025-12-09 14:55:14 557

557

LABVIEW 2023Q1調(diào)用python后一直報(bào)錯(cuò)1671報(bào)錯(cuò)信息:PythonNode_AddTwoDoubles.vi中的打開Python會話Python returned

2025-11-12 09:51:26

在lin系統(tǒng)中下載github一直報(bào)錯(cuò),顯示port443

2025-11-05 07:22:26

,并支持MetaXLink超節(jié)點(diǎn)擴(kuò)展技術(shù),在硬件性能和軟件兼容上完全滿足下一代生成式AI的訓(xùn)練和推理需求。 而且,沐曦股份與中國科學(xué)院合作的國產(chǎn)千卡集群,已完成多個(gè)大模型全參數(shù)訓(xùn)練,證實(shí)國產(chǎn)算力已具備大模型預(yù)訓(xùn)練能力。 公開資料顯示,沐曦股份于

2025-10-19 20:04:36 45478

45478 近日,DeepSeek宣布在其新版本中擁抱國產(chǎn)GPU語言TileLang,引發(fā)業(yè)界廣泛關(guān)注。作為國產(chǎn)高性能GPU的代表,沐曦曦云C系列產(chǎn)品已率先在這一新興開源社區(qū)獲得支持。TileLang項(xiàng)目是由

2025-10-14 09:25:25 919

919

stm32f103zet6芯片,根據(jù)官方配置的pwm一直沒有輸出,求各位大佬指點(diǎn)一下

2025-10-10 07:07:32

STM32H743IIT6使用QBOOT一直重啟

2025-09-19 07:06:40

近日,在EmTech China 2025全球新興科技峰會上,曦智科技憑借領(lǐng)先的光電混合算力技術(shù),再度榮登“50家聰明公司”(TR50)榜單!這也是自2019年以來,曦智科技第四次獲此殊榮~掌聲響起來!

2025-09-16 14:25:50 527

527

我上面的代碼中如果加入rt_thread_delay就一直卡在rt_thread_idle_entry空閑線程,如果去掉rt_thread_delay就能正常打印,請問這是怎么回事。我的RT_TICK_PER_SECOND設(shè)置為1000,rt_thread_delay(1)應(yīng)該只有1ms啊

2025-09-12 08:13:09

近日,全球領(lǐng)先的光電混合算力提供商曦智科技宣布完成規(guī)模超15億元人民幣的C輪融資。本輪融資吸引了中國移動、上海國投、國新基金、浦東創(chuàng)投等知名投資機(jī)構(gòu)參與,老股東中科創(chuàng)星、沂景資本、某領(lǐng)先互聯(lián)網(wǎng)廠商等

2025-09-05 15:44:44 696

696 一直徘徊在高速電路設(shè)計(jì)的門口遲遲無法真正進(jìn)入,希望能借此書真正翱翔于高速電路設(shè)計(jì)的領(lǐng)域

2025-08-21 08:31:43

一直為低電平

按照“Detailed LVDS transaction diagram”中的流程,在完成“PHY and LINK training”后,BUFFER_RDY信號應(yīng)該從低電平拉升

2025-08-14 06:21:46

在CanMv連接k230時(shí)一直報(bào)錯(cuò)顯示獲取固件版本時(shí)出現(xiàn)超時(shí)錯(cuò)誤

2025-07-30 06:38:43

天網(wǎng)絡(luò)”)運(yùn)營的沐曦曦云C550 三千卡通用 GPU 國產(chǎn)集群。此次合作標(biāo)志著硅基流動正式將該國產(chǎn)集群納入算力網(wǎng)絡(luò),進(jìn)一步為大模型產(chǎn)業(yè)落地提供充沛的高性能國產(chǎn)算力。

2025-07-23 17:33:58 1668

1668 使用L9305驅(qū)動4路閥,但是一直無法和芯片正常通信,確認(rèn)硬件無問題。有無相關(guān)庫和相應(yīng)文檔,謝謝謝謝

2025-07-23 06:41:10

BLUE DFU APP選擇要升級的bin文件,連接上設(shè)備后,在升級頁面卡在PROGRAMMING,下載進(jìn)度一直顯示0。

2025-07-18 08:20:19

在while中一直使用HAL_SPI_TransmitReceive_DMA發(fā)送接收數(shù)據(jù),循環(huán)幾次后就會一直為HAL_BUSY狀態(tài),查看SPI狀態(tài)結(jié)構(gòu)體可看到State始終為

2025-07-18 06:38:29

我這運(yùn)行kmodel模型驗(yàn)證一直報(bào)錯(cuò),所以沒法做kmodel模型好壞驗(yàn)證,不知道怎么解決這個(gè)問題,重新訓(xùn)練一個(gè)kmodel模型會和拿相同pt訓(xùn)練的模型效果不一樣嗎?在線云訓(xùn)練效果會好嗎?

或者大佬能不能說是我給您發(fā)pt、onnx、kmodel模型您幫幫驗(yàn)證一下好嗎?

2025-06-10 08:02:30

當(dāng)前,PaddleScience已與沐曦展開深度合作,涵蓋智能仿真、高性能計(jì)算、科學(xué)建模等多個(gè)方向。這一趨勢正加速形成面向"Al for Science"的國產(chǎn)智算生態(tài)新格局。

2025-05-06 14:49:43 1459

1459 我們做了兩款設(shè)備,一款USBA的輸出為3.0,另外一款電路只改了連接器TYPEC,一直顯示2.1,同樣的固件,拆掉type-C的連接器電線連接USBA連接器還是不能顯示3.0,ESD也是連接的,請問誰遇到過

2025-04-29 18:47:39

AD7606

這是我的原理圖,輸出的busy一直為高

2025-04-24 07:55:36

DS1232LPS-2+T&R,這款芯片在什么情況下,5腳RST會一直輸出高電平?(正常時(shí)序是上電有個(gè)400多ms的高電平后,一直處于低電平,如果7腳沒有及時(shí)喂狗,會觸發(fā)復(fù)位,也就是重復(fù)400多ms的高電平后,一直處于低電平)

2025-04-18 07:51:16

ADI9002校準(zhǔn)通過后給校準(zhǔn)信號后一直校準(zhǔn),無法正常工作

2025-04-18 07:13:29

英國倫敦時(shí)間4月9日,全球頂級學(xué)術(shù)期刊《自然》(Nature)刊載了曦智科技的光電混合計(jì)算成果:《超低延遲大規(guī)模集成光子加速器》(An integrated large-scale photonic

2025-04-10 09:50:28 1330

1330

這是設(shè)計(jì)的原理圖,做出PCB以后,輸入給15V直流電,但是一直給不上。會觸發(fā)電源的保護(hù)。

查了資料發(fā)現(xiàn)該芯片的最大輸入電流不能超過1A。然后嘗試在二極管后面串聯(lián)15歐姆電阻。發(fā)現(xiàn)仍然無法穩(wěn)壓。同樣

2025-04-03 13:35:01

近日,沐曦曦云C500通用計(jì)算GPU與百度飛槳已完成Ⅱ級兼容性測試。測試結(jié)果顯示,雙方兼容性表現(xiàn)良好,整體運(yùn)行穩(wěn)定。這是沐曦加入飛槳“硬件生態(tài)共創(chuàng)計(jì)劃”后的階段性成果。

2025-03-31 14:22:39 1594

1594 2025年3月25日,曦智科技正式發(fā)布全新光電混合計(jì)算卡“曦智天樞”。曦智科技創(chuàng)始人兼首席執(zhí)行官沈亦晨博士在發(fā)布現(xiàn)場表示:“曦智天樞首次實(shí)現(xiàn)了光電混合計(jì)算在復(fù)雜商業(yè)化模型中的應(yīng)用,是曦智科技光電混合

2025-03-25 15:43:21 521

521

近日,基于開源KTransformers架構(gòu)的 CPU/GPU 異構(gòu)推理能力,沐曦在曦云C500單卡GPU上成功實(shí)現(xiàn)DeepSeek-R1-671B滿血版單并發(fā)解碼吞吐16.5 tokens/s的優(yōu)異成績,相比社區(qū)官方數(shù)據(jù)提升20%以上。

2025-03-20 15:52:39 2015

2015 目前定時(shí)器2配置中斷,程序一直死循環(huán),無法進(jìn)入中斷,有無大佬請教或者看一下個(gè)參考?xì)v程

2025-03-12 08:18:39

由stm32cubemx按照配置重新生成工程,bsp_SysTick.c一直沒有呢

2025-03-10 07:44:48

我用的是STM32H7讀取MKI-165V1的開發(fā)板的大氣壓的值,我設(shè)置輸出頻率為1,STM32間隔1s讀取一次大氣壓數(shù)據(jù),未使用FIFO,得到的IIC大氣壓數(shù)據(jù)一直在減少,在一個(gè)小時(shí)內(nèi),數(shù)據(jù)從1014.117一直減小到1002.970,怎么樣能讓數(shù)據(jù)輸出的穩(wěn)定一些

2025-03-10 07:00:26

在看到大佬們的帖子之后,自己也嘗試將hummingbird v2移植到賽靈思的板卡上,但是在IDE里一直報(bào)錯(cuò)

一開始用的是Sipeed的調(diào)試器,后來買了芯來家的,都是同樣的問題

板卡的連線如圖,使用芯來調(diào)試器時(shí)候,店家說殼子套反了

XDC中的約束為

搗鼓了好幾天,有沒有大佬救救我

2025-03-07 09:50:14

我正在嘗試使用S2-LP芯片的LDC模式,但是芯片一直無法正常工作

對于TX端,芯片只能進(jìn)行一次TX操作,之后就會一直進(jìn)入sleep模式,我向TX FIFO 中寫入數(shù)據(jù),但是

2025-03-07 08:10:21

這個(gè)代碼一直顯示輸入?yún)?shù)不足,這個(gè)函數(shù)在之前調(diào)用時(shí)一直可以,這次調(diào)用時(shí)就不行,想請問一下這是什么原因?

2025-03-02 11:15:40

云硬盤一直處于“deleting”狀態(tài)可能是由于多種原因?qū)е碌模缇W(wǎng)絡(luò)問題、系統(tǒng)故障、掛載狀態(tài)異常或后臺任務(wù)未完成等。以下是一些解決方法: 1、等待刪除過程完成 通常情況下,云硬盤的刪除需要一

2025-02-24 20:08:15 938

938 蝦哥小智Ai對話項(xiàng)目固件編譯演示

2025-02-24 12:21:55 9554

9554

大家好,在使用DLPC410的時(shí)候我遇到了一個(gè)問題,我用CHIPSCOPE抓取INIT_ACTIVE信號時(shí)會一直為1,關(guān)于ARST的聲明我是參考了參考代碼的寫法,有人知道這個(gè)問題該如何解決嗎?煩請指點(diǎn)一二。

2025-02-24 07:45:57

我正在使用一款DLPC3430+DLP2000+DLP2010的顯示模組,但一直顯示條紋圖案(如圖),并且用示波器測量確認(rèn)輸入的DSI信號和輸出的LVDS信號都是有的。我想請問一下這個(gè)條紋idle

2025-02-21 16:41:15

我在燒錄DLP4500 FIRMWARE的過程中一直不成功,總是在最后一步停止不動,顯示download completed in xxxxxx,但進(jìn)度一直是0%不動,如圖,請問這個(gè)問題如何解決?

2025-02-21 07:57:42

我制作了一個(gè)13Mb的固件但是他燒錄不進(jìn)去,一直卡在61%,然后開始無響應(yīng)。

2025-02-20 08:08:04

CYPRESS_I2C_ReadI2C一直失敗。

1----我將samples的.c代碼添加到Qt中的cpp調(diào)用。 如圖1

圖1

2----調(diào)用寫命令CYPRESS_I2C_WriteI2C 會成

2025-02-20 08:04:09

在更新固件時(shí)突然斷電,接上電之后就出現(xiàn)Connect;Powered Off。再次對固件進(jìn)行更新時(shí),一直處于Erasing flash data。

2025-02-19 06:44:04

你好,updata firmware 一直失敗,請問是什么原因?

2025-02-19 06:28:46

卻給出了一個(gè)令人震驚的答案:僅需 817 條精心設(shè)計(jì)的樣本,就能讓模型在數(shù)學(xué)競賽級別的題目上超越當(dāng)前許多最先進(jìn)模型。這一發(fā)現(xiàn)不僅挑戰(zhàn)了傳統(tǒng)認(rèn)知,更揭示了一個(gè)可能被我們忽視的事實(shí):大模型的數(shù)學(xué)能力或許一直都在,關(guān)鍵在于如何喚

2025-02-17 17:44:24 1003

1003

在ADS1278上電后,SCLK沒給波型(一直是高電平),為什么DOUT會一直出來波形?很不解。不是說DOUT只在SCLK有波形輸入的時(shí)候才會輸出波的嗎

2025-02-14 06:22:28

1.75V的方波時(shí),測得AINN2是幅值為0.87v左右的方波,AINP2是與AINN2反相,幅值為0.87v左右的方波,但是后來發(fā)現(xiàn)芯片好像被燒掉了,即Reday輸出一直為高。您覺得有沒有可能是輸入

2025-02-14 06:21:28

ADS1118一直循環(huán)寫寄存器spi,為什么讀到的數(shù)據(jù)是脈沖信號

如果只初始化寄存器一次的話,就一直高電平

2025-02-13 07:45:05

您好,我使用的同步FIFO SN74V293,但是它的/EF引腳標(biāo)志位一直為低,復(fù)位對其也沒有影響。FIFO工作在Standard模式下(即FWFT引腳接地),/LD引腳一直為高,/SEN引腳一直

2025-02-12 08:30:49

不知道什么原因,外擴(kuò)AD芯片一直燒TMS320F28335芯片。

想問下,IOVDD接3.3v電壓,out的輸出口不接50歐姆電阻(實(shí)際電路板都沒接50歐電阻),其輸出電壓以及電流會不會超過TMS320F28335的I/O電壓電流要求。將DSP芯片燒壞

2025-02-12 07:47:42

使用ADS1248時(shí),硬件如下圖,ADS1248_REG_MUX1配置為0x30,但VREFOUT引腳一直沒有輸出,請問可能是什么原因

2025-02-12 07:28:59

首先感謝JHL老師的前期指導(dǎo)。現(xiàn)在我的程序能夠正確讀出1298的狀態(tài)。我有幾個(gè)問題,

1、當(dāng)引腳懸空時(shí)輸出一直為7fffff(8388607),對嗎,為什么?

2,、測試信號寄存器config2

2025-02-12 06:43:29

初次接觸這種外界的DAC模塊,DAC7573的數(shù)據(jù)手冊關(guān)于LDAC的講解看的不太明白,麻煩哪位用過的大神給小弟說明一下。

DAC7573一直沒輸出,在研究是否是這個(gè)的問題。

2025-02-11 07:33:25

的數(shù)值,是由于D11一直為1導(dǎo)致的。我想咨詢一下,這個(gè)的話,可能是由什么問題導(dǎo)致的?是AD芯片的問題還是我板子的問題?謝謝了。

2025-02-11 07:27:03

您好!在使用DM6437控制ADS8568采樣的時(shí)候,數(shù)據(jù)一直不對,希望能找到能控制ADS8568采樣的示例程序,用別的單片機(jī)什么的也行,只是想看看控制ADS8568采樣的思路,以便找出錯(cuò)誤,謝謝!

2025-02-11 07:19:27

ADS1232的輸出AD值隨著時(shí)間會一直慢慢的持續(xù)遞減

2025-02-11 06:32:38

ADS1298 做測試時(shí),完全按照數(shù)據(jù)手冊設(shè)置,config1 0x86; config2 0x10; config3 0xC0; CHnSET 0x05; RDATAC mode.但是DRDY一直是低,有讀取時(shí)鐘,且讀取時(shí)DIN一直為 logic \'0\'. 求前輩幫忙,大神解釋啊

2025-02-08 09:00:08

我們公司用ADS1242芯片,現(xiàn)在做了一個(gè)實(shí)驗(yàn)板,ADS1242芯片5V供電,參考電壓是2.5V,遇到一個(gè)問題,AD輸出值一直是65535,不會變,不知道是怎么回事,請大家?guī)兔χ笇?dǎo)一下!!!

2025-02-07 08:30:53

芯片上電后,保證復(fù)位時(shí)序,給1246的START 腳輸入高電平,然后一直發(fā)送時(shí)鐘(cs為低),DRDY上一直為低電平,根本沒有變化,請TI工程師多多指教!

2025-02-07 07:33:41

參照ADS1293 PDF資料Figure 34. 8-12-Lead ECG Application 原理和寄存器設(shè)置,設(shè)置寄存器讀寫沒有問題,但啟動ADC轉(zhuǎn)換后,DRDYB管腳一直為高電平

2025-02-06 08:15:50

ADS1255電路是這樣設(shè)計(jì)的,AIN0輸入正電壓時(shí),AIN1接GND。但是AIN0是設(shè)計(jì)可以檢測0-5v的,但是不知道什么原因就是一直輸出FFFFFFh,不知道如何排查軟件問題,還是硬件問題。請TI工程師指點(diǎn)迷津,謝謝!

2025-02-06 07:55:48

我是用DSP28335外部接口與DAC7724通信,DA芯片的引腳除了數(shù)據(jù)載入LDAC和復(fù)位用普通IO口控制外,其余都和DSP28335外部接口的相應(yīng)引腳相連,程序測試一直不對,輸出的值一直是-10V,而且我只是讓通道A輸出,可是其他的3個(gè)通道也是-10V ,這個(gè)是怎么回事?

2025-02-06 07:54:22

引腳還是一直是高電平。通過DIN和sclk輸入數(shù)據(jù)時(shí),DRDY輸出高電平脈沖。DOUT有數(shù)據(jù)。ADS1274壞了嗎?

2025-02-06 07:07:12

低電平,RESET腳始終為高電平,但不論連續(xù)還是單次DRDY腳用示波器看基本都一直為高電平,沒有負(fù)跳變。求解。

寄存器配置如下:

IDC0 0x00

MUX1 0x00

MUX00x01

SYS0 0x08

2025-02-06 06:18:05

請問一下,SPI的時(shí)鐘是一直有,還是只是在發(fā)送數(shù)據(jù)的時(shí)候自動產(chǎn)生?為什么我不能把命令寫進(jìn)ADS1258的寄存器呢?請問一下有可能是哪方面的原因呢?

2025-02-05 08:28:52

我用FPGA控制ADS1248。

ads1248編程思路如下:

FPGA產(chǎn)生時(shí)鐘給SCLK引腳,并且電路板上電后,一直給它時(shí)鐘;CLK雖和FPGA相連,但沒進(jìn)行數(shù)據(jù)處理;TESET、START引腳

2025-02-05 08:20:55

手冊上說DRDY在START=1命令發(fā)出后且AD轉(zhuǎn)換結(jié)束之后會變?yōu)椋埃⑦^一段時(shí)間之后會自動變?yōu)椋保易鰧?shí)驗(yàn)的時(shí)候,轉(zhuǎn)換結(jié)束之后一直是0,不會變?yōu)椋保瑢?shí)在想不明白是哪里出的問題。

另:在START=1命令發(fā)出之前,DADY一直是1.

2025-02-05 06:13:36

移動電源(充電寶)的燈一直亮可能有多種原因,以下是一些可能的原因及相應(yīng)的解決方法:

2025-01-27 16:27:00 7744

7744 Byte之后,讀取ADS7844 Dout,一直為0,示波器抓取波形也顯示如此,為什么?

3.寫control Byte的時(shí)候,量測AD1電壓為0.131V(實(shí)際DA TLV5610輸出),一直

2025-01-24 08:00:08

最近在調(diào)ADS1248 讀取K型熱電偶的板子 寄存器都能配置, 就是讀取的AD值一直在調(diào) 而且調(diào)的范圍很大 不知道什么原因?還有 如何把AD值轉(zhuǎn)換成溫度值 有沒有什么計(jì)算公式啊?

2025-01-24 07:45:04

最近在使用ADS1230做一個(gè)壓力控制設(shè)備,精度要求不高,但在測試的時(shí)候發(fā)現(xiàn)一直能不斷DOUT的下降沿信號,連上MCU后DOUT一直是高電平。這個(gè)的版圖,設(shè)計(jì)的時(shí)候忘了把REFP和REFN接上電源

2025-01-23 07:09:47

我使用ADS1178電路圖如下圖所示,采用SPI模式,ADC_CLK為25MHz,由CPLD產(chǎn)生SYNC,脈沖寬度為120ns,測試DRDY管腳一直為高電平,這是什么原因呢?

2025-01-23 06:54:28

最近買了一塊4490血氧評估板,上位機(jī)軟件一直報(bào)錯(cuò),大致意思是沒有數(shù)據(jù)返回,沒AD值,是配置問題,還是板子硬件有問題?

2025-01-22 08:32:36

我首先對ads1248全部進(jìn)行復(fù)位,然后安裝復(fù)位的設(shè)置,通過AIN0為positiveAIN1為negative進(jìn)行輸入,,然后等待DRDY變低,然后進(jìn)行讀數(shù)據(jù),,但是結(jié)果一直都是0,,都調(diào)了好長時(shí)間了,,求指導(dǎo)...好人一生平安

2025-01-22 07:37:33

請問一下,我的ADS7886讀數(shù)一直為0,連線如上,剛開始加了上拉電阻后來去掉了。代碼如下

unsigned int get_data()

{

unsigned char i,dat

2025-01-22 06:35:19

近日,澎峰科技與沐曦科技宣布,雙方已完成對PerfXLM推理引擎、PerfXCloud大模型服務(wù)平臺與沐曦曦云系列通用計(jì)算GPU的聯(lián)合測試。這一合作標(biāo)志著澎峰科技的核心軟件產(chǎn)品與沐曦科技的GPU產(chǎn)品

2025-01-21 15:20:17 1028

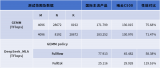

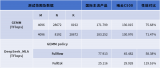

1028 ?近期,澎峰科技與沐曦完成了對PerfXLM(推理引擎)、PerfXCloud(大模型服務(wù)平臺)與沐曦的曦云系列通用計(jì)算GPU的聯(lián)合測試,測試結(jié)果表明PerfXLM、PerfXCloud軟件與沐曦GPU產(chǎn)品實(shí)現(xiàn)了全面兼容。

2025-01-21 09:51:47 1299

1299

電路輸出電壓一直不對,要么一直輸出電源電壓,要么輸出一些奇怪的電壓值。

寫入時(shí)序是這樣:開始、寫入0x98、寫入0x10、寫入數(shù)據(jù)高位、寫入數(shù)據(jù)低位、停止

2025-01-17 08:31:32

在使用FPGA驅(qū)ADS805的時(shí)候,根據(jù)手冊上的時(shí)序要求。數(shù)據(jù)滯后6個(gè)時(shí)鐘,那我采一個(gè)固定的電壓3.3v,因該得到的值是固定的才對。但是實(shí)際得到的如下:

,數(shù)據(jù)一直變化沒有規(guī)律。不知道是什么問題?

還是向手冊上說的,,可能用3.3v來驅(qū)使有問題的?

2025-01-17 06:48:47

74HC573上電以后,OE=0,LE=1,,輸入pin懸空,輸出一直為低是為什么?輸入端需要接上拉電阻嗎?

2025-01-16 07:47:09

AMC7823模塊一直不返回?cái)?shù)據(jù),PDF里時(shí)序也比較簡單,發(fā)送0x8000就有數(shù)據(jù) 但是我這邊的數(shù)據(jù)一直都是7f80且AD模塊沒反應(yīng)

2025-01-16 06:03:15

AFE5805的輸出時(shí)鐘LCLK、FCLK為什么一直沒有波形輸出呢?在不進(jìn)行數(shù)據(jù)配置的情況下,有沒有一個(gè)很簡單的測試方式啊,比如一上電,給個(gè)復(fù)位,可以測試哪些信號

2025-01-14 08:10:57

我安裝了ADS1298ECG-FE的軟件平臺,打開后一直出現(xiàn)unable to find a version of the runtime to run this application這個(gè)錯(cuò)誤

2025-01-14 06:13:52

請問大家有沒有用試過用ADS1234 的時(shí)候DOUT一直為高電平,無論DVDD設(shè)置5V還是3.3V, DOUT一直輸出是3.3V,

PDWN腳是通過MCU控制,MCU是C8051F系列的。

在線等待回復(fù),萬分感謝。

2025-01-13 08:21:40

Din輸入0x97,,VCC為3.3V,Vref為1V,當(dāng)采0.5V直流電壓時(shí),Dout引腳MSB輸出不為1,當(dāng)采1.5v直流量時(shí),Dout引腳MSB為1,輸出完全不正常,而且一直變動不穩(wěn)定,不知道為什么?

2025-01-13 08:04:03

根據(jù)數(shù)據(jù)手冊,ADS7841的BUSY應(yīng)該在控制字節(jié)的最后一個(gè)脈沖的下降沿的時(shí)候拉高,但是實(shí)際不是這樣

實(shí)際的波形是這樣的,正常嗎?

AD轉(zhuǎn)換的結(jié)果也不對。

這個(gè)AD芯片工作的時(shí)候是不是一直要給脈沖才能工作?

謝謝。

2025-01-10 08:13:27

使用ADS1115的時(shí)候出現(xiàn)個(gè)問題。配置完成后,讀取配置寄存器的值是正確的,可是讀取數(shù)據(jù)卻一直為0,而且在發(fā)出讀取數(shù)據(jù)命令后,循環(huán)檢查 ALERT/RDY的引腳,發(fā)現(xiàn)一直為高。

請幫忙看看可能是哪方面的原因,謝謝!

2025-01-10 06:24:51

位數(shù)據(jù),連續(xù)3次就可以讀取到24位,

CLK:25MHZ

讀取數(shù)據(jù)時(shí)將SYNC置為低電平,延時(shí)10ms然后開始讀取數(shù)據(jù),讀取完畢后再置為高電平。

但是我讀取出來的數(shù)據(jù)一直為0,輸入端的電壓有1.1V

2025-01-09 08:21:17

最近一個(gè)周用FPGA寫一個(gè)讀取一個(gè)ADS1271數(shù)據(jù)的程序。按照芯片手冊上的初始化的理解,我先將SYNC_N用引腳拉低500個(gè)時(shí)鐘周期,然后再將其拉高。可是DRDY_N一直是高電平,未能使能輸出數(shù)據(jù)。請問這是由于初始化的脈沖寬度小了么?還是根本就是我的理解有錯(cuò)誤。

2025-01-09 07:36:48

在使用ADS1256采集電壓時(shí),無論是使用單端采集還是差分采集(測試輸入電壓都為負(fù)值),在輸出端DOUT采集到的24位數(shù)據(jù)在最高位都無法變?yōu)?一直為0,所以采集得到的數(shù)據(jù)都是正的;如圖中我采集

2025-01-09 06:11:16

我用的是ads1256evm開發(fā)板,3腳接5V ,9腳3.3V,reset,CS用IO引腳控制的,上電以后,drdy一直是高的,

ADS_CS_LOW();

RESET_HIGH

2025-01-08 06:06:25

電子發(fā)燒友App

電子發(fā)燒友App

評論