芯源MCU采用的是什么內(nèi)核?

2025-12-22 07:11:06

和文件要求在vivado2019.2上嚴(yán)格正確執(zhí)行,要求無(wú)報(bào)錯(cuò)。

能解決的大神請(qǐng)加QQ 2257993511,希望這兩天解決。

2025-12-19 23:17:52

前言:做Linux驅(qū)動(dòng)開(kāi)發(fā)或內(nèi)核調(diào)試的朋友,一定對(duì)printk不陌生,但你真的會(huì)用它嗎?為什么同樣是調(diào)試RK3588內(nèi)核,別人能精準(zhǔn)捕捉關(guān)鍵錯(cuò)誤,你卻被海量日志淹沒(méi)?今天就帶大家吃透printk

2025-12-19 08:32:48 654

654

當(dāng) CPU 遇到嚴(yán)重異常(如讀取到的指令無(wú)效、訪問(wèn) FLASH 時(shí)位寬和目標(biāo)地址不匹配),會(huì)將 PC 指針停在當(dāng)前地址處鎖定,并產(chǎn)生內(nèi)核 LOCKUP 故障復(fù)位信號(hào)。

芯片上電后,LOCKUP 復(fù)位

2025-12-15 08:33:25

CW32L052是基于什么內(nèi)核的芯片?

2025-12-15 06:02:41

AMD Vivado Design Suite 2025.2 版本現(xiàn)已發(fā)布,新增對(duì) AMD Versal 自適應(yīng) SoC 的設(shè)計(jì)支持,包含新器件支持、QoR 功能及易用性增強(qiáng)。

2025-12-09 15:11:32 722

722 以ARM為例:

ARM-cortex-M3/4的單片機(jī)(比如STM32 等):該類單片機(jī)的代碼在nor flash中,cortex內(nèi)核可以直接運(yùn)行,不需要將代碼加載到ram中運(yùn)行

2025-12-04 08:06:56

變頻電機(jī)的恒轉(zhuǎn)矩運(yùn)行與恒功率運(yùn)行是工業(yè)驅(qū)動(dòng)領(lǐng)域的兩大核心控制模式,其特性直接影響設(shè)備性能與能耗效率。以下從原理、應(yīng)用及技術(shù)實(shí)現(xiàn)層面展開(kāi)分析: 一、恒轉(zhuǎn)矩運(yùn)行模式的技術(shù)本質(zhì) 1. 電磁轉(zhuǎn)矩恒定

2025-12-04 07:39:57 393

393

內(nèi)核模塊是什么?

內(nèi)核模塊是動(dòng)態(tài)加載到內(nèi)核中的代碼,可以在不重啟系統(tǒng)的情況下擴(kuò)展功能,比如設(shè)備驅(qū)動(dòng)或者文件系統(tǒng)支持。這樣用戶不需要把所有功能都編譯進(jìn)內(nèi)核,節(jié)省了資源,提高了靈活性。

模塊的文件格式

2025-11-25 06:59:27

,它是一個(gè)向上的計(jì)數(shù)器,記錄的是內(nèi)核時(shí)鐘運(yùn)行的個(gè)數(shù),內(nèi)核時(shí)鐘跳動(dòng)一次,該計(jì)數(shù)器就加1,精度非常高,決定內(nèi)核的頻率是多少,如果是F103系列,內(nèi)核時(shí)鐘是72M,那精度就是1/72M = 14ns,而程序

2025-11-21 07:51:59

開(kāi)源鴻蒙技術(shù)大會(huì)2025 OS內(nèi)核與視窗分論壇在湖南長(zhǎng)沙國(guó)際會(huì)議中心圓滿舉行。來(lái)自西北工業(yè)大學(xué)、浙江大學(xué)、廈門大學(xué)、華為等高校和企業(yè)的學(xué)者專家齊聚一堂,圍繞鴻蒙內(nèi)核通信機(jī)制、智能渲染、內(nèi)存緩存優(yōu)化、端云協(xié)同備份及空間視窗架構(gòu)等前沿方向,分享最新研究成果與實(shí)踐經(jīng)驗(yàn)。

2025-11-20 17:29:16 657

657

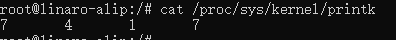

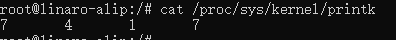

一、開(kāi)篇:一個(gè)命令引出的核心問(wèn)題 在?Linux?終端執(zhí)行?cat /proc/sys/kernel/printk,你可能會(huì)看到這樣的輸出: 這串?dāng)?shù)字不是隨機(jī)的,而是內(nèi)核日志系統(tǒng)的“核心配置開(kāi)關(guān)

2025-11-20 15:54:56 1433

1433

Hi 各位,我在嘗試使用Vivado 2018.2編譯E203的mcs文件,遇到如下兩個(gè)問(wèn)題:

1. 按照書(shū)中步驟運(yùn)行,執(zhí)行完make mcs之后得到的mcs文件與git中預(yù)編譯出來(lái)的mcs文件有

2025-11-11 06:04:55

vivado中,怎么將e203內(nèi)核源代碼封裝成ip核,并添加總線?

2025-11-10 07:22:49

在linux中,將程序的運(yùn)行空間分為內(nèi)核空間與用戶空間(內(nèi)核態(tài)和用戶態(tài)),在邏輯上它們之間是相互隔離的,因此用戶程序不能訪問(wèn)內(nèi)核數(shù)據(jù),也無(wú)法使用內(nèi)核函數(shù)。當(dāng)用戶進(jìn)程必須訪問(wèn)內(nèi)核或使用某個(gè)內(nèi)核函數(shù)時(shí),就得使用系統(tǒng)調(diào)用(System Call)。在Linux中,系統(tǒng)調(diào)用是用戶空間訪問(wèn)內(nèi)核空間的唯一途徑。

2025-11-08 12:42:20 645

645 前提條件:

1)開(kāi)發(fā)板是Digilent的ARTY A7-35T開(kāi)發(fā)版,也就是《手把手教你設(shè)計(jì)CPU-RISC-V處理器》中介紹的那塊板子

2)vivado安裝正常,可以啟動(dòng),跑make mcs

2025-11-07 06:05:07

本文利用NucleiStudio IDE 和 vivado 對(duì) NICE demo協(xié)處理器進(jìn)行軟硬件聯(lián)合仿真。

1. 下載demo_nice例程:https://github.com

2025-11-05 13:56:02

購(gòu)買了HummingBird Evaluation kit,按照書(shū)本的指示,

(1)連接FPGA JTAG

(2)連接電源,并上電

(3)打開(kāi)vivado,并進(jìn)入Hardware manager,發(fā)現(xiàn)沒(méi)有找到HummingBird Evaluation kit

可能的原因是什么?多謝!

2025-11-05 07:11:49

在qemu上體驗(yàn)芯來(lái)RISC-V處理器運(yùn)行鴻蒙LiteOS-M內(nèi)核

1.本文概述

2.下載qemu

3.下載鴻蒙LiteOS-M

4.運(yùn)行與測(cè)試

5.gdb調(diào)試

1.本文概述

由于前幾天

2025-10-31 09:04:54

一、隊(duì)伍介紹

本篇為蜂鳥(niǎo)E203系列分享第一篇。本篇介紹的內(nèi)容是Hbirdv2在vivado2018.3上的仿真工作。

二、前言

仿真前,我們首先需要獲得仿真需要的.verilog文件,我們

2025-10-31 08:43:38

;Run Behavioral Simulation之后,會(huì)出現(xiàn)如下圖界面,此時(shí),在Tcl Console中并沒(méi)有出現(xiàn)仿真結(jié)果。

沒(méi)有出現(xiàn)仿真結(jié)果的原因是沒(méi)有給Vivado時(shí)間進(jìn)行仿真,解決方法

2025-10-31 06:24:20

分享一代E203的vivado調(diào)試方法(windows/linux皆可)。比賽小隊(duì)名:強(qiáng)強(qiáng)聯(lián)合隊(duì)。報(bào)名編號(hào):CICC1316

1.新建vivado項(xiàng)目

此處注意勾選Do not specify

2025-10-31 06:14:34

vivado綜合后時(shí)序?yàn)槔饕怯袃煞N原因?qū)е拢?1,太多的邏輯級(jí)

2,太高的扇出

分析時(shí)序違例的具體位置以及原因可以使用一些tcl命令方便快速得到路徑信息

2025-10-30 06:58:47

在Windows操作系統(tǒng)下使用vivado將設(shè)計(jì)的電路燒寫(xiě)到MCU200T開(kāi)發(fā)板上的FLASH中的方法。通過(guò)將硬件電路的比特流文件燒寫(xiě)到板載FLASH內(nèi),開(kāi)發(fā)板上電時(shí)將自動(dòng)地從FLASH中讀取比特流

2025-10-29 08:21:12

開(kāi)發(fā)板:MCU200T

攝像頭:OV5640

在我們小組開(kāi)發(fā)過(guò)程中,通常會(huì)遇到仿真結(jié)果正確,但下板運(yùn)行之后運(yùn)行錯(cuò)誤的情況,尤其是MCU200T開(kāi)發(fā)板本身的可觀察輸出引腳(LED等)還比較少,因此

2025-10-29 08:03:17

:

(2)然后運(yùn)行,待生成bin文件后,點(diǎn)擊VIVADO界面左上FLOW

(3)之后的步驟可參考網(wǎng)站:https://wenku.baidu.com/view

2025-10-29 06:57:46

prologue_setup.tcl文件后,都會(huì)出現(xiàn)文件路徑不匹配,總是在路徑前多出一個(gè)盤符加冒號(hào),類似“e:e:....”,所以在查閱了相關(guān)資料后,手動(dòng)將prologue_setup.tcl文件中的代碼做如下改動(dòng),本質(zhì)上是對(duì)字符串的切片刪除處理。

改完后再運(yùn)行tcl文件就正常了。

2025-10-28 07:19:22

使用rk3568開(kāi)發(fā)板,核0\\\\1\\\\3運(yùn)行linux,核2運(yùn)行hal,想在內(nèi)核中通過(guò)smc指令完成核0對(duì)核2得啟動(dòng)和關(guān)閉,文件系統(tǒng)中/sys/rk_amp目錄下有個(gè)boot_cpu文件,可以發(fā)起對(duì)核2得開(kāi)啟和關(guān)閉操作,但是目前會(huì)返回錯(cuò)誤,請(qǐng)問(wèn)如果解決呢

2025-10-27 10:09:54

在hbirdv2參考文檔中使用make指令生成system.bit和system.mcs文件,但是虛擬機(jī)本身會(huì)消耗計(jì)算資源,導(dǎo)致運(yùn)行速度變慢,對(duì)于不習(xí)慣在linux下編輯代碼的人,還需要來(lái)回倒騰代碼

2025-10-27 08:25:28

在移植內(nèi)核時(shí),用VIVADO進(jìn)行綜合實(shí)現(xiàn)后會(huì)出現(xiàn)時(shí)序違例,如圖:

雖然可以上板正常進(jìn)行開(kāi)發(fā),但是還是想把這些違例解決下^_^

檢查后,發(fā)現(xiàn)是 apb_adv_timer 這條路徑報(bào)的違例,解決方式

2025-10-27 07:32:41

環(huán)境:Vivado2018.3、NucleiStudio_IDE_202102-win64

內(nèi)容:Vivado仿真e203_hbirdv2跑whetstone跑分

以下提供可以在Vivado

2025-10-27 07:21:04

https://www.rvmcu.com/community-topic-id-386.html

以上鏈接為如何生成.verilog,并在VIVADO中生成波形的例子。我們?cè)趯?shí)踐過(guò)程中,發(fā)現(xiàn)了兩個(gè)

2025-10-27 06:41:49

工程

這里我們主要也是參考了論壇中的這篇文章來(lái)創(chuàng)建了一個(gè)Vivado的工程,這樣我們一個(gè)可以方便閱讀內(nèi)核代碼,另一方面,這也是我們進(jìn)行仿真的第一步。

創(chuàng)建后整個(gè)內(nèi)核的架構(gòu)大概如下圖:

唯一有一點(diǎn)

2025-10-27 06:35:08

本文將分享如何使用Nexys Video開(kāi)發(fā)板,移植e203

運(yùn)行FPGA原工程

首先進(jìn)入fpga原工程,如圖所示

使用下面命令打開(kāi)vivado

make install FPGA_NAME

2025-10-27 06:26:11

工程

這里我們主要也是參考了論壇中的這篇文章來(lái)創(chuàng)建了一個(gè)Vivado的工程,這樣我們一個(gè)可以方便閱讀內(nèi)核代碼,另一方面,這也是我們進(jìn)行仿真的第一步。

創(chuàng)建后整個(gè)內(nèi)核的架構(gòu)大概如下圖:

唯一有一點(diǎn)

2025-10-24 07:36:49

我們?cè)谧鰠①愓n題的過(guò)程中發(fā)現(xiàn),上FPGA開(kāi)發(fā)板跑系統(tǒng)時(shí),有時(shí)需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對(duì)添加了vivado ip核的soc系統(tǒng)進(jìn)行仿真。在這種情況下

2025-10-24 07:28:03

在做vivado綜合時(shí)和FPGA下載程序時(shí),我們碰到以下問(wèn)題,并找出了對(duì)應(yīng)的解決方案。

1.could not open include file”e203_defines.v”問(wèn)題

在做

2025-10-24 07:12:12

Vivado浮點(diǎn)數(shù)IP核的握手信號(hào)

我們的設(shè)計(jì)方案中,F(xiàn)PU計(jì)算單元將收到的三條數(shù)據(jù)和使能信號(hào)同步發(fā)給20多個(gè)模塊,同時(shí)只有一個(gè)模塊被時(shí)鐘使能,進(jìn)行計(jì)算,但結(jié)果都會(huì)保留,發(fā)給數(shù)選。計(jì)算單元還需接受

2025-10-24 07:01:36

vivado仿真運(yùn)行判斷狀態(tài)是否正確。

獲取二進(jìn)制代碼

在Nucleistudio中打開(kāi)相關(guān)項(xiàng)目的Properties,按路徑打開(kāi)C/C++ Build ->setting,找到

2025-10-24 06:46:36

vivado仿真運(yùn)行判斷狀態(tài)是否正確。

獲取二進(jìn)制代碼

在Nucleistudio中打開(kāi)相關(guān)項(xiàng)目的Properties,按路徑打開(kāi)C/C++ Build ->setting,找到

2025-10-24 06:31:26

Vivado浮點(diǎn)數(shù)IP核的一些設(shè)置注意點(diǎn)

我們?cè)?b class="flag-6" style="color: red">vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計(jì)算種類及多模式選擇。有時(shí)多種計(jì)算可以用同一個(gè)IP核實(shí)

2025-10-24 06:25:22

編譯完成后,我們會(huì)在工程目錄下發(fā)現(xiàn)生成了.verilog文件,此即為我們仿真需用到的文件,可以將改文件復(fù)制保存在tb目錄下

聯(lián)合仿真

在我們前面創(chuàng)建的Vivado工程中添加仿真文件

2025-10-23 06:22:05

如標(biāo)題所示,我們分享如何在Vivado上仿真蜂鳥(niǎo)SOC,仿真NucleiStudio編譯好的程序

具體步驟

1. 將蜂鳥(niǎo)soc移植到Vivado

只要將端口映射好,注意配置好時(shí)鐘和bank

2025-10-21 11:08:55

對(duì)蜂鳥(niǎo)E203內(nèi)核進(jìn)行優(yōu)化可以考慮以下幾個(gè)方面:

編譯器優(yōu)化:使用適合蜂鳥(niǎo)E203的編譯器選項(xiàng)和指令集,優(yōu)化編譯器的選項(xiàng)和參數(shù),開(kāi)啟對(duì)硬件的特定支持,比如使用-O2等優(yōu)化選項(xiàng),以提高代碼執(zhí)行效率

2025-10-21 07:55:16

我自己畫(huà)的底板,底板主要提供5V、接地以及JTAG連接器。但是插上XC7A35T的核心板后,vivado顯示找不到target(vivado截圖見(jiàn)圖1)。圖2-3是我的底板原理圖,原理圖和pcb文件在附件,求大佬指點(diǎn)迷津!!*附件:PCB_Project_1.rar

2025-10-13 16:05:54

想更換uart的引腳,但是換了就無(wú)法輸出信息了,除了這里還要改別的地方嗎?

2025-10-13 07:51:15

就是這樣更改無(wú)遺漏),設(shè)備端也更改后發(fā)現(xiàn)無(wú)法通信找不到原因(因?yàn)橹?b class="flag-6" style="color: red">改信道,其它通信相關(guān)參數(shù)eui等都不該),請(qǐng)問(wèn)改信道的話,節(jié)點(diǎn)都需要改哪些地方?:

節(jié)點(diǎn)改的幾個(gè)地方:

2025-10-11 06:03:25

隨著 AMD Spartan UltraScale+ 系列現(xiàn)已投入量產(chǎn),解鎖其功能集的最快途徑便是采用最新 AMD Vivado 工具版本( 2025.1 或更高版本)和全新操作指南資源。該集

2025-09-23 09:15:55 1390

1390

qkey軟件包,在內(nèi)核V5.0.2編譯無(wú)問(wèn)題,運(yùn)行報(bào)錯(cuò):

(rt_object_get_type(&m->parent

2025-09-15 07:46:09

許多硬件問(wèn)題只有在整個(gè)集成系統(tǒng)實(shí)時(shí)運(yùn)行的過(guò)程中才會(huì)顯現(xiàn)出來(lái)。AMD Vivado ChipScope 提供了一套完整的調(diào)試流程,可在系統(tǒng)運(yùn)行期間最大限度提升對(duì)可編程邏輯的觀測(cè)能力,助力設(shè)計(jì)調(diào)試。

2025-09-05 17:08:41 1023

1023 利用vivado進(jìn)行設(shè)計(jì)xilinx FPGA時(shí),寫(xiě)完設(shè)計(jì)代碼和仿真代碼后,點(diǎn)擊run simulation(啟動(dòng)modelsim進(jìn)行仿真)。

2025-08-30 14:22:17 1157

1157

科技云報(bào)到:壞了!數(shù)字人真要爆改百業(yè)了

2025-08-14 14:41:42 490

490 ,對(duì) KleidiAI 進(jìn)行了簡(jiǎn)要概述,并附有相關(guān)指南鏈接,其中詳細(xì)說(shuō)明了在 Linux 環(huán)境中運(yùn)行 KleidiAI 矩陣乘法 (matmul) 微內(nèi)核的分步操作,這份指南內(nèi)容詳實(shí)且極易上手。而本篇內(nèi)容則將

2025-08-08 15:16:37 3674

3674

在高并發(fā)微服務(wù)環(huán)境中,網(wǎng)絡(luò)性能往往成為K8s集群的瓶頸。本文將深入探討如何通過(guò)精細(xì)化的Linux內(nèi)核參數(shù)調(diào)優(yōu),讓你的K8s節(jié)點(diǎn)網(wǎng)絡(luò)性能提升30%以上。

2025-08-06 17:50:46 803

803 在使用 AMD Vivado Design Suite 對(duì)開(kāi)發(fā)板(Evaluation Board)進(jìn)行 FPGA 開(kāi)發(fā)時(shí),我們通常希望在創(chuàng)建工程時(shí)直接選擇開(kāi)發(fā)板,這樣 Vivado 能夠自動(dòng)配置

2025-07-15 10:19:43 1521

1521

TC334芯片有幾個(gè)ADC內(nèi)核

2025-07-14 07:08:32

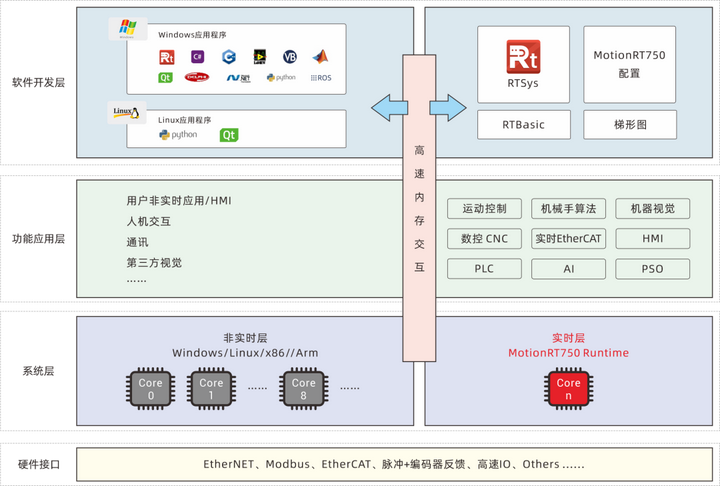

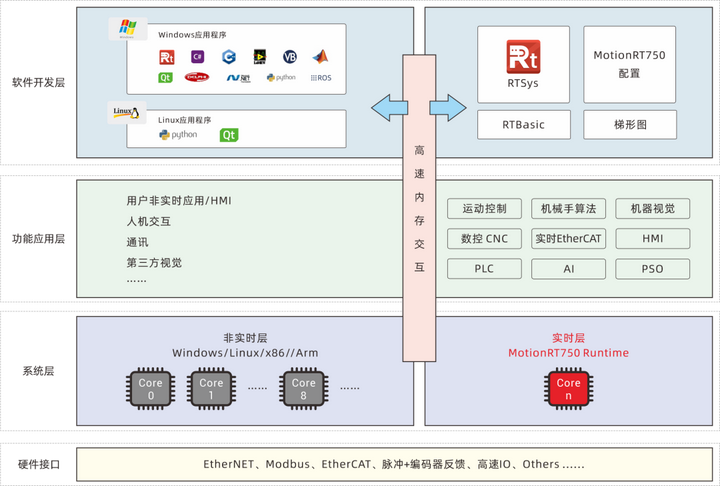

強(qiáng)實(shí)時(shí)運(yùn)動(dòng)控制內(nèi)核MotionRT750的驅(qū)動(dòng)安裝與內(nèi)核配置

2025-07-03 15:48:07 3528

3528

AMD Vivado Design Suite 2025.1 現(xiàn)已推出,支持 AMD Spartan UltraScale+ 和新一代 Versal 器件。這一最新版本還新增了多項(xiàng)功能,可顯著提升 Versal SSIT 器件的 FMAX 值,并對(duì)所有系列產(chǎn)品在 IP 集成和功能驗(yàn)證方面的易用性進(jìn)行了改進(jìn)。

2025-06-16 15:16:04 1342

1342 GPUStack 是一個(gè)用于運(yùn)行 AI 模型的開(kāi)源 GPU 集群管理器。它具有廣泛的硬件兼容性,支持多種品牌的 GPU,并能在 Apple MacBook、Windows PC 和 Linux 服務(wù)器上運(yùn)行

2025-06-06 11:45:31 2291

2291

在Linux系統(tǒng)運(yùn)維和性能優(yōu)化中,內(nèi)核參數(shù)(sysctl)的配置至關(guān)重要。合理的參數(shù)調(diào)整可以顯著提升網(wǎng)絡(luò)性能、系統(tǒng)穩(wěn)定性及資源利用率。然而,僅僅修改參數(shù)是不夠的,如何驗(yàn)證這些參數(shù)是否生效同樣關(guān)鍵。

2025-05-29 17:40:31 904

904 本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結(jié)果(以 Vivado 2024.2 為例)。

2025-05-19 14:22:26 1111

1111

有了內(nèi)核模塊以后,我們要如何使用呢?編譯驅(qū)動(dòng)有倆種方式,那 Linux 驅(qū)動(dòng)的運(yùn)行方式也肯定有倆種。一種就是將驅(qū)動(dòng)編譯進(jìn)內(nèi)核,這樣 Linux 系統(tǒng)啟動(dòng)后會(huì)自動(dòng)運(yùn)行程序。第二種就是將驅(qū)動(dòng)編譯成模塊

2025-05-14 10:56:58

設(shè)計(jì)、編譯、交付,輕松搞定。更快更高效。 Vivado 設(shè)計(jì)套件提供經(jīng)過(guò)優(yōu)化的設(shè)計(jì)流程,讓傳統(tǒng) FPGA 開(kāi)發(fā)人員能夠加快完成 Versal 自適應(yīng) SoC 設(shè)計(jì)。 面向硬件開(kāi)發(fā)人員的精簡(jiǎn)設(shè)計(jì)流程

2025-05-07 15:15:09 1170

1170

大家好,歡迎來(lái)到至芯科技FPGA煉獄營(yíng)地,準(zhǔn)備開(kāi)啟我們的偉大征程!正所謂“兵馬未動(dòng),糧草先行”,戰(zhàn)前的準(zhǔn)備自是必不可少,在FPGA的漫漫沙場(chǎng),我們何以入場(chǎng),何以取勝呢?在這里我們?yōu)楦魑粦?zhàn)友準(zhǔn)備了vivado 2018.3的使用教程。

2025-04-30 14:14:18 3068

3068

為了盡快把新產(chǎn)品推向市場(chǎng),數(shù)字系統(tǒng)的設(shè)計(jì)者需要考慮如何加速設(shè)計(jì)開(kāi)發(fā)的周期。設(shè)計(jì)加速主要可以從“設(shè)計(jì)的重用”和“抽象層級(jí)的提升”這兩個(gè)方面來(lái)考慮。Xilinx 推出的 Vivado HLS 工具可以

2025-04-16 10:43:12 1432

1432

Linux開(kāi)發(fā)中,編譯內(nèi)核是一項(xiàng)常見(jiàn)任務(wù),但不少開(kāi)發(fā)者在移動(dòng)硬盤或虛擬機(jī)環(huán)境下嘗試時(shí)會(huì)遭遇失敗。本文將簡(jiǎn)要探討這些問(wèn)題的成因,并介紹一些虛擬機(jī)使用技巧,幫助大家更好地應(yīng)對(duì)相關(guān)問(wèn)題。在移動(dòng)硬盤里編譯

2025-04-11 11:36:04 846

846

可以獲得兩個(gè)正在運(yùn)行的作系統(tǒng):一個(gè)在 A55 內(nèi)核上的 Linux,一個(gè)在 Zephyr 內(nèi)核上的 Zephyr。我經(jīng)常會(huì)更換 Zephyr OS,但不會(huì)更換 Linux作系統(tǒng),這就是為什么我試圖能夠

2025-04-08 07:23:37

implementation。

似乎獨(dú)立構(gòu)建會(huì)生成內(nèi)核映像和 DTB;嗯,兩者都有幾個(gè)版本。我認(rèn)為 Image 是內(nèi)核映像(基于名稱),我找到了一個(gè) imx8mn-evk.dtb,它似乎是我想要使用的 DTB。我

2025-04-04 06:07:05

我正在使用i.MX 8XDXL 評(píng)估套件并希望在 Cortex-A35 上運(yùn)行 Yocto Linux 映像cores 的Cortex-M4 上的 FreeRTOS 映像核心。

實(shí)現(xiàn)這一目標(biāo)的最佳

2025-04-04 06:02:06

我嘗試在最近的內(nèi)核中重新構(gòu)建以前版本 (4.19) 的 Linux 設(shè)備驅(qū)動(dòng)程序,即嵌入式平臺(tái)上的 6.1.22,ARM64 架構(gòu)。

驅(qū)動(dòng)程序管理 tty 設(shè)備。

當(dāng)我調(diào)用類似于用戶空間

2025-04-02 06:06:02

誰(shuí)能幫我了解如何使用 S32DS 在 MPC5775B 中并行運(yùn)行兩個(gè)內(nèi)核(core0 和 core2)?

2025-03-31 06:27:33

Vivado的時(shí)序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要?jiǎng)?chuàng)建xdc文件設(shè)置時(shí)序約束。時(shí)序約束文件可以直接創(chuàng)建或添加已存在的約束文件,創(chuàng)建約束文件有兩種方式:Constraints Wizard和Edit Timing Constraints,在綜合后或?qū)崿F(xiàn)后都可以進(jìn)行創(chuàng)建。

2025-03-24 09:44:17 4561

4561

CMS32F0332是M0+內(nèi)核,最快支持64MHz運(yùn)行,工作電壓2.1V~5.5V,多達(dá)30個(gè)GPIO,2個(gè)UART,1個(gè)SPI,1個(gè)I2C,2組CCP模塊,內(nèi)置2路模擬比較器、2路運(yùn)算放大器、2

2025-03-18 09:04:01

各位大佬,我想請(qǐng)教一個(gè)問(wèn)題:

為了驗(yàn)證H750主時(shí)鐘頻率和功耗的關(guān)系:

用STM32CUBEMX配置STM32H750VBT6的主時(shí)鐘為:100MHz,程序可以正常運(yùn)行,然后將主時(shí)鐘改至120MHz

2025-03-12 06:38:48

e203自定義指令硬件模塊設(shè)計(jì),修改內(nèi)核,綜合沒(méi)錯(cuò)誤,軟件也修改工具鏈通過(guò)并產(chǎn)生verilog文件,但在vivado硬件里自定義指令識(shí)別為非法指令怎么解決

2025-03-07 07:34:21

獲取具有三個(gè)輸出的自定義模型的輸出張量: 從 openvino.runtime 導(dǎo)入內(nèi)核

內(nèi)核 = 內(nèi)核()

model = core.read_model(model=“model.xml

2025-03-05 09:44:30

的幾個(gè)依賴庫(kù)的版本,在我下載的process sdk不一致。

4. 運(yùn)行ti_cnnperfsim.exe之后,會(huì)生成perfSimInfo.bin 這個(gè)里面的數(shù)據(jù)是什么,我認(rèn)為可能是最后一個(gè)layer的計(jì)算完成的數(shù)據(jù),但是我計(jì)算了一下大小,并不匹配。

2025-03-03 06:35:23

隨著微秒級(jí)NVMe存儲(chǔ)的蓬勃發(fā)展,Linux內(nèi)核存儲(chǔ)棧的開(kāi)銷幾乎是存儲(chǔ)訪問(wèn)時(shí)間的兩倍,已經(jīng)成為性能瓶頸。

2025-03-01 16:09:35 946

946

Xilinx的FIR IP核屬于收費(fèi)IP,但是不需要像 Quartus那樣通過(guò)修改license文件來(lái)破解。如果是個(gè)人學(xué)習(xí),現(xiàn)在網(wǎng)絡(luò)上流傳的license破解文件在破解Vivado的同時(shí)也破解

2025-03-01 14:44:19 2709

2709

本文使用 DDS 生成三個(gè)信號(hào),并在 Vivado 中實(shí)現(xiàn)低通濾波器。低通濾波器將濾除相關(guān)信號(hào)。

2025-03-01 14:31:37 2585

2585

【技術(shù)分享】迅為RK3568開(kāi)發(fā)板使用TFTP加載內(nèi)核設(shè)備樹(shù)

2025-02-21 14:04:46 1197

1197

在運(yùn)行230evm時(shí),有時(shí)會(huì)發(fā)生這種情況,只會(huì)發(fā)出藍(lán)光,還有在運(yùn)行實(shí)例程序時(shí)會(huì)顯示不太正確的圖像。最近剛買了五個(gè)230evm,其他幾個(gè)都正常,只有一個(gè)有這種情況。請(qǐng)問(wèn)這是投影儀硬件問(wèn)題嘛。

2025-02-21 09:18:35

本文檔涵蓋了如何驅(qū)動(dòng) AMD Vivado Design Suite 來(lái)分析和改善您的設(shè)計(jì)。

2025-02-19 11:22:26 989

989

要降低顛轉(zhuǎn)儀在運(yùn)行過(guò)程中的能耗,可從電機(jī)選型、傳動(dòng)系統(tǒng)優(yōu)化以及控制系統(tǒng)設(shè)計(jì)這幾個(gè)關(guān)鍵維度入手。 在電機(jī)選型方面,永磁同步電機(jī)是極具優(yōu)勢(shì)的選擇。相較于普通異步電機(jī),永磁同步電機(jī)的效率明顯更高。這主要

2025-02-13 09:26:24 680

680

的可持續(xù)發(fā)展提供了新的思路。接下來(lái)和大家一起探索個(gè)人電腦改云存儲(chǔ)的教程。 ? ?個(gè)人電腦改云存儲(chǔ)的教程: ? ?和把電腦改成云存儲(chǔ)方法類似。下載安裝云存儲(chǔ)軟件,如OwnCloud,按照安裝向?qū)瓿砂惭b。安裝后,在軟件界面進(jìn)行個(gè)

2025-01-22 10:30:46 688

688

在嵌入式項(xiàng)目開(kāi)發(fā)中,為了適配新外設(shè)、調(diào)整硬件資源分配或修復(fù)驅(qū)動(dòng)問(wèn)題,需要頻繁修改設(shè)備樹(shù)和內(nèi)核。修改完成后,通常需要重新編譯生成鏡像,并將其燒錄到開(kāi)發(fā)板上進(jìn)行測(cè)試。然而,傳統(tǒng)的燒錄方式不僅需要連接物理接口,還可能因?yàn)殓R像體積較大而耗費(fèi)較長(zhǎng)時(shí)間,這在開(kāi)發(fā)周期緊張的情況下顯得尤為低效。

2025-01-17 15:52:09 1946

1946

電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南: 設(shè)計(jì)分析與收斂技巧.pdf》資料免費(fèi)下載

2025-01-15 15:28:44 2

2 電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南:邏輯仿真.pdf》資料免費(fèi)下載

2025-01-15 15:25:58 0

0 Vivado Tcl零基礎(chǔ)入門與案例實(shí)戰(zhàn)-高亞軍編寫(xiě)

2025-01-14 11:13:49

電子發(fā)燒友網(wǎng)站提供《AN-354: 應(yīng)用工程師問(wèn)答——1幾個(gè)問(wèn)題.pdf》資料免費(fèi)下載

2025-01-13 15:43:31 0

0 基于8051內(nèi)核MCU AiP8F3216的小型制氧機(jī)方案

2025-01-10 09:04:14 1009

1009

家用制氧機(jī)需要檢測(cè)的壓力值主要包括以下幾個(gè)方面:一、工作壓力家用制氧設(shè)備的工作壓力是選購(gòu)時(shí)需重點(diǎn)關(guān)注的參數(shù)之一。一般來(lái)說(shuō),家用制氧機(jī)的工作壓力設(shè)定在0.04至0.07MPa之間。這一范圍既能保證制氧

2025-01-07 11:54:42 3004

3004

關(guān)于內(nèi)核啟動(dòng)流程涉及內(nèi)容較多而且復(fù)雜,過(guò)度的分析意義不大,因此,這里不做詳細(xì)講解,只做一個(gè)大概的介紹。初學(xué)者只做了解,有一定基礎(chǔ)的可以深入理解。

內(nèi)核鏡像被uboot加載到內(nèi)存空間之后,獲得控制權(quán)

2025-01-06 09:51:55

rk3566-pwm內(nèi)核驅(qū)動(dòng)

2025-01-05 09:18:09 0

0

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

654

654

722

722 393

393

657

657

1433

1433

645

645 1390

1390

1023

1023 1157

1157

3674

3674

803

803 1521

1521

3528

3528

1342

1342 2291

2291

904

904 1111

1111

1170

1170

3068

3068

1432

1432

846

846

4561

4561

946

946

2709

2709

2585

2585

1197

1197

989

989

680

680

688

688

1946

1946

2

2 0

0 0

0 3004

3004

評(píng)論