作者: 碎碎思,來(lái)源:OpenFPGA

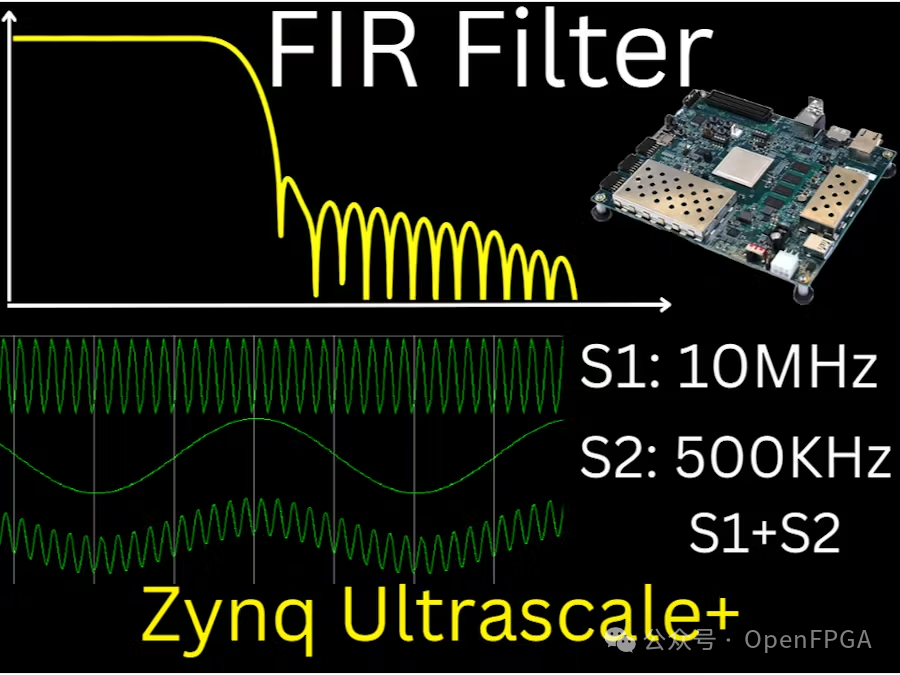

本文使用 DDS 生成三個(gè)信號(hào),并在 Vivado 中實(shí)現(xiàn)低通濾波器。低通濾波器將濾除相關(guān)信號(hào)。

介紹

用DDS生成三個(gè)信號(hào),并在Vivado中實(shí)現(xiàn)低通濾波器。低通濾波器將濾除較快的信號(hào)。

本文分為幾個(gè)主要部分:

信號(hào)生成:展示如何使用DDS(直接數(shù)字合成)IP生成測(cè)試信號(hào) - 10 MHz 信號(hào)和 500 kHz 信號(hào),然后將它們組合起來(lái)創(chuàng)建混合信號(hào)進(jìn)行測(cè)試。

FIR 濾波器設(shè)計(jì):解釋影響 FIR 濾波器性能的關(guān)鍵因素,包括:

抽頭數(shù)量及其對(duì)濾波器響應(yīng)的影響

量化和系數(shù)位寬設(shè)計(jì)

權(quán)衡資源利用

設(shè)計(jì):演示使用 Vivado 進(jìn)行設(shè)計(jì),包括

設(shè)置FIR IP

使用 MATLAB 生成的系數(shù)配置濾波器參數(shù)

設(shè)置適當(dāng)?shù)奈粚捄?a href="http://www.3532n.com/tags/時(shí)鐘/" target="_blank">時(shí)鐘頻率

添加必要的組件,如時(shí)鐘源和 ILA(集成邏輯分析儀)

測(cè)試和驗(yàn)證:顯示如何通過(guò)以下方式驗(yàn)證濾波器的操作:

仿真結(jié)果顯示高頻分量的濾波

FPGA 板上的硬件實(shí)現(xiàn)

使用基于計(jì)數(shù)器的脈沖發(fā)生器觀(guān)察濾波器脈沖響應(yīng)的特殊技術(shù)

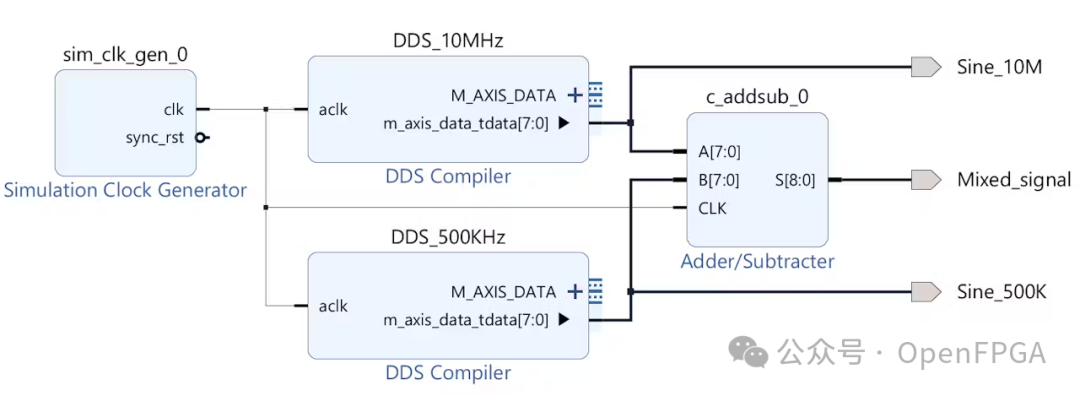

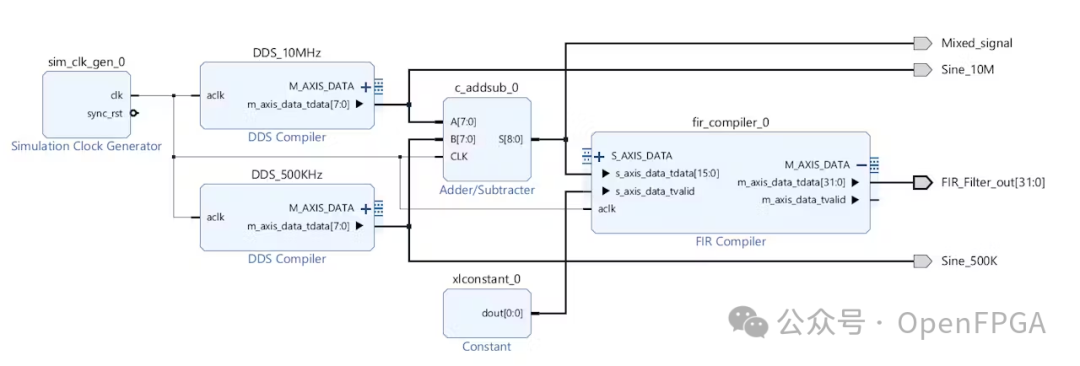

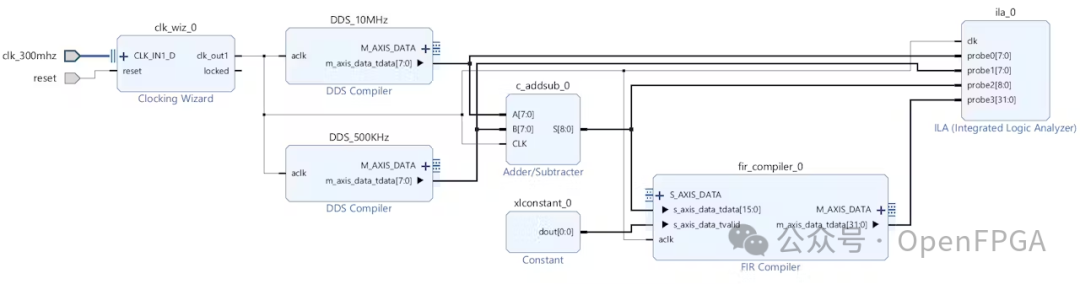

第 1 部分:DDS 設(shè)置,用于生成兩個(gè)信號(hào)和混合信號(hào)

首先為測(cè)試臺(tái)生成信號(hào):

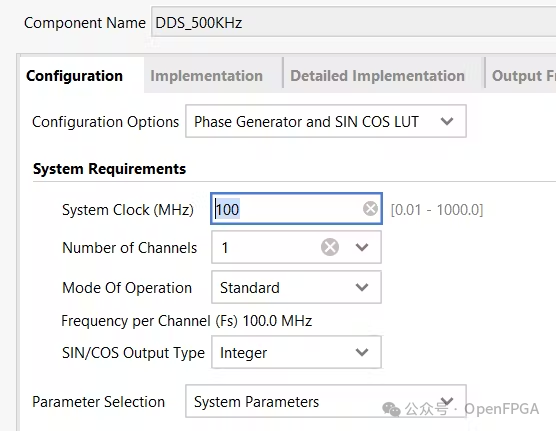

在BD設(shè)計(jì)中添加 DDS IP。在配置選項(xiàng)卡中,將系統(tǒng)時(shí)鐘設(shè)置為 100 MHz。

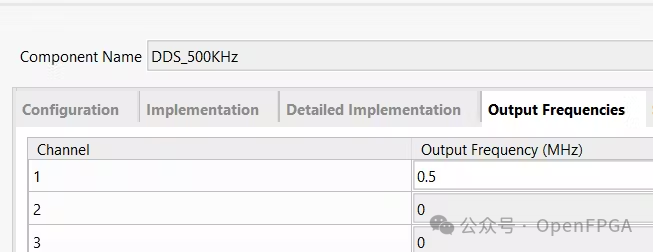

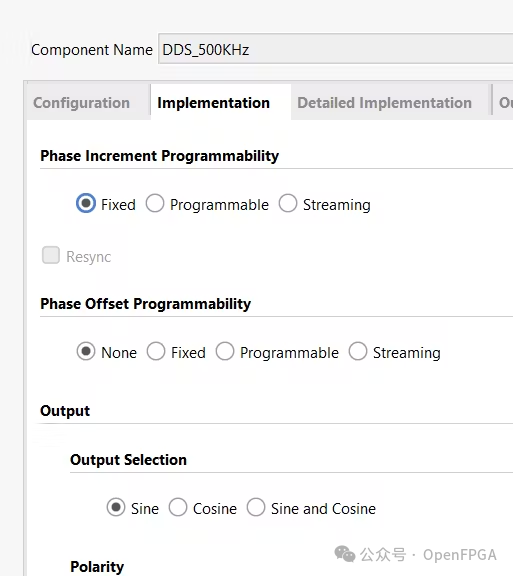

由于我們只需要生成正弦波,因此在Implementation選項(xiàng)卡中,選擇輸出為Sine選項(xiàng),并取消選擇相位輸出選項(xiàng)。在Output Frequency選項(xiàng)卡中,將Channel 1的頻率設(shè)置為 500 kHz。

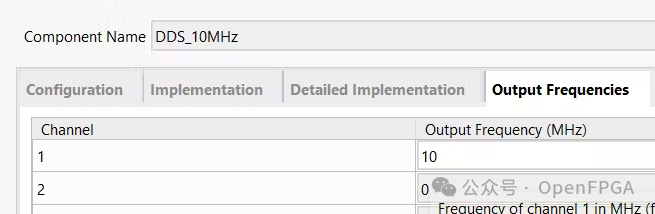

在BD設(shè)計(jì)中添加另一個(gè) DDS IP。重復(fù)相同的設(shè)置,但這次將輸出頻率設(shè)置為 10 MHz。

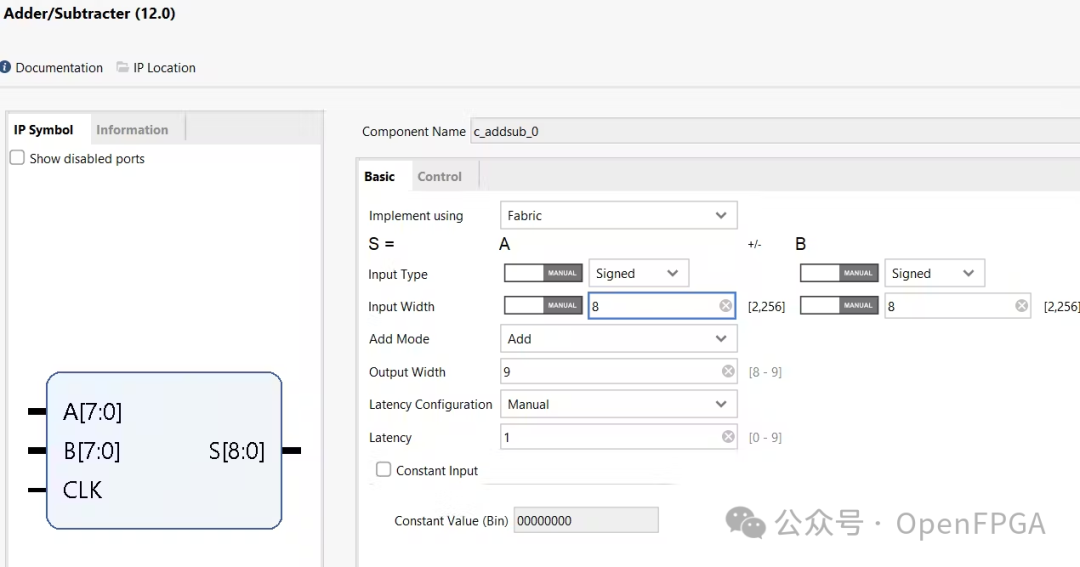

在BD設(shè)計(jì)中添加一個(gè)加法器。將其輸入位寬設(shè)置為 8,將其輸出位寬設(shè)置為 9。

將兩個(gè) DDS 編譯器的輸出連接到加法器的輸入。這將生成混合信號(hào)。

在設(shè)計(jì)中添加一個(gè)模擬時(shí)鐘發(fā)生器,并將其頻率設(shè)置為 100MHz。該頻率也是設(shè)計(jì)的采樣率

DDS編譯器仿真結(jié)果:

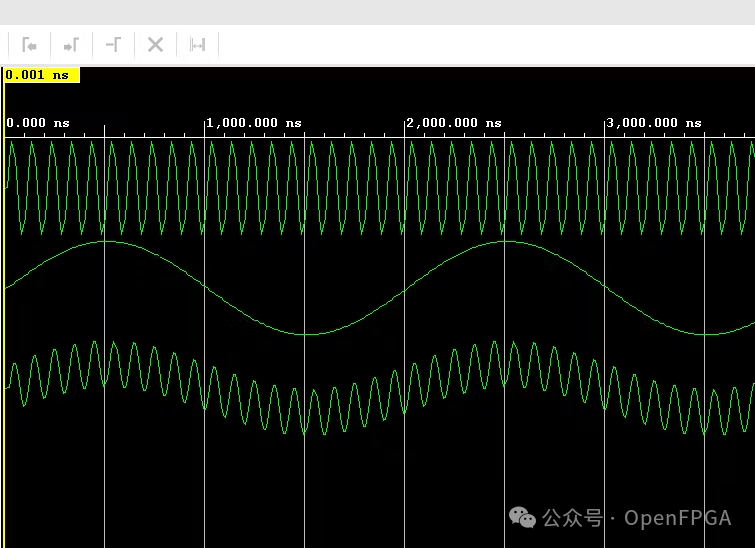

如仿真結(jié)果所示:

第一個(gè)正弦波的周期為 2000 ns,這是一個(gè) 500 kHz 的信號(hào)。

第二個(gè)正弦波的周期為 100 ns,這是一個(gè) 10 MHz 信號(hào)。

還可以觀(guān)察混合信號(hào),其中較快信號(hào)的幅度以較慢信號(hào)的頻率波動(dòng),從而顯示了兩個(gè)頻率的組合。

Vivado FIR 濾波器仿真

FIR 濾波器配置:FIR 濾波器的性能受幾個(gè)因素影響:

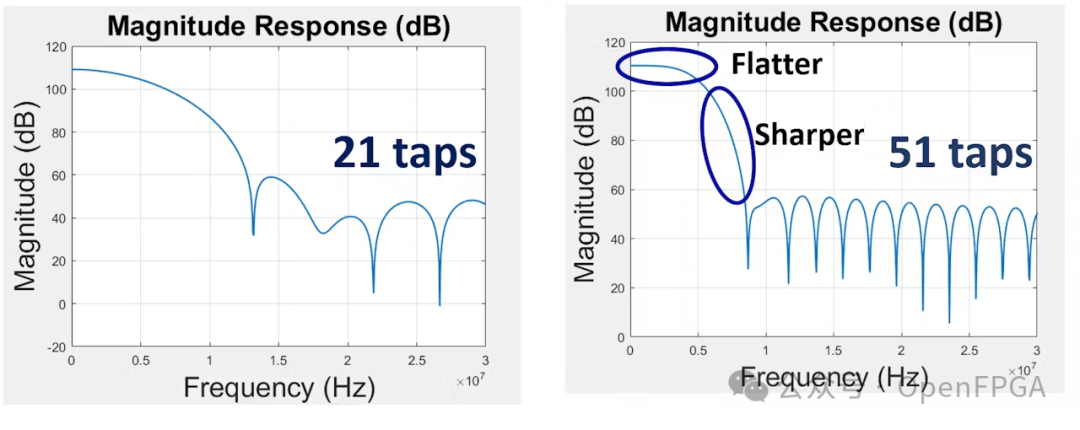

抽頭數(shù)量:

增加抽頭數(shù)量可改善濾波器響應(yīng),從而使通帶更平坦,波紋更少,振鈴減少。

更多的抽頭數(shù)還會(huì)增強(qiáng)截止頻率的衰減,從而提高濾波器的精度。然而,更多的抽頭會(huì)引入更大的延遲,這可能不適合某些 DSP 系統(tǒng)。

不同抽頭數(shù)的FIR濾波器響應(yīng)比較

不同抽頭數(shù)的FIR濾波器響應(yīng)比較

量化和濾波器系數(shù)位寬:

量化-通過(guò)將數(shù)字映射到由分配的位寬決定的一組固定的離散值來(lái)降低數(shù)字的精度。

使用較少的位數(shù)進(jìn)行量化會(huì)降低濾波器系數(shù)的準(zhǔn)確性,從而對(duì)濾波器的性能產(chǎn)生負(fù)面影響。

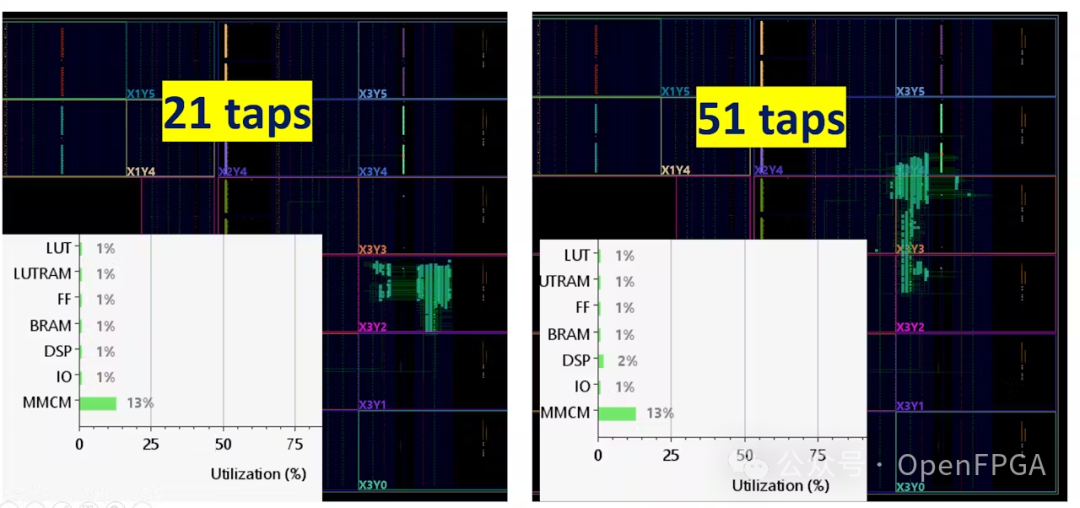

資源權(quán)衡:

濾波器性能和 FPGA 資源利用率之間存在權(quán)衡。

增加抽頭數(shù)量或系數(shù)的位寬需要更多的 DSP 資源,這可能會(huì)消耗 FPGA 很多資源。

兩種不同F(xiàn)IR濾波器所需的FPGA資源

兩種不同F(xiàn)IR濾波器所需的FPGA資源

通過(guò)平衡這些因素,可以?xún)?yōu)化 FIR 濾波器以滿(mǎn)足應(yīng)用程序的特定要求。

在 Matlab 中生成量化 FIR 濾波器抽頭

為了簡(jiǎn)化工作,提供了一個(gè)可以輕松生成量化 FIR 濾波器的 Matalab 代碼,可以在 Vivado 中直接使用它:

closeall clearall clc %%setuptheparametershere Sample_Rate=50e6; cutoff_frequency=5e6; number_of_filter_taps=191;%mustbeoddnumber! filter_taps_bitwidth=10; lowpass_highpass='low';%shouldbeloworhigh %%Caluculatethetaps Nyquist_frequency=Sample_Rate/2; Wn=cutoff_frequency/(Nyquist_frequency); %Generatearowvectorbcontainingthen+1coefficients filter_taps=fir1(number_of_filter_taps-1,Wn,lowpass_highpass); %%Quantization %onebitforsign filter_taps=floor(filter_taps/max(filter_taps)*(2^(filter_taps_bitwidth-1)-1)); %%plotthefilterresponse N=1024;%Numberofpointsforthefrequencyresponse [H,f]=freqz(filter_taps,1,N,Sample_Rate);%Calculatethefrequencyresponse %Magnitudeandphaseresponse magnitude=abs(H);%Magnituderesponse %Plotthefilterresponse %Magnituderesponseplot figure; plot(f,20*log10(magnitude),'linewidth',1.3);%PlotmagnitudeindB gridon; title('MagnitudeResponse(dB)',FontSize=22); xlabel_txt='Frequency(Hz)'; xlabel(xlabel_txt,FontSize=22); ylabel('Magnitude(dB)',FontSize=22); %xlim([030e6]) figure freqz(filter_taps,1) figure stem(filter_taps,'linewidth',1.3) gridon;

在提供的Matlab代碼中,需要配置以下參數(shù):

采樣率:這是采樣頻率,在我們的設(shè)計(jì)中它對(duì)應(yīng)于驅(qū)動(dòng)系統(tǒng)的時(shí)鐘頻率。

截止頻率:指定濾波器的截止頻率。

抽頭數(shù):設(shè)置濾波器的抽頭數(shù),決定濾波器的精度和性能。

抽頭位寬:定義濾波器系數(shù)的位寬,影響量化精度。

濾波器類(lèi)型:選擇需要的濾波器類(lèi)型。此代碼目前僅支持高通和低通濾波器。

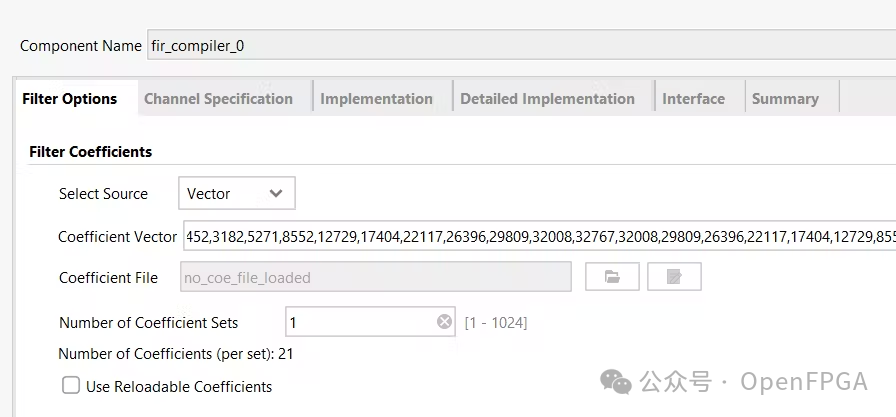

Vivado 中的 FIR 編譯器 IP 設(shè)置:

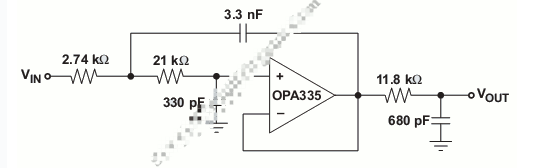

借助 Matlab 代碼,生成截止頻率為 1MHz、量化為 16 位的 21 個(gè)濾波器抽頭。需要進(jìn)行少許修改才能使生成的值在 Vivado 中可用。

復(fù)制 FIR 濾波器抽頭并將其粘貼到“濾波器選項(xiàng)”選項(xiàng)卡 下的“系數(shù)向量”字段中。

請(qǐng)注意,一旦更新濾波器系數(shù),實(shí)施選項(xiàng)卡中的輸出寬度將自動(dòng)調(diào)整。

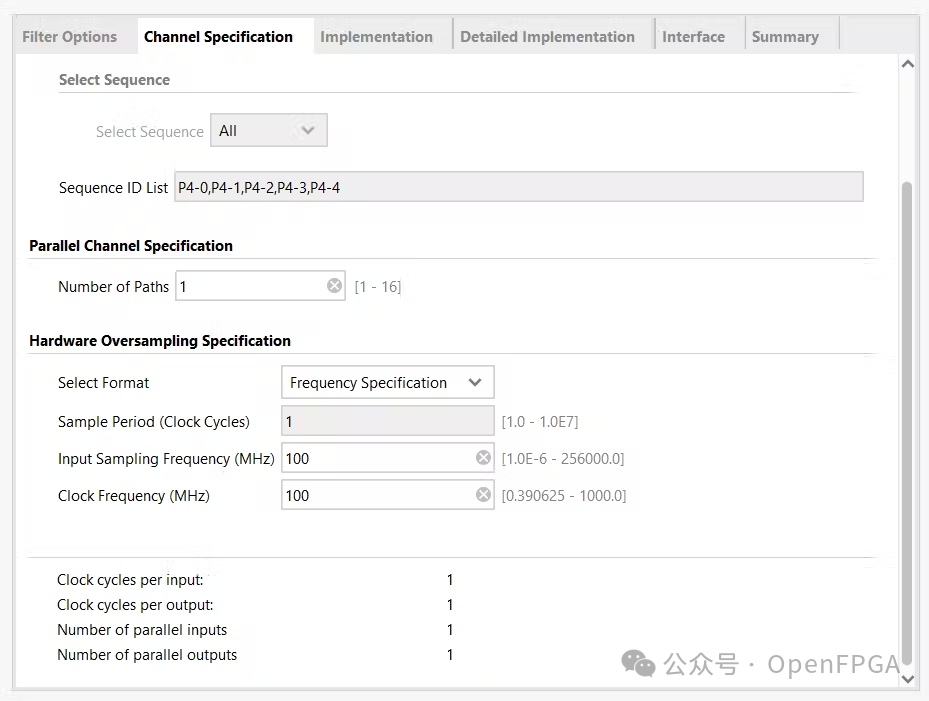

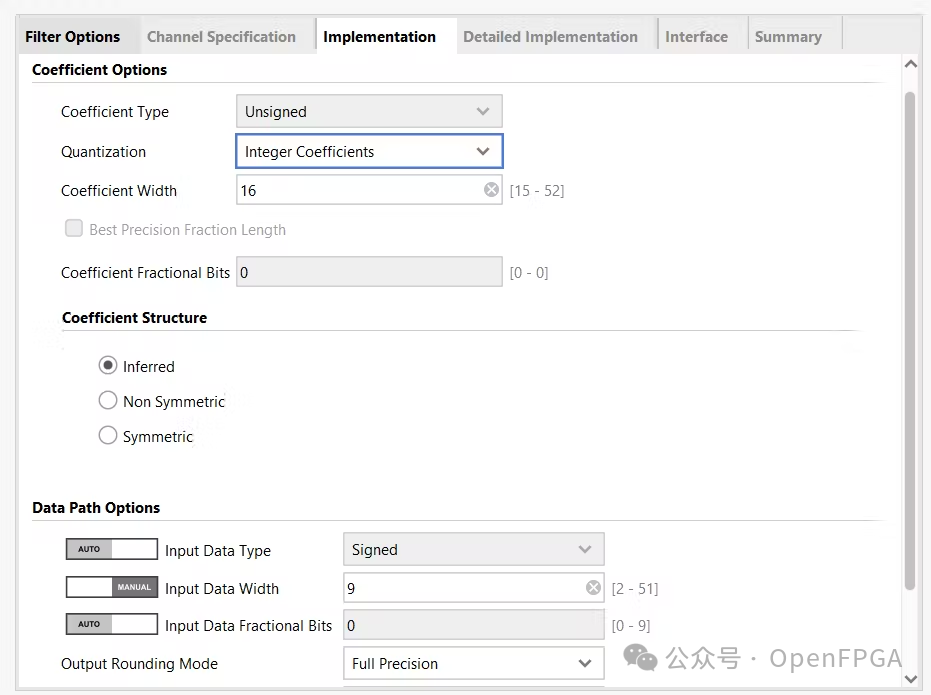

在“通道規(guī)范”選項(xiàng)卡中,設(shè)置采樣率和時(shí)鐘頻率匹配連接到 FIR 濾波器的時(shí)鐘。在本教程中,我們使用 100 MHz 時(shí)鐘。

在“實(shí)施”選項(xiàng)卡中,配置“輸入位寬”以匹配輸入信號(hào)的位寬。例如,由于此設(shè)計(jì)中加法器的輸出有 9 位,因此將輸入位寬設(shè)置為 9。

這樣FIR 濾波器現(xiàn)已配置完畢并可以使用。

請(qǐng)注意,F(xiàn)IR 濾波器的輸入和輸出位寬與正確的字節(jié)數(shù)對(duì)齊。例如,當(dāng)我們將輸入位寬設(shè)置為 9 位時(shí),濾波器的實(shí)際輸入位寬會(huì)調(diào)整為 2 個(gè)字節(jié)(16 位)。

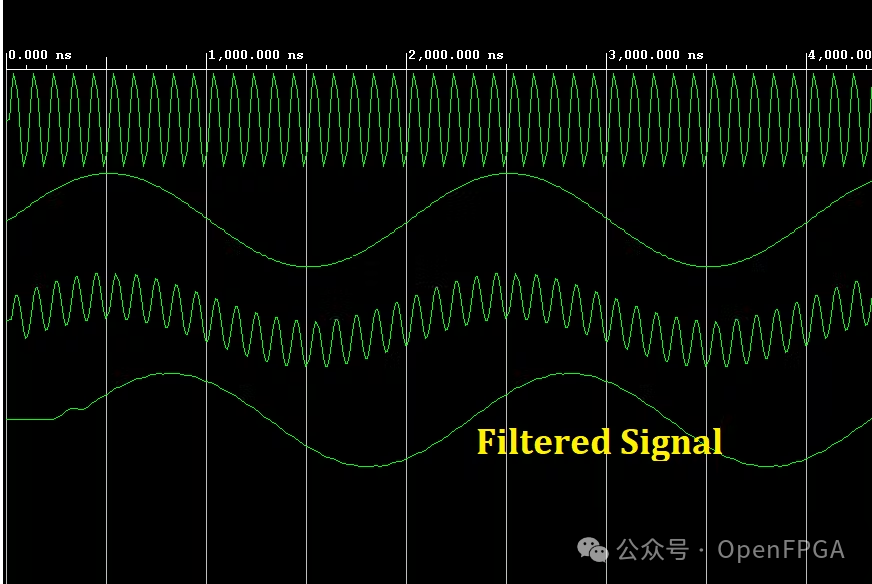

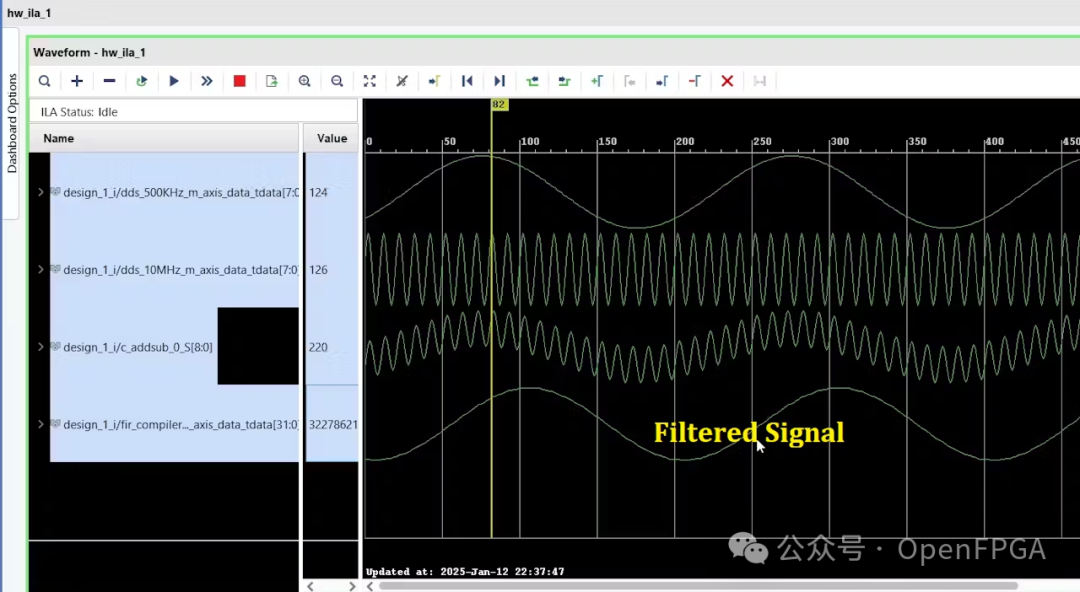

仿真結(jié)果

仿真就會(huì)觀(guān)察到 FIR 濾波器表現(xiàn)為低通濾波器,衰減頻率更高的信號(hào)。

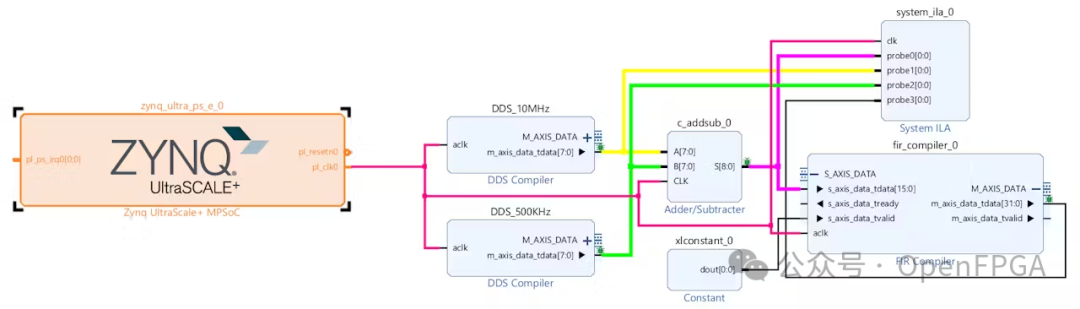

Vivado 綜合

上訴設(shè)計(jì)都是可綜合的,在系統(tǒng)內(nèi)為設(shè)計(jì)添加時(shí)鐘后就可以進(jìn)行綜合和實(shí)現(xiàn)了。

最后,需要在設(shè)計(jì)中加入一個(gè) ILA 來(lái)監(jiān)控和研究目標(biāo)信號(hào)。移除所有額外的端口,并將它們連接到 ILA。

使用上面的架構(gòu)需要使用SDK或者Vitis運(yùn)行一個(gè)簡(jiǎn)單的“HelloWorld!”程序。

如果使用板載時(shí)鐘就按照需求進(jìn)行修改。

運(yùn)行后,應(yīng)該能看到與仿真相同的結(jié)果:

-

FPGA

+關(guān)注

關(guān)注

1661文章

22442瀏覽量

637468 -

濾波器

+關(guān)注

關(guān)注

162文章

8419瀏覽量

185938 -

FIR

+關(guān)注

關(guān)注

4文章

152瀏覽量

35598 -

Vivado

+關(guān)注

關(guān)注

19文章

859瀏覽量

71237

原文標(biāo)題:FPGA DSP:Vivado 中帶有 DDS 的 FIR 濾波器

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于 FPGA 的任意波形發(fā)生器+低通濾波器系統(tǒng)設(shè)計(jì)

基于 FPGA 的任意波形發(fā)生器+低通濾波器系統(tǒng)設(shè)計(jì)

低通濾波器如何設(shè)計(jì)?

有源濾波器中數(shù)字低通濾波器的設(shè)計(jì)及其DSP實(shí)現(xiàn)

基于DDS的低通濾波器設(shè)計(jì)與仿真

基于DDS的橢圓函數(shù)低通濾波器的設(shè)計(jì)

DDS信號(hào)發(fā)生器中橢圓低通濾波器的設(shè)計(jì)

LC低通濾波器作用及應(yīng)用案例

低通濾波器的設(shè)計(jì)與實(shí)現(xiàn)

低通濾波器與匹配濾波器的區(qū)別

低通濾波器與高通濾波器有什么不同

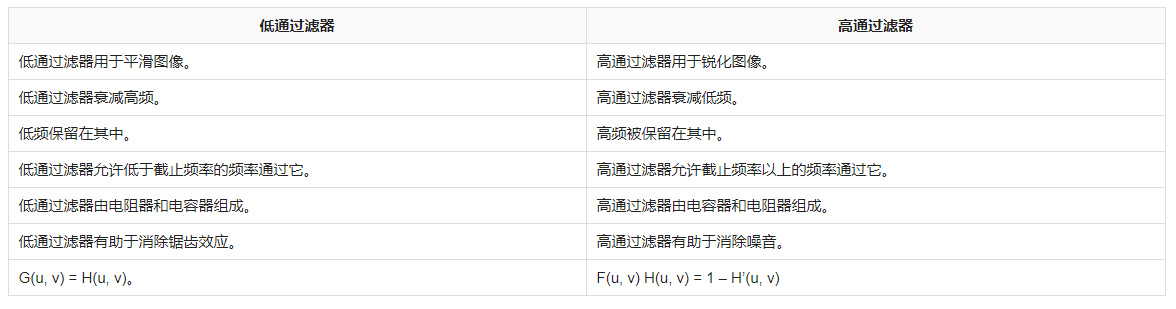

有源低通濾波器設(shè)計(jì)原理 有源低通濾波器的截止頻率計(jì)算

什么是低通濾波器?低通濾波器有什么作用?

使用DDS生成三個(gè)信號(hào)并在Vivado中實(shí)現(xiàn)低通濾波器

使用DDS生成三個(gè)信號(hào)并在Vivado中實(shí)現(xiàn)低通濾波器

評(píng)論