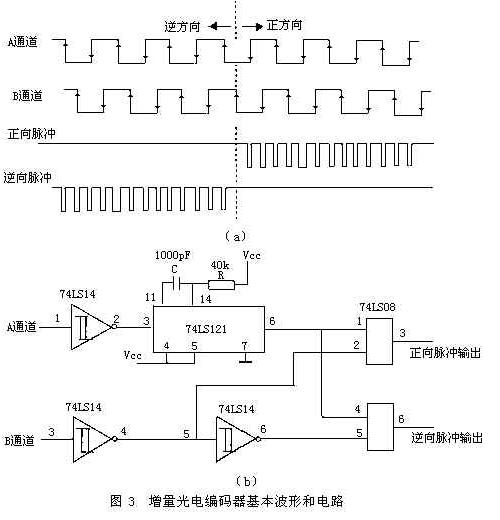

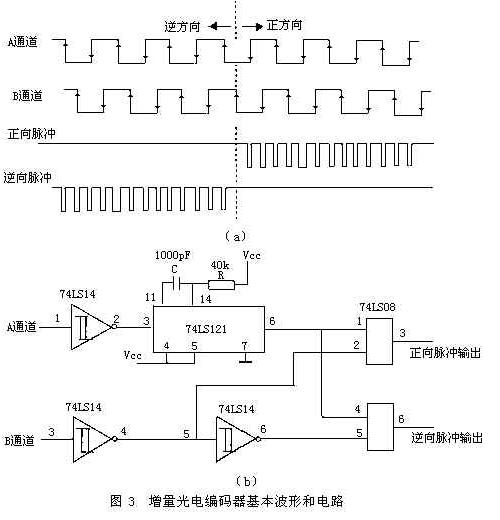

增量光電編碼器基本波形和電路

?

采用旋轉(zhuǎn)式光電編碼器,把它的轉(zhuǎn)軸與重力測量儀中補(bǔ)償旋鈕軸相連。重力測量儀中補(bǔ)償旋鈕的角位移

2009-09-26 17:28:45 6441

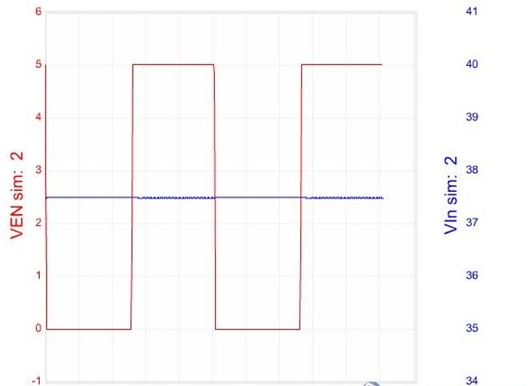

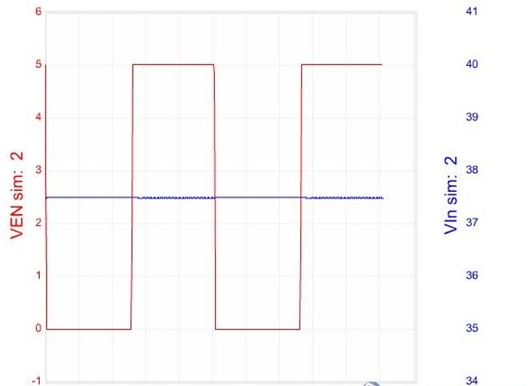

6441 最近進(jìn)行了一款燈具的設(shè)計(jì),利用了WEBENCH的波形仿真的強(qiáng)大功能,真對(duì)性的運(yùn)用仿真設(shè)計(jì),其實(shí)實(shí)際設(shè)計(jì)時(shí)用的仿真波形比較多,進(jìn)行的各種軟件對(duì)比和方案篩選也比較多,進(jìn)行的波形仿真的數(shù)據(jù)對(duì)比也較多,今天

2018-04-02 09:18:13 9136

9136

我在用VHDL寫TESTBENCH進(jìn)行仿真時(shí),出現(xiàn)了一個(gè)錯(cuò)誤,說不能打開設(shè)計(jì)工程中一個(gè)后綴為 ”rdb“的文件,而且最終modelsim出來的波形也不對(duì),求教高手,這是怎么回事,該怎么改

2013-12-07 10:56:17

VHDL特點(diǎn)是什么VHDL語言在EDA仿真中的應(yīng)用

2021-04-29 06:01:15

使用。書中還附有大量程序設(shè)計(jì)和實(shí)驗(yàn)、實(shí)踐方面的習(xí)題。本書可作為高等院校的電子工程、通信、工業(yè)自動(dòng)化、計(jì)算機(jī)應(yīng)用技術(shù)、電子對(duì)抗、儀器儀表、數(shù)字信號(hào)處理、圖像處理等學(xué)科領(lǐng)域和專業(yè)的高年級(jí)本科生或研究生的VHDL

2008-06-04 10:31:29

DAP仿真器 BURNER

2023-03-28 13:06:20

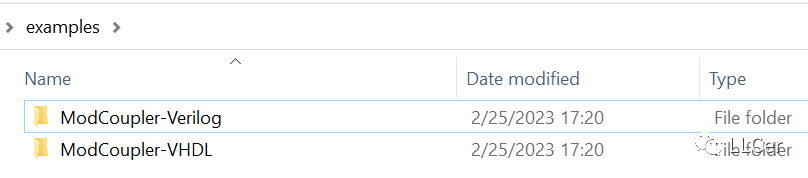

DDR SDRAM參考設(shè)計(jì)VHDL版(有詳細(xì)的文檔,仿真綜合文件)File/Directory Description

2012-08-11 09:33:30

本文以戰(zhàn)術(shù)軍用通信系統(tǒng)的首選碼RS(31,15)碼為例,對(duì)生成多項(xiàng)式進(jìn)行了優(yōu)化,并采用查表法的原理極大地提高了編碼器運(yùn)算數(shù)據(jù)的能力,縮短了運(yùn)算周期,最終利用VHDL語言編譯,在FPGA中實(shí)現(xiàn),得到了正確的RS編譯碼。

2021-05-06 09:27:33

嗨,大家好,我遇到的問題如下:我在vivaldo webpack中運(yùn)行vhdl模擬。當(dāng)運(yùn)行模擬對(duì)話框彈出時(shí),仿真似乎已啟動(dòng)并運(yùn)行。但是,運(yùn)行模擬會(huì)顯示當(dāng)前時(shí)間:0fs并且不顯示波形。感謝幫助。謝謝

2020-04-07 14:42:53

我有一些VHDL 編寫的程序請問如何對(duì)他們進(jìn)行軟件仿真 要求出波形。

2010-05-07 09:36:22

一個(gè)四分頻設(shè)計(jì)VHDL文件編譯成功了,在進(jìn)行波形仿真時(shí)報(bào)錯(cuò)怎么回事?版本是quartus II 15.0網(wǎng)上說要編譯鏈接庫,我也編譯了,還是報(bào)錯(cuò)。新手求指教!!!

2019-04-19 16:54:34

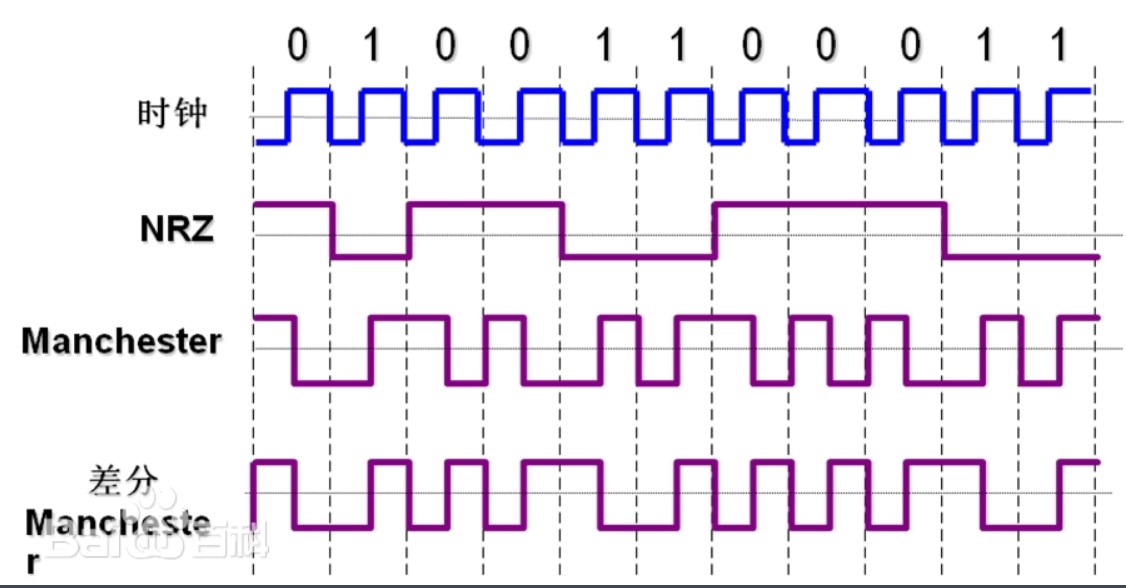

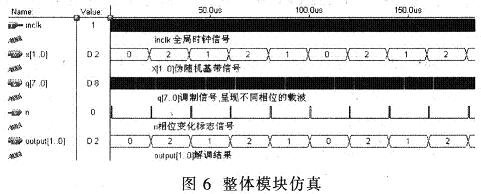

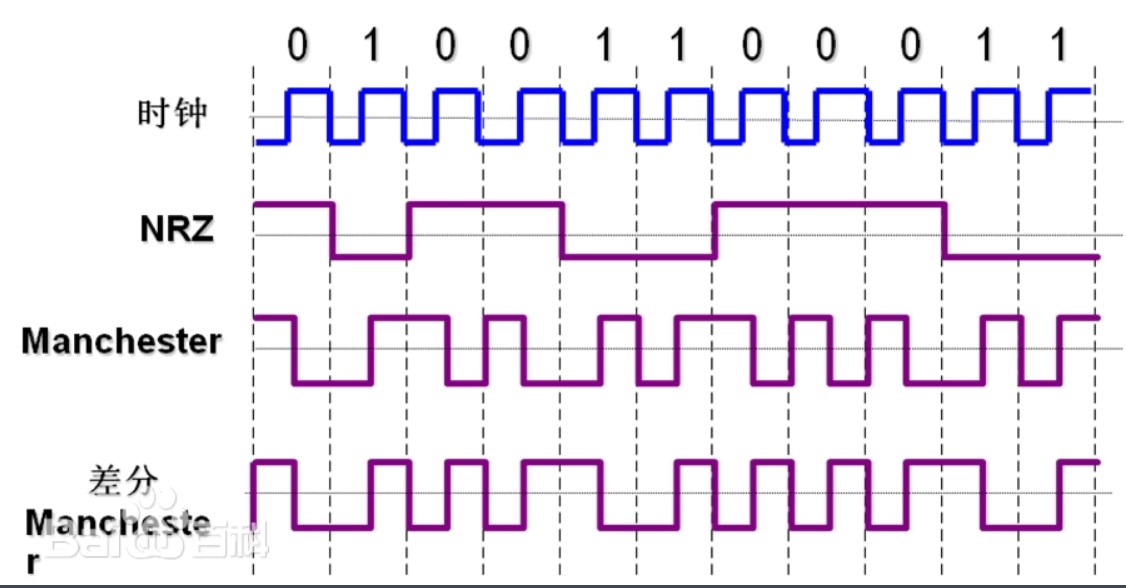

所示。圖22 八種編碼波形總結(jié)1) 運(yùn)用VHDL編寫以上八種編碼是可行的。2) 經(jīng)過觀察各模塊的仿真波形,符合各個(gè)編碼的特性。3) 通過整體程序的調(diào)試仿真,并在FPGA上實(shí)現(xiàn)了波形的鍵選。

2015-01-29 14:11:42

本帖最后由 eehome 于 2013-1-5 10:03 編輯

電子時(shí)鐘VHDL程序與仿真1. 10進(jìn)制計(jì)數(shù)器設(shè)計(jì)與仿真(1)10進(jìn)制計(jì)數(shù)器VHDL程序--文件名:counter10.vhd

2012-03-05 15:13:19

本帖最后由 eehome 于 2013-1-5 09:56 編輯

自動(dòng)售貨機(jī)VHDL程序與仿真(1)自動(dòng)售貨機(jī)VHDL程序如下:--文件名:pl_auto1.vhd。--功能:貨物信息存儲(chǔ)

2012-03-05 15:03:26

寫了很多VHDL文件和testbench文件,在仿真時(shí)信號(hào)的值總是U,請問有誰遇到過這種問題么,怎樣解決,謝謝各位大牛!

2017-09-29 17:20:08

,分別是:Simulator Behavioral Model(功能仿真)、Simulator Post-translate VHDL Model(翻譯后仿真)、Simulator Post-Map

2017-11-28 11:19:34

我有一個(gè)關(guān)于使用spi flash配置Spartan 6的快速問題。根據(jù)spartan 6數(shù)據(jù)表,fpga可以使用典型的行業(yè)標(biāo)準(zhǔn)spi flash進(jìn)行配置。我是否必須對(duì)任何vhdl模塊進(jìn)行編碼以

2019-05-24 13:10:08

大家好,您如何定義VHDL設(shè)計(jì)的功能仿真?謝謝你的幫助!

2020-04-23 10:06:36

2打兩拍systemverilog與VHDL編碼1 本章目錄1)FPGA簡介2)SystemVerilog簡介3)VHDL簡介4)打兩拍verilog編碼5)打兩拍VHDL編碼6)結(jié)束語2 FPGA

2021-07-26 06:19:28

TEXTIO 在VHDL 仿真與磁盤文件之間架起了橋梁,使用文本文件擴(kuò)展VHDL 的仿真功能。本文介紹TEXTIO 程序包,以一個(gè)加法器實(shí)例說明TEXTIO 的使用方法,最后使用ModelSim對(duì)設(shè)計(jì)進(jìn)行仿真,

2009-04-15 10:37:26 35

35 漢明糾錯(cuò)嗎編碼器實(shí)例(VHDL源代碼):

2009-05-27 10:11:15 43

43 剖析硬件描述語言VHDL-AMS 的新特性。通過對(duì)A/D 轉(zhuǎn)換器和D/A 轉(zhuǎn)換器進(jìn)行建模和仿真分析可以看出,VHDL-AMS 突破了VHDL 只能設(shè)計(jì)數(shù)字電路的限制,使得VHDL 可以應(yīng)用于模擬以及混合信

2009-07-08 09:49:23 22

22 本文介紹了可編程邏輯器件(PLD)在雙音多頻信號(hào)的PCM 編碼中的應(yīng)用。從雙音多頻信號(hào)的PCM 編碼到PCM 編碼信號(hào)的輸出,利用CPLD、硬件描述語言VHDL 及MATLAB 來實(shí)現(xiàn)整個(gè)功能,仿真

2009-08-14 11:40:18 44

44 VHDL 包含的語句非常豐富,不同的描述可以實(shí)現(xiàn)同樣功能的電路,但可能在對(duì)資源的利用率上存在差異。根據(jù)應(yīng)用MaxplusⅡ軟件進(jìn)行VHDL 語言代碼編寫的經(jīng)驗(yàn),結(jié)合相應(yīng)實(shí)例,闡述

2009-08-19 11:18:48 28

28 基于公共數(shù)據(jù)結(jié)構(gòu)的EDA仿真波形分析技術(shù):現(xiàn)有的EDA仿真工具缺乏對(duì)仿真數(shù)據(jù)的分析處理功能,影響了仿真分析的效率。本文提出一種基于公共波形數(shù)據(jù)結(jié)構(gòu)的仿真波形自動(dòng)分析技

2009-10-23 16:49:51 21

21 電基于公共數(shù)據(jù)結(jié)構(gòu)的EDA仿真波形分析技術(shù)

摘要: 現(xiàn)有的EDA仿真工具缺乏對(duì)仿真數(shù)據(jù)的分析處理功能,影響了仿真分析的效率。本文提出一種基于公共波形數(shù)

2009-12-07 13:54:16 12

12 給出了一個(gè)利用格雷碼對(duì)地址編碼的羿步FIFO 的實(shí)現(xiàn)方法,并給出了VHDL 程序,以解決異步讀寫時(shí)鐘引起的問題。

2010-07-16 15:15:42 26

26 多功能波形發(fā)生器VHDL程序與仿真

--文件名:mine4.vhd。

--功能:實(shí)現(xiàn)4種常見波形正弦、三角、鋸齒、方波(A、B)的頻率、幅

2008-06-27 10:43:39 3008

3008 步進(jìn)電機(jī)定位控制系統(tǒng)VHDL程序與仿真library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;

entity step_mot

2008-06-27 10:44:32 1738

1738 出租車計(jì)價(jià)器VHDL程序與仿真

--文件名:taxi.hd。--功能:出租車計(jì)價(jià)器。--最后修

2008-06-27 10:49:29 2496

2496

LCD控制VHDL程序與仿真 1. FPGA驅(qū)動(dòng)LCD顯示中文字符“年”程序--文件名:lcd_driver.vhd。--功能:FGAD驅(qū)動(dòng)LCD顯示中文字符“年”。--最后修改日期:2004.3.24。

2008-06-27 11:20:03 1807

1807 LED控制VHDL程序與仿真分別介紹采用FPGA對(duì)LED進(jìn)行靜態(tài)和動(dòng)態(tài)顯示的數(shù)字時(shí)鐘控制程序。1. 例1:FPGA驅(qū)動(dòng)LED靜態(tài)顯示--文件名:decoder.vhd。--功能:譯碼輸出

2008-06-27 11:20:40 1631

1631

編碼波形檢測器電路圖

2009-06-10 10:07:43 2726

2726

用VHDL設(shè)計(jì)專用串行通信芯片

一種專用串行同步通信芯片(該芯片內(nèi)部結(jié)構(gòu)和操作方式以INS8250為參考)的VHDL設(shè)計(jì)及CPLD實(shí)現(xiàn),著重介紹了用VHDL及CPLD設(shè)計(jì)專用通信芯片的

2009-10-12 19:07:48 2154

2154

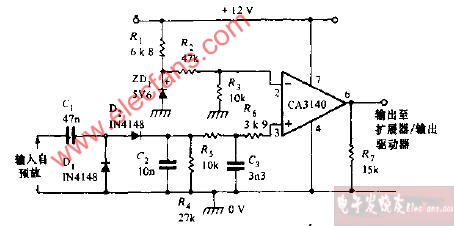

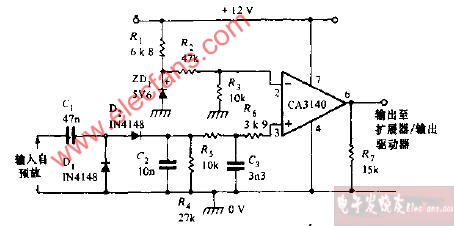

增量光電編碼器基本波形和電路圖

增量編碼器是以脈沖形式輸出的傳感器,其碼盤比絕對(duì)編碼器碼盤要簡單得多

2009-10-29 22:55:06 3578

3578

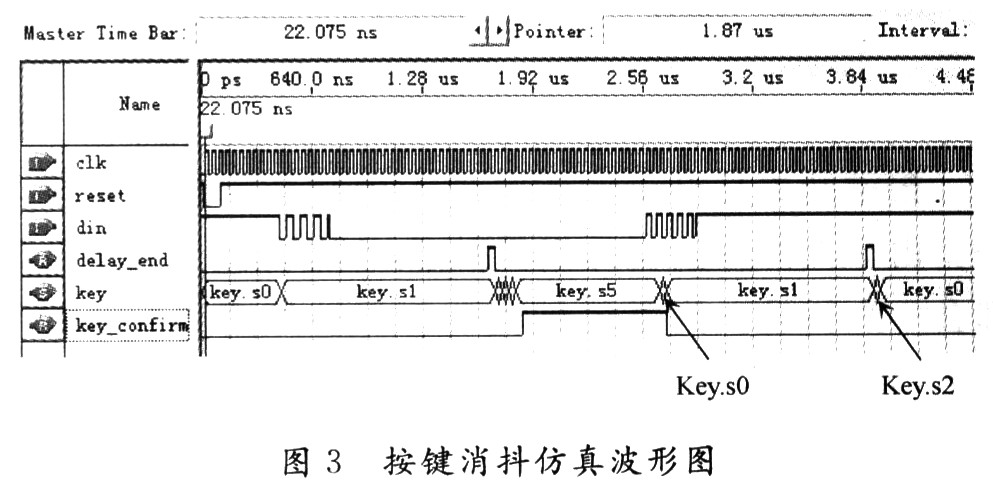

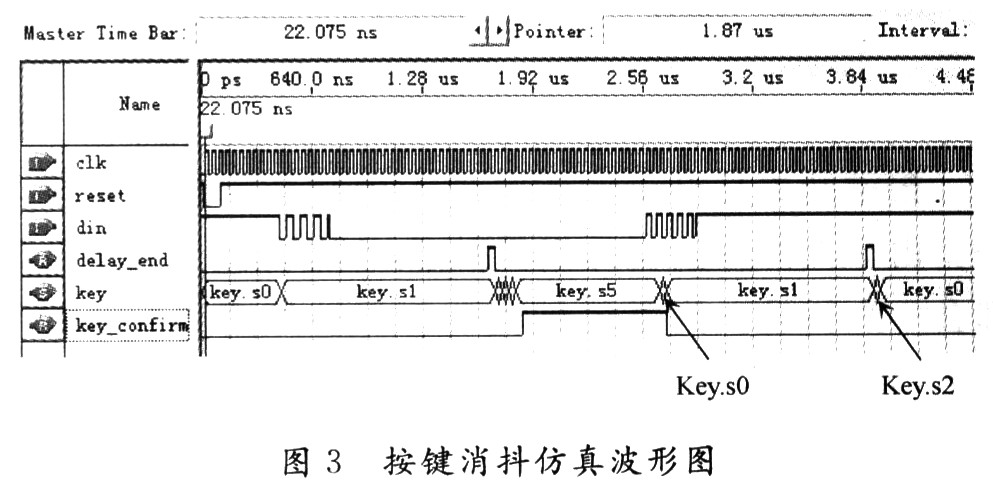

基于VHDL語言的按鍵消抖電路設(shè)計(jì)及仿真

按鍵開關(guān)是電子設(shè)備實(shí)現(xiàn)人機(jī)對(duì)話的重要器件之一。由于大部分按鍵是機(jī)械觸點(diǎn),在觸點(diǎn)閉合和斷開時(shí)都會(huì)產(chǎn)生抖動(dòng)。為避免

2010-01-04 10:39:13 6598

6598

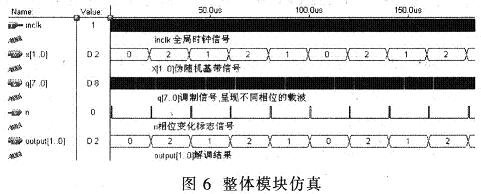

基于VHDL的4PSK的設(shè)計(jì)與實(shí)現(xiàn)

1 引言

實(shí)際通信中的許多信道都不能直接傳送基帶信號(hào),必須使用基帶信號(hào)控制載波波形的某些參量,使得這些參量隨基帶信

2010-02-26 13:23:14 3675

3675

文章在MAX+PLUS II 開發(fā)環(huán)境下采用VHDL 語言設(shè)計(jì)并實(shí)現(xiàn)了電表抄表器討論了系統(tǒng)的四個(gè)組成模塊的設(shè)計(jì)和VHDL 的實(shí)現(xiàn)每個(gè)模塊采用RTL 級(jí)描述整體的生成采用圖形輸入法通過波形仿真下載芯

2011-09-23 17:56:11 40

40 本文主要分析了QuartusⅡ的特點(diǎn)和虛擬仿真軟件的優(yōu)越性,以交通燈控制系統(tǒng)為例,介紹了在虛擬仿真軟件Multisim平臺(tái)上使用VHDL硬件描述語言進(jìn)行程序編寫、電路建模和仿真的方法。

2012-10-25 14:58:31 15207

15207

基于探索電容濾波電路工作波形仿真實(shí)驗(yàn)技術(shù)的目的,采用Multisim10仿真軟件對(duì)電容濾波電路的工作波形進(jìn)行了仿真實(shí)驗(yàn)測試,給出了Multisim仿真實(shí)驗(yàn)方案,仿真分析了濾波電容選取不同

2012-12-17 10:47:08 240

240 文中著重介紹了一種基于FPGA利用VHDL硬件描述語言的數(shù)字秒表設(shè)計(jì)方法,在設(shè)計(jì)過程中使用基于VHDL的EDA工具M(jìn)odelSim對(duì)各個(gè)模塊仿真驗(yàn)證,并給出了完整的源程序和仿真結(jié)果。

2012-12-25 11:19:24 7092

7092 文中詳細(xì)介紹了QPSK技術(shù)的工作原理和QPSK調(diào)制、解調(diào)的系統(tǒng)設(shè)計(jì)方案,并通過VHDL語言編寫調(diào)制解調(diào)程序和QuartusII軟件建模對(duì)程序進(jìn)行仿真,通過引腳鎖定,下載程序到FPGA芯片EP1K30TC144

2013-06-08 17:47:19 92

92 基于vhdl的DDS設(shè)計(jì)

簡單的波形發(fā)生器

可以產(chǎn)生正弦波,方波,三角波,鋸齒波

2016-01-12 17:55:02 31

31 系統(tǒng)地介紹了通信原理MATLAB仿真的基本思想與方法,重點(diǎn)討論了MATLAB對(duì)常見信號(hào)與

線性系統(tǒng)、模擬調(diào)制、模擬信號(hào)的數(shù)字傳輸、數(shù)字信號(hào)的基帶傳輸、數(shù)字信號(hào)的頻帶傳輸、信道容量和編碼以及擴(kuò)頻通信系統(tǒng)的仿真算法、流程與程序編制的思路過程。

2016-03-31 17:09:39 7

7 系統(tǒng)地介紹了通信原理MATLAB仿真的基本思想與方法,重點(diǎn)討論了MATLAB對(duì)常見信號(hào)與

線性系統(tǒng)、模擬調(diào)制、模擬信號(hào)的數(shù)字傳輸、數(shù)字信號(hào)的基帶傳輸、數(shù)字信號(hào)的頻帶傳輸、信道容量和編碼以及擴(kuò)頻通信系統(tǒng)的仿真算法、流程與程序編制的思路過程。

2016-03-31 17:17:55 6

6 DSP之 FSK調(diào)制與解調(diào)VHDL程序及仿真教程,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 17:37:35 12

12 DSP之 PSK調(diào)制與解調(diào)VHDL程序及仿真教程,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 17:42:41 15

15 DSP之MASK調(diào)制VHDL程序及仿真,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 17:42:41 16

16 DSP之MPSK調(diào)制與解調(diào)VHDL程序與仿真,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 17:42:41 4

4 VHDL波形發(fā)生器程序,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 17:17:12 3

3 用VHDL設(shè)計(jì)專用串行通信芯片,下來看看。

2016-12-20 18:02:50 10

10 基于VHDL_AMS的流水線ADC結(jié)構(gòu)式建模方法與仿真_陳世同

2017-01-03 17:41:32 2

2 SPWM波形protues仿真程序 51單片機(jī)SPWM波形產(chǎn)生代碼 protues仿真

2017-01-14 22:32:46 276

276 在編寫verilog模塊后,很重要的一部分就是對(duì)所編寫的模塊進(jìn)行仿真。而在仿真過程中,很重要的一部分就是觀察波形。

2017-09-15 17:40:43 13

13 系統(tǒng)中各點(diǎn)的頻譜和波形,直觀說明了擴(kuò)頻通信的原理。 本文闡述了擴(kuò)頻通信的基本原理,使用Systemview軟件對(duì)擴(kuò)頻通信進(jìn)行仿真設(shè)計(jì)。在仿真設(shè)計(jì)中,我們使用了觸發(fā)器產(chǎn)生PN周期偽隨即序列作為擴(kuò)頻碼,使用2PSK調(diào)制信號(hào)與擴(kuò)頻碼相乘實(shí)現(xiàn)擴(kuò)頻調(diào)制。最后,我們結(jié)

2017-11-10 16:13:24 14

14 文章給出了一種偵測紅外線編碼波形的方法,由單片機(jī)AT89C2051作為前端檢測處理器,通過串行口和通用微機(jī)進(jìn)行通信,由微機(jī)對(duì)編碼波形進(jìn)行顯示、分析、存儲(chǔ),構(gòu)成功能可由軟件擴(kuò)充的紅外線編碼波形的偵測

2017-11-18 11:13:10 10

10 在數(shù)字電路設(shè)計(jì)中(Verilog or VHDL),ModelSim是常用的仿真工具。當(dāng)我們仿真大型的工程時(shí),往往需要保留仿真波形,以便分析和以后查看。這就需要學(xué)習(xí)在ModelSim里面如何保存仿真波形及調(diào)用波形。

2017-11-24 11:13:24 18389

18389 saber仿真電路最主要的就是看電路某些點(diǎn)的電壓電流波形,當(dāng)仿真后,得到波形了,波形如何處理才更好得分析電路呢?下面介紹下。

2017-12-08 11:37:46 26574

26574

將基于VHDL的HDB3編碼用在光纖通信系統(tǒng)中作為誤碼儀測試誤碼的HDB3轉(zhuǎn)換器,能滿足實(shí)際測試的需要。且運(yùn)用基于VHDL的可編程芯片開發(fā)技術(shù)將相關(guān)的信號(hào)處理電路進(jìn)行硬件描述,并用CPLD/FPGA

2018-02-08 04:38:00 13809

13809

在信道編碼研究的初期,人們探索、研究出各種各樣的編碼構(gòu)造方法,其中包括卷積碼。

2018-08-20 16:58:32 6138

6138

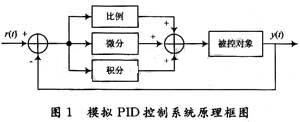

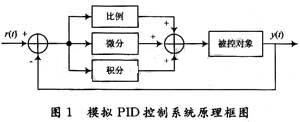

本文介紹VHDL-AMS的新概念和新特性。通過對(duì)PID控制原理進(jìn)行數(shù)學(xué)分析,建立PID控制器的數(shù)學(xué)模型,實(shí)現(xiàn)PID控制器的VHDL-AMS行為級(jí)建模,并進(jìn)行仿真分析。

2018-11-14 08:03:00 4304

4304

根據(jù)編碼方式的不同,音頻編碼技術(shù)分為三種:波形編碼、參數(shù)編碼和混合編碼。一般來說,波形編碼的話音質(zhì)量高,但編碼速率也很高;參數(shù)編碼的編碼速率很低,產(chǎn)生的合成語音的音質(zhì)不高;混合編碼使用參數(shù)編碼技術(shù)和波形編碼技術(shù),編碼速率和音質(zhì)介于它們之間。

2018-11-08 15:52:51 12288

12288 復(fù)習(xí)編碼器的原理,掌握編碼器的設(shè)計(jì)實(shí)現(xiàn)方法,設(shè)計(jì)實(shí)現(xiàn)數(shù)字系統(tǒng)設(shè)計(jì)中常用的8線-3線優(yōu)先編碼器,逐步學(xué)會(huì)熟練運(yùn)用MAX+PLUSⅡ或Quartus II軟件,熟悉EDA的VHDL程序設(shè)計(jì)方法、學(xué)習(xí)掌握

2019-01-29 17:20:49 29

29 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL硬件描述語言入門教程資料免費(fèi)下載包括了:1. VHDL語言基礎(chǔ),2. VHDL基本結(jié)構(gòu),3. VHDL語句,4. 狀態(tài)機(jī)在VHDL中的實(shí)現(xiàn),5. 常用電路VHDL程序,6. VHDL仿真,7. VHDL綜合

2019-04-08 08:00:00 54

54 以函數(shù)信號(hào)發(fā)生器的功能為設(shè)計(jì)對(duì)象,運(yùn)用EDA技術(shù)的設(shè)計(jì)方法,進(jìn)行各種波形的輸入設(shè)計(jì)、設(shè)計(jì)處理,項(xiàng)目校驗(yàn)和器件編程。在VHDL語言的編寫中按照行為描述,寄存器傳輸描述,實(shí)現(xiàn)了兒種波形的軟件設(shè)計(jì)和具體

2019-05-24 14:19:40 3

3 本文檔的主要內(nèi)容詳細(xì)介紹的是使用VHDL語言設(shè)計(jì)比較器與實(shí)時(shí)仿真的資料合集免費(fèi)下載。

2019-06-03 08:00:00 0

0 在VHDL程序中,實(shí)體(ENTITY)和結(jié)構(gòu)體(ARCHITECTURE)這兩個(gè)基本結(jié)構(gòu)是必須的,他們可以構(gòu)成最簡單的VHDL程序。通常,最簡單的VHDL程序結(jié)構(gòu)中還包含另一個(gè)最重要的部分,即庫(LIBRARY)和程序包(PACKAGE)。

2020-04-23 15:43:38 5846

5846 本文檔的主要內(nèi)容詳細(xì)介紹的是通信系統(tǒng)的仿真實(shí)驗(yàn)合集包括了:Systemview操作環(huán)境的認(rèn)識(shí)與操作,濾波器使用及參數(shù)設(shè)計(jì),模擬線性調(diào)制系統(tǒng)仿真,DSB調(diào)制解調(diào)仿真,SSB調(diào)制解調(diào)仿真,輸出信號(hào)頻譜和波形,脈沖幅度調(diào)制系統(tǒng)仿真,基帶傳輸系統(tǒng)眼圖分析與觀察,數(shù)字信號(hào)的載波調(diào)制系統(tǒng)仿真

2020-10-22 17:16:00 38

38 本文檔的主要內(nèi)容詳細(xì)介紹的是FSK的調(diào)制與解調(diào)的VHDL程序和仿真說明。

2020-12-18 16:44:00 25

25 本文檔的主要內(nèi)容詳細(xì)介紹的是CPSK調(diào)制的VHDL程序和仿真資料免費(fèi)下載。

2020-12-18 16:44:16 8

8 本文檔的主要內(nèi)容詳細(xì)介紹的是4個(gè)URAT VHDL程序與仿真的資料合集包括了:1. 頂層程序與仿真,2. 波特率發(fā)生器程序與仿真,3. UART發(fā)送器程序與仿真,4. UART接收器程序與仿真。

2020-12-18 16:44:17 6

6 本文檔的主要內(nèi)容詳細(xì)介紹的是電梯控制系統(tǒng)的VHDL程序與仿真免費(fèi)下載。

2020-12-18 16:46:00 32

32 本文檔的主要內(nèi)容詳細(xì)介紹的是出租車計(jì)價(jià)器的VHDL程序與仿真的資料免費(fèi)下載。

2020-12-21 17:10:58 14

14 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)自動(dòng)售貨機(jī)的VHDL程序與仿真資料。

2020-12-21 17:10:00 24

24 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)自動(dòng)售貨機(jī)的VHDL程序與仿真資料免費(fèi)下載。

2020-12-22 17:07:00 15

15 本文檔的主要內(nèi)容詳細(xì)介紹的是出租車計(jì)價(jià)器的VHDL程序與仿真資料免費(fèi)下載。

2021-01-18 17:17:27 12

12 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)LCD控制的VHDL程序與仿真資料免費(fèi)下載。

2021-01-18 17:19:08 10

10 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)LED控制的VHDL程序與仿真資料免費(fèi)下載。

2021-01-18 17:32:46 12

12 本文檔的主要內(nèi)容詳細(xì)介紹的是TLC5510的VHDL程序與仿真資料免費(fèi)下載。

2021-01-19 14:00:08 13

13 本文檔的主要內(nèi)容詳細(xì)介紹的是DAC0832接口電路的VHDL程序與仿真免費(fèi)下載。

2021-01-19 14:00:00 7

7 本文檔的主要內(nèi)容詳細(xì)介紹的是TLC7524接口電路的VHDL程序與仿真免費(fèi)下載。

2021-01-19 14:00:10 4

4 本文檔的主要內(nèi)容詳細(xì)介紹的是URAT VHDL的程序與仿真詳細(xì)資料說明。

2021-01-19 14:00:14 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是基于VHDL硬件描述語言實(shí)現(xiàn)CPSK調(diào)制的程序及仿真。

2021-01-19 14:34:15 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字頻率計(jì)VHDL程序與仿真的設(shè)計(jì)資料免費(fèi)下載。

2021-01-20 13:44:18 28

28 本文檔的主要內(nèi)容詳細(xì)介紹的是電子時(shí)鐘VHDL的程序與仿真資料免費(fèi)下載。

2021-01-20 13:44:14 36

36 本文檔的主要內(nèi)容詳細(xì)介紹的是電梯控制器的VHDL程序與仿真資料合集免費(fèi)下載。

2021-01-20 13:44:11 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是自動(dòng)售貨機(jī)的VHDL程序與仿真資料免費(fèi)下載

2021-01-20 14:26:00 19

19 本文檔的主要內(nèi)容詳細(xì)介紹的是步進(jìn)電機(jī)定位控制系統(tǒng)的VHDL程序與仿真資料免費(fèi)下載。

2021-01-20 14:26:02 15

15 本文檔的主要內(nèi)容詳細(xì)介紹的是多功能波形發(fā)生器的VHDL程序與仿真資料免費(fèi)下載。

2021-01-20 14:26:00 8

8 前面已經(jīng)講述了VHDL語法和建模,VHDL程序作為硬件的描述語言,可以實(shí)現(xiàn)仿真測試,包括RTL門級(jí)仿真和布線布局后仿真。通過仿真,可以很容易驗(yàn)證VHDL程序以及其描述硬件的正確性。本章將講述如何建立VHDL程序的仿真模型和平臺(tái),以及ⅤHDL語言的具體仿真過程

2021-01-20 17:03:54 14

14 VHDL與Verilog硬件描述語言在數(shù)字電路的設(shè)計(jì)中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設(shè)計(jì)復(fù)雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些小的設(shè)計(jì)中,用

2021-08-04 14:16:44 4725

4725 基于Simcenter Flotherm BCI-ROM技術(shù),Simcenter Flotherm可以進(jìn)行3D電子產(chǎn)品以VHDL-AMS格式進(jìn)行電熱聯(lián)合仿真,同時(shí)電子產(chǎn)品數(shù)學(xué)熱模型可轉(zhuǎn)化為FMU格式

2021-08-13 09:25:59 2876

2876 Modelsim使用技巧—波形白底黑線設(shè)置 在發(fā)表期刊或者論文時(shí),我們需要夾帶modelsim的仿真波形在我們的論文里,在modelsim默認(rèn)模式下的波形一般是黑底綠線白字,如圖1所示。打印出來幾乎

2021-08-26 11:23:12 4738

4738 基于Systemview的脈沖編碼調(diào)制系統(tǒng)仿真(測試測量儀器設(shè)備)-該文檔為基于Systemview的脈沖編碼調(diào)制系統(tǒng)仿真講解文檔,是一份不錯(cuò)的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-30 12:14:10 16

16 目前市面上能支持HDL語言聯(lián)合仿真的電源仿真軟件并不多,能支持VHDL聯(lián)合仿真的就更少了,PSIM軟件支持VHDL及verilogHDL聯(lián)合仿真,這樣對(duì)于快速驗(yàn)證HDL實(shí)現(xiàn)的新想法是十分便捷的。

2023-05-23 11:38:10 5345

5345

的matlab仿真(1) 大學(xué)畢業(yè)設(shè)計(jì)一席談之三十 級(jí)聯(lián)編碼方式下的matlab仿真(2) 大學(xué)畢業(yè)設(shè)計(jì)一席談之三十 級(jí)聯(lián)編碼方式下的mat ? lab仿真(3)測試卷積交織 大學(xué)畢業(yè)設(shè)計(jì)一席談之九 多種編碼方式的通信系統(tǒng)仿真(4) RS碼仿真 大學(xué)畢業(yè)設(shè)計(jì)一席談之

2023-05-25 17:55:01 967

967

使用VCS仿真Vivado里面的IP核時(shí),如果Vivado的IP核的仿真文件只有VHDL時(shí),仿真將變得有些困難,VCS不能直接仿真VHDL

2023-06-06 11:15:35 3578

3578

波形編碼是基于對(duì)語音信號(hào)波形的數(shù)字化處理,試圖使處理后重建的語音信號(hào)波形與原語音信號(hào)波形保持一致。

2024-05-01 17:17:00 4614

4614

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論