51單片機實現數字秒表,有開始,暫停,結束三個獨立按鍵。Proteus仿真圖代碼1.頭文件,定義變量#include#define uchar unsigned char#define uint

2021-11-18 08:38:56

的設計早期就能查驗設計系統的功能可行性,隨時可對設計進行仿真模擬。3.大規模設計一些大型的 FPGA 設計項目必須有多人甚至多個開發組共同并行工作才能實現。VHDL 語句的行為描述能力和程序結構決定了它具有

2018-09-07 09:04:45

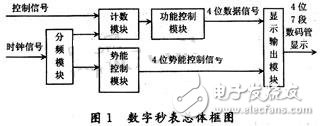

,舉例說明了利用VHDL語言實現數字系統的過程。 整個數字電壓表的硬件結構如圖1所示。 工作時,系統按一定的速率采集輸入的模擬電壓,經ADC0804轉換為8位數字量,此8位數字量經FPGA處理

2012-10-26 15:46:00

用notepad++的關聯設置Lesson07 特權Xilinx FPGA SF-SP6入門指南 -- ISE與Modelsim聯合仿真之庫編譯Lesson08 特權Xilinx FPGA SF-SP6入門

2015-07-22 11:49:20

本帖最后由 eehome 于 2013-1-5 10:08 編輯

Xilinx Fpga前仿真后仿真

2012-08-17 08:50:07

Xilinx Fpga前仿真后仿真

2012-08-15 18:49:38

8章)、VHDL綜合和可綜合的VHDL程序設計技術(第9章)、VHDL基本設計和實用設計(第10、11章)、多種常用的支持VHDL的EDA軟件使用(第12章)、VHDL數字系統設計實踐(第13章

2008-06-04 10:31:29

FPGA正在掀起一場數字信號處理的變革。本書旨在講解前端數字信號處理算法的高效實現。首先概述了當前的FPGA技術、器件以及用于設計最先進DSP系統的工具。第1章的案例研究是40多個設計示例

2023-09-19 06:38:28

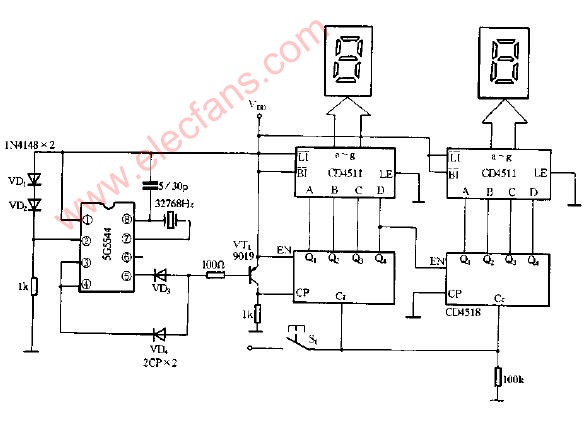

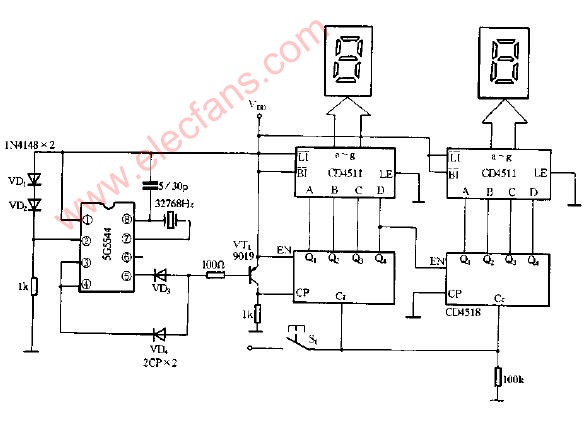

秒表proteus仿真

2015-12-08 23:26:24

UART參考設計,Xilinx提供 (VHDL)DISCLAIMER

2012-08-13 17:51:49

數字示波器的FPGA實現, VHDL語言,測試通過(僅供參考)

2009-11-06 19:53:52

Verilog常用程序示例2.6.1 Verilog基本模塊2.6.2 基本時序處理模塊2.6.3 常用數字處理算法的Verilog實現2.7 本章小結第3章基于Xilinx芯片的HDL語言高級進階3.1 面向

2012-04-24 09:23:33

1.熟悉FPGA架構及應用,熟悉圖像算法的FPGA實現。

2.熟悉verilog vhdl,熟悉Xilinx或Intel等開發工具。

3.有AI算法 fpga實現經驗優先。

4.本科及以上學歷,碩士優先。具有強烈的責任心,執行力,良好的溝通能力和團隊合作能力。

2024-09-02 15:50:50

針對實現DSP的設計軟件—System Generator。在使用FPGA為原型平臺運行算法時,它不僅能夠對硬件的真實情況進行仿真,還能夠自動生成硬件實現所需要的硬件描述語言代碼。與語 言設計相比

2019-06-21 06:25:23

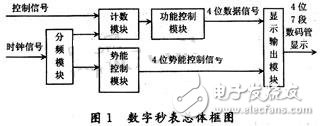

本文介紹了一種基于FPGA利用VHDL硬件描述語言的數字秒表設計方法,

2021-05-11 06:37:32

。下面小編來詳細介紹一下不同仿真模式的區別。 數字電路設計中一般包括3個大的階段:源代碼輸入、綜合和實現,而電路仿真的切入點也基本與這些階段相吻合,根據適用的設計階段的不同仿真可以分為RTL行為級仿真

2018-01-24 11:06:12

盡可能短、實驗成本盡可能低,最好能在實驗室直接驗證設計的準確性和可行性,因而出現了現場可編程邏輯門陣列FPGA。對于芯片設計而言,FPGA的易用性不僅使得設計更加簡單、快捷,并且節省了反復流片驗證的巨額成本。對于某些小批量應用的場合,甚至可以直接利用FPGA實現,無需再去訂制專門的數字芯片。

2019-08-30 08:26:38

本文基于VHDL方式實現了QPSK數字調制解調電路的設計,通過QuartusII軟件建模對程序進行仿真,并通過引腳鎖定,下載到FPGA芯片EP1K30TC144—3中,軟件仿真和硬件驗證結果表明了該

2020-12-18 06:03:26

基于VHDL語言含秒表數字鐘仿真和引腳設置

2012-05-22 23:13:33

設計簡介:本設計是基于單片機的數字秒表的設計,主要實現以下功能:可實現LCD12864顯示時間以及倒計時、順計時等信息;可實現通過按鍵調節調節時間的大小以及實現計時功能;可實現通過通過語音播報目前

2021-12-08 06:31:00

隨著集成電路技術的不斷進步,數字化應用逐漸普及,在數字通信、電力系統自動化等方面越來越多地運用了數字鎖相環。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現了一個全數字鎖相環功能模塊,構成了片內鎖相環。

2019-10-10 06:12:52

今天給大俠帶來在FPGA設計應用中如何在ModelSim中添加Xilinx仿真庫,話不多說,上貨。

注意:ModelSim一定要安裝在不帶空格的目錄下,即不要安裝在“Program

2024-07-03 18:16:38

為開發平臺,采用MATLAB及VHDL語言開發工具,詳細闡述了數字濾波器的實現原理、結構、方法及仿真測試過程,并通過大量工程實例分析其在FPGA實現過程中的具體技術細節。其主要內容包括FIR濾波器

2020-05-12 15:48:28

AC-Link音頻編/解碼原理是什么?怎么實現AC-Link數字音頻VHDL編/解碼的FPGA設計?

2021-05-10 06:46:20

本文介紹一種以FPGA為核心,設計了一種基于FPGA的數字秒表?

2021-05-10 06:40:32

怎樣去設計基于FPGA的數字秒表?如何對數字秒表進行仿真測試?

2021-05-13 07:17:49

本帖最后由 eehome 于 2013-1-5 10:09 編輯

共8章,很全面包括altera和xilinx,兩個公司的FPGA和相關軟件都涉及到,軟件操作,語法點,編碼風格,還有專門一章

2012-12-06 16:10:55

UART 4 UART參考設計,Xilinx提供VHDL代碼 uart_vhdl

This zip file contains the following folders

2009-06-14 08:57:14 114

114 USB接口控制器參考設計,xilinx提供VHDL代碼 usb xilinx vhdl

;? This program is free software; you can redistribute

2009-06-14 09:05:40 45

45 以VHDL實現的數字溫度表本專題主要是在于如何運用硬體描述語言(VHDL) 仿真數字溫度表,以及它如何找出ADC0809 的數位轉換值與AD590 感測實際溫度值的對應關系,并以Al tera MAX+ plusI

2009-11-22 17:52:56 82

82 數字電池EDA入門之VHDL程序實現集

2009-12-07 14:14:57 0

0 多相濾波器組信道化接收機的FPGA 仿真實現趙偉 王靜 李偉偉(大連海事大學 信息工程學院 遼寧 大連 116026)摘要:軟件無線電理論中的信道化接收機理論在多信號同時提取

2009-12-15 15:04:51 33

33 十分鐘學會Xilinx FPGA 設計

Xilinx FPGA設計基礎系統地介紹了Xilinx公司FPGA的結構特點和相關開發軟件的使用方法,詳細描述了VHDL語言的語法和設計方法,并深入討

2010-03-15 15:09:08 179

179 基于LabVIEW的數字仿真實驗平臺的設計

利用虛擬儀器軟件開發平臺,在計算機上通過對前面板和后面板的編寫來完成實驗室及電子課程實驗教學中所涉及的數字

2010-03-30 16:06:57 111

111 摘要:Xilinx ISE集成綜合環境是Xilinx公司的現場可編程邏輯器件數字電路開發工具集,其集成的工具可以使設計人員方便、快速地完成FPGA/CPLD數字電路開發全過程。通過介紹一個16進

2010-05-06 10:27:26 79

79 本文設計了一種在數字通信系統中的數字鎖相位同步提取方案,詳細介紹了本設計的位同步提取原理及其各個組成功能模塊的VHDL語言實現,并在Quartus II開發平臺上仿真驗證通過。本

2010-08-06 14:28:08 64

64 提出一種基于DCT域的數字水印算法,并用FPGA硬件實現其中關鍵部分DCT變換。采用VHDL語言有效設計和實現DCT變換,分析與仿真結果表明:與軟件實現相比,用FPGA實現水印算法具有高

2010-12-28 10:22:14 20

20 LCD控制VHDL程序與仿真 1. FPGA驅動LCD顯示中文字符“年”程序--文件名:lcd_driver.vhd。--功能:FGAD驅動LCD顯示中文字符“年”。--最后修改日期:2004.3.24。

2008-06-27 11:20:03 1807

1807 LED控制VHDL程序與仿真分別介紹采用FPGA對LED進行靜態和動態顯示的數字時鐘控制程序。1. 例1:FPGA驅動LED靜態顯示--文件名:decoder.vhd。--功能:譯碼輸出

2008-06-27 11:20:40 1631

1631

數字秒表電路圖

2009-05-08 14:39:27 6914

6914

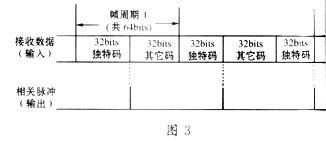

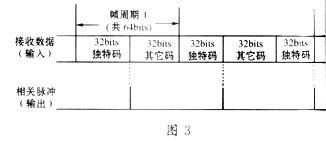

【摘 要】 用VHDL設計了一種32-bit數字相關器,測試和實際應用表明其性能穩定可靠。 關鍵詞:FPGA,VHDL,相關器

2009-05-11 19:47:10 1385

1385

數字電壓表的VHDL設計與實現

介紹數字電壓表的組成及工作原理,論述了基于VHDL語言和FPGA芯片的數字系統的設計思想和實現過程。 關鍵詞:數字電壓表;VHDL語

2009-10-12 19:14:32 2145

2145

TI將數字電源管理應用于Xilinx FPGA設計

德州儀器 (TI) 宣布,Xilinx 在其最新 Virtex-6 ML605 現場可編程門陣列 (FPGA) 評估套件中采用 TI 電源管理技術簡化電源

2009-10-30 08:56:00 679

679 本文采用VHDL描述語言,充分利用Xilinx公司Spartan II FPGA的系統資源,設計實現了一種非對稱同步FIFO,它不僅提供數據緩沖,而且能進行數據總線寬度的轉換。

2011-01-13 11:33:43 2240

2240 Power Expert是一套可以支持Xilinx FPGA設計的最新設計工具,設計數字系統的工程師只要利用這套工具,便可解決仿真電路的設計問題。這個設計工具網頁詳列Xilinx各種不同的FPGA產品以供工程師挑

2011-03-16 14:48:58 137

137 本系統以AES加密算法為例,使用Xilinx SPARTAN 3E為開發平臺,以Xilinx的嵌入式軟核Microblaze為主控制器,調用FPGA的硬件VHDL編程實現的AES加解密和控制CC2420來實現高速有效的數據通信

2011-04-23 11:22:17 2184

2184

利用一塊芯片完成除時鐘源、按鍵、揚聲器和顯示器(數碼管)之外的所有數字電路功能。所有數字邏輯功能都在CPLD器件上用VHDL語言實現。這樣設計具有體積小、設計周期短(設計過

2011-09-27 15:08:56 366

366 本教程主要是向ISE的初學者描述和演示, 在XILINX的ISE集成軟件環境中如何用VHDL和原理圖的方式進行設計輸入如何用 ModelSim 仿真工具對設計進行功能仿真和時序仿真如何實現設計.

2011-11-01 14:44:07 0

0 本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種結構類型的fir數字濾波器的fpga實現、不同結構

2011-11-04 15:50:12 0

0 紹了數字倍頻電路的工作原理,分析了倍頻器產生誤差的原因,然后給出用VHDL語言來實現數字倍頻器的方法,并用Max+plusII通過仿真進行了驗證。

2011-12-07 13:47:30 71

71 為了實現對非相干雷達的接收相參處理,基于數字穩定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設計了一種基于FPGA的DSU硬件實現方法。實驗結果表明基于FPGA的

2012-06-26 15:48:36 27

27 本資料是關于基于Quartus II FPGA/CPLD數字系統設計實例(VHDL源代碼文件),需要的可以自己下載。

2012-11-13 14:03:36 907

907 基于FPGA數字跑表的設計 VHDL語言

2015-10-30 10:39:27 25

25 基于CPLD的VHDL語言數字鐘(含秒表)設計

2015-11-04 15:14:36 9

9 本書比較全面地闡述了fpga在數字信號處理中的應用問題。本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種

2015-12-23 11:07:46 47

47 svpwm的MATLAB仿真實現,利用MATLAB對三相電路進行了仿真,最后成功的仿真除了SVPWM。

2016-04-05 14:16:28 13

13 SVPWM算法仿真實現及分析,有需要的下來看看

2016-04-14 17:06:44 10

10 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設計VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:FM收音機的解碼及控制器VHDL語言實現

2016-06-07 14:13:43 11

11 Xilinx FPGA工程例子源碼:VHDL實現對圖像的采集和壓縮

2016-06-07 14:54:57 6

6 Xilinx FPGA工程例子源碼:USB接口控制器參考設計VHDL代碼(Xilinx)

2016-06-07 14:54:57 21

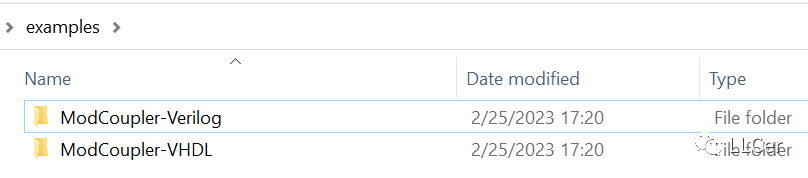

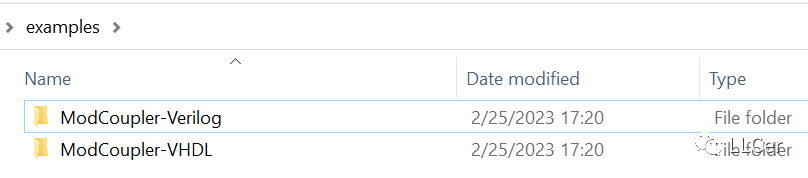

21 Xilinx FPGA工程例子源碼:含Verilog和VHDL版本級詳細說明文檔

2016-06-07 14:54:57 0

0 Xilinx FPGA工程例子源碼:Xilinx DDR3最新VHDL代碼(通過調試)

2016-06-07 14:54:57 77

77 Xilinx FPGA工程例子源碼:Xilinx 提供的頻率發生器的VHDL源碼

2016-06-07 15:07:45 10

10 Xilinx FPGA工程例子源碼:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 38

38 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 33

33 基于8051的Proteus仿真-10秒的秒表

2016-09-06 16:52:29 25

25 基于8051的Proteus仿真-1602LCD顯示的秒表

2022-05-11 17:29:25 39

39 秒表protues仿真 51單片機秒表仿真程序設計 protues秒表仿真設計

2017-01-14 22:32:46 112

112 (Xilinx)FPGA中LVDS差分高速傳輸的實現

2017-03-01 13:12:04 66

66 電子發燒友網站提供《單片機數字秒表仿真(仿真+程序).rar》資料免費下載

2017-06-08 08:00:00 92

92 文中介紹了一種基于FPGA的數字秒表設計方法。采用VHDL硬件描述語言,運用ModelSim等EDA仿真工具。該設計具有外圍電路少、集成度高、可靠性強等優點。最后經實驗驗證,該數字秒表計時準確,輸入

2017-11-18 12:13:01 10629

10629 CCD驅動 電路的實現是CCD應用技術的關鍵問題。以往大多是采用普通數字芯片實現驅動電路,CCD外圍電路復雜,為了克服以上方法的缺點,利用VHDL硬件描述語言.運用FPGA技術完成驅動時序電路的實現

2017-11-24 18:55:51 2079

2079

FPGA仿真篇-使用腳本命令來加速仿真二 基于FPGA的HDMI高清顯示借口驅動 基于FPGA灰度圖像高斯濾波算法的實現 FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:44:00 1728

1728

,再構建成一個完整的基于FPGA設計的數字日歷的頂層模塊,然后對其進行編譯、仿真、引腳鎖定,最終下載到可編程邏輯器件上進行結果驗證。

2019-04-23 08:25:00 5221

5221 應用VHDL語言設計數字系統,很多設計工作可以在計算機上完成,從而縮短了系統的開發時間,提高了工作效率。本文介紹一種以FPGA為核心,以VHDL為開發工具的數字秒表,并給出源程序和仿真結果。

2019-07-24 08:05:00 4908

4908

本文檔的主要內容詳細介紹的是使用FPGA實現自動售貨機的VHDL程序與仿真資料。

2020-12-21 17:10:00 24

24 本文檔的主要內容詳細介紹的是使用FPGA實現自動售貨機的VHDL程序與仿真資料免費下載。

2020-12-22 17:07:00 15

15 本文檔的主要內容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現優化設計。

2021-01-13 17:00:59 26

26 本文檔的主要內容詳細介紹的是使用FPGA實現LCD控制的VHDL程序與仿真資料免費下載。

2021-01-18 17:19:08 10

10 本文檔的主要內容詳細介紹的是使用FPGA實現LED控制的VHDL程序與仿真資料免費下載。

2021-01-18 17:32:46 12

12 前面已經講述了VHDL語法和建模,VHDL程序作為硬件的描述語言,可以實現仿真測試,包括RTL門級仿真和布線布局后仿真。通過仿真,可以很容易驗證VHDL程序以及其描述硬件的正確性。本章將講述如何建立VHDL程序的仿真模型和平臺,以及ⅤHDL語言的具體仿真過程

2021-01-20 17:03:54 14

14 本文檔的主要內容詳細介紹的是使用單片機實現99.9秒秒表的仿真文件免費下載。

2021-03-19 13:48:00 41

41 本文檔的主要內容詳細介紹的是使用單片機實現能預置初值的倒計時秒表的仿真文件免費下載。

2021-03-19 13:48:28 35

35 設計簡介:本設計是基于單片機的數字秒表的設計,主要實現以下功能:可實現LCD12864顯示時間以及倒計時、順計時等信息; 可實現通過按鍵調節調節時間的大小以及實現計時功能; 可實現通過通過語音播報

2021-11-25 17:06:02 39

39 本篇主要介紹Xilinx FPGA的電源設計,主要包括電源種類、電壓要求、功耗需求,上下電時序要求,常見的電源實現方案等。

2022-10-17 17:43:39 8054

8054 基于51單片機數字秒表proteus仿真設計,資料包含仿真及源程序

2023-04-20 16:16:41 2

2 目前市面上能支持HDL語言聯合仿真的電源仿真軟件并不多,能支持VHDL聯合仿真的就更少了,PSIM軟件支持VHDL及verilogHDL聯合仿真,這樣對于快速驗證HDL實現的新想法是十分便捷的。

2023-05-23 11:38:10 5344

5344

OFDM中調制使用IFFT,解調使用IFFT,在OFDM實現系統中,FFT和IFFT時必備的關鍵模塊。在使用Xilinx的7系列FPGA(KC705)實現OFDM系統時,有以下幾種選擇。

2023-07-10 10:50:52 1918

1918

電子發燒友網站提供《模擬電路仿真實現.pdf》資料免費下載

2025-01-21 15:21:00 5

5 電子發燒友網站提供《模擬行為仿真實現.pdf》資料免費下載

2025-01-21 09:24:38 0

0 電子發燒友網站提供《數字電路仿真實現.pdf》資料免費下載

2025-01-21 09:24:38 2

2 電子發燒友網站提供《數模混合電路仿真實現.pdf》資料免費下載

2025-01-21 15:32:26 1

1

電子發燒友App

電子發燒友App

評論