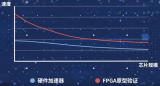

ASIC和FPGA具有不同的價值主張,在作出選擇前必須仔細評估。兩種種技術對比。這里介紹了ASIC和FPGA 的優勢與劣勢。

2011-03-31 17:30:09 5926

5926

S2C Inc.今日宣布將最新的原型驗證平臺Quad V7加入其V7 TAI Logic Module系列。Quad V7 是基于Xilinx Virtex-7 2000T可編程3D IC的最新一代SoC/ASIC原型硬件。

2013-01-23 11:28:14 2747

2747 基于 FPGA 的 ASIC 原型可快速、準確地實現 SoC 系統建模和驗證并加速軟件和固件的開發。Xilinx 推出Virtex?-7 2000T 器件,使基于 FPGA 的原型得到了進一步發展

2013-03-14 14:33:00 2541

2541

RTL代碼驗證工作上,另外軟件的相關開發工作,也會在得到芯片前開始,這2方面都需要借助FPGA原形來模擬芯片的行為,幫助硬件開發和軟件開發者,共同提升工作效率。 FPGA原型在數字芯片設計中,基本是必不可少的,原因非常明顯,相比用

2020-12-30 12:00:13 3715

3715 什么是FPGA原型?? FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能

2022-07-19 16:27:29 2400

2400 FPGA原型在數字芯片設計中非常重要,因為相比用仿真器,或者加速器等來跑仿真,FPGA的運行速度,更接近真實芯片,可以配合軟件開發者來進行底層軟件的開發。這一流片前的軟硬件的協同開發,是其最不可替代的地方。

2023-05-10 10:44:00 11197

11197

國微思爾芯發布3億門原型驗證系統,采用業界最高容量的 Intel? Stratix? 10 GX 10M FPGAs。

2020-09-08 10:56:20 1403

1403 原型驗證---用軟件的方法來發現硬件的問題 在芯片tap-out之前,通常都會計算一下風險,例如存在一些的嚴重錯誤可能性。通常要某個人簽字來確認是否去生產。這是一個艱難的決定。ASIC的產品NRE

2019-07-11 08:19:24

` 本帖最后由 wangjiamin2014 于 2014-7-24 11:21 編輯

事實上,工業市場是一個龐大的市場,任何一款主控芯片都無法完全將其覆蓋。就工業應用領域而言,FPGA憑借

2014-07-24 11:18:05

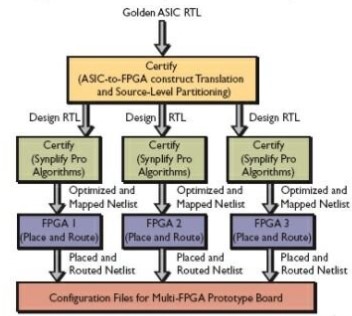

原型驗證過程中的ASIC到FPGA的代碼是怎樣進行轉換的?

2021-05-08 09:16:18

。 ASIC在離開生產線后再也無法改變。這就是為什么設計師在大規模量產之前需要完全確保設計正確無誤。工程師可以利用FPGA的可重配置這一優勢,進行ASIC的原型驗證,以便在將設計發送到代工廠之前,可以在

2020-12-01 17:41:49

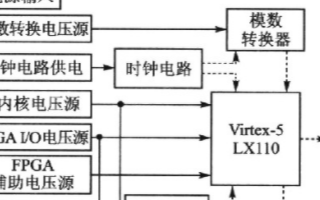

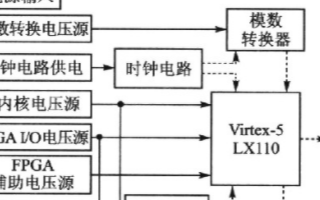

...................................................493.1 Vertex-7 FPGA 資源與架構

2015-09-18 15:26:25

ASIC設計-FPGA原型驗證

2020-03-19 16:15:49

的設計流程(數字芯片)包括:功能描述、模塊劃分、模塊編碼輸入、模塊級仿真驗證、系統集成和系統仿真驗證、綜合、STA(靜態時序分析)、形式驗證。(FPGA 和 ASIC 設計流程)插一句,在 ASIC

2020-09-25 11:34:41

、系統集成和系統仿真驗證、綜合、STA(靜態時序分析)、形式驗證。插一句,在ASIC 設計過程中,往往要用到FPGA 進行原型驗證。FPGA 驗證是進行ASIC 設計的重要環節,其后,還需要引入ASIC

2017-09-02 22:24:53

130 萬,所以最大系統門數為170 萬。結論:FPGA 等效門數估計方法可以是把FPGA 資源基本單元(如LUT+FF,ESB)和實現相同功能的標準門陣列相比得到FPGA 基本單元等效的門數,然后

2012-03-01 10:08:53

Tape Out并回片后都可以進行驅動和應用的開發。目前ASIC的設計變得越來越大,越來越復雜,單片FPGA已不能滿足原型驗證要求,多片FPGA驗證應運而生。本文我就將與大家探討FPGA原型驗證的幾個經典挑戰性場景,(具體應對的辦法,請戳原文。)容量限制和性能要求

2020-08-21 05:00:12

擴展性較好,可以通過增加芯片數量或使用更大容量的芯片來滿足更高的性能需求。而ASIC的可擴展性相對較差,需要重新設計和制造。

驗證和調試 :FPGA的驗證和調試過程相對簡單,可以在系統級進行仿真和測試。而

2024-02-22 09:54:36

以上”.此話的含意是:日隈介紹“集成同等規模的電路(400萬個邏輯門以及8MbitRAM)時,130nm工藝ASIC芯片與40nm工藝FPGA芯片的面積幾乎相等”.如此說來,如果將FPGA微細化到

2012-11-20 20:09:57

節點以上”.此話的含意是:日隈介紹“集成同等規模的電路(400萬個邏輯門以及8MbitRAM)時,130nm工藝ASIC芯片與40nm工藝FPGA芯片的面積幾乎相等”.如此說來,如果將FPGA微細化到

2012-11-07 20:25:53

HAPS(高性能ASIC原型設計系統)是一款基于FPGA的高性能、高容量ASIC原型設計和仿真系統。HAPS是一種模塊化的系統,采用多個FPGA主板以及標準或定制子板,可以多種方式疊加。標準子板

2018-11-20 15:49:49

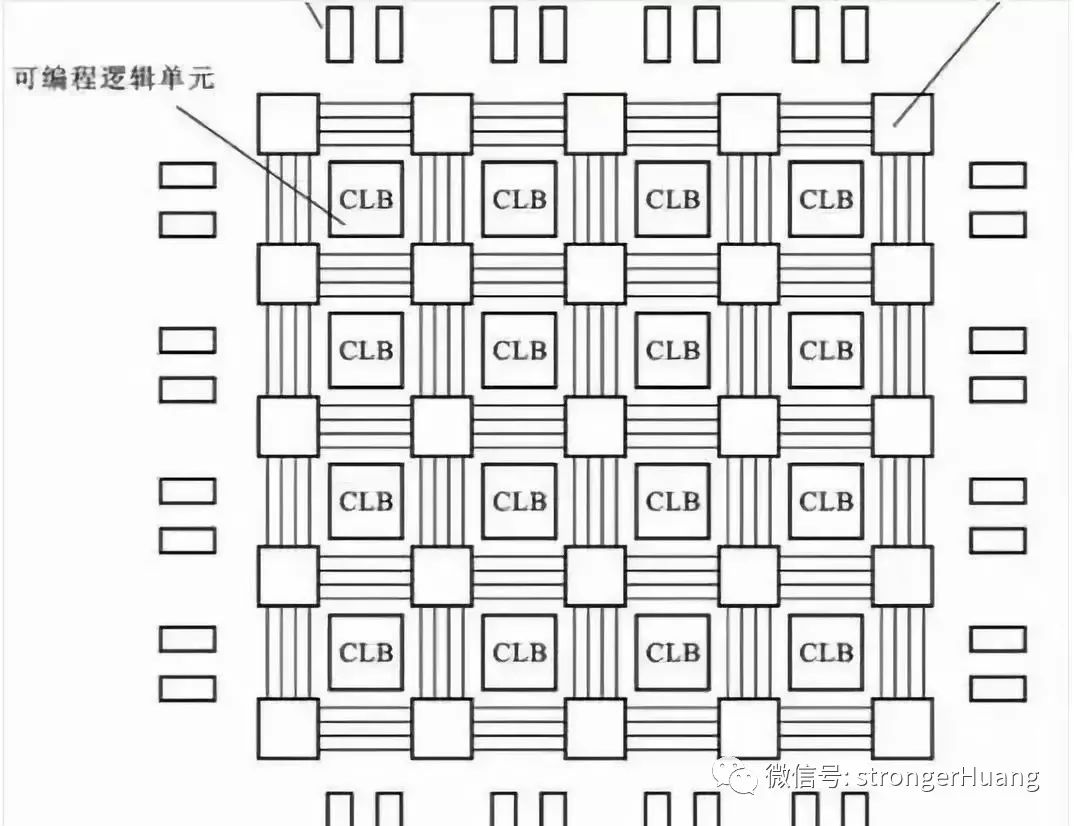

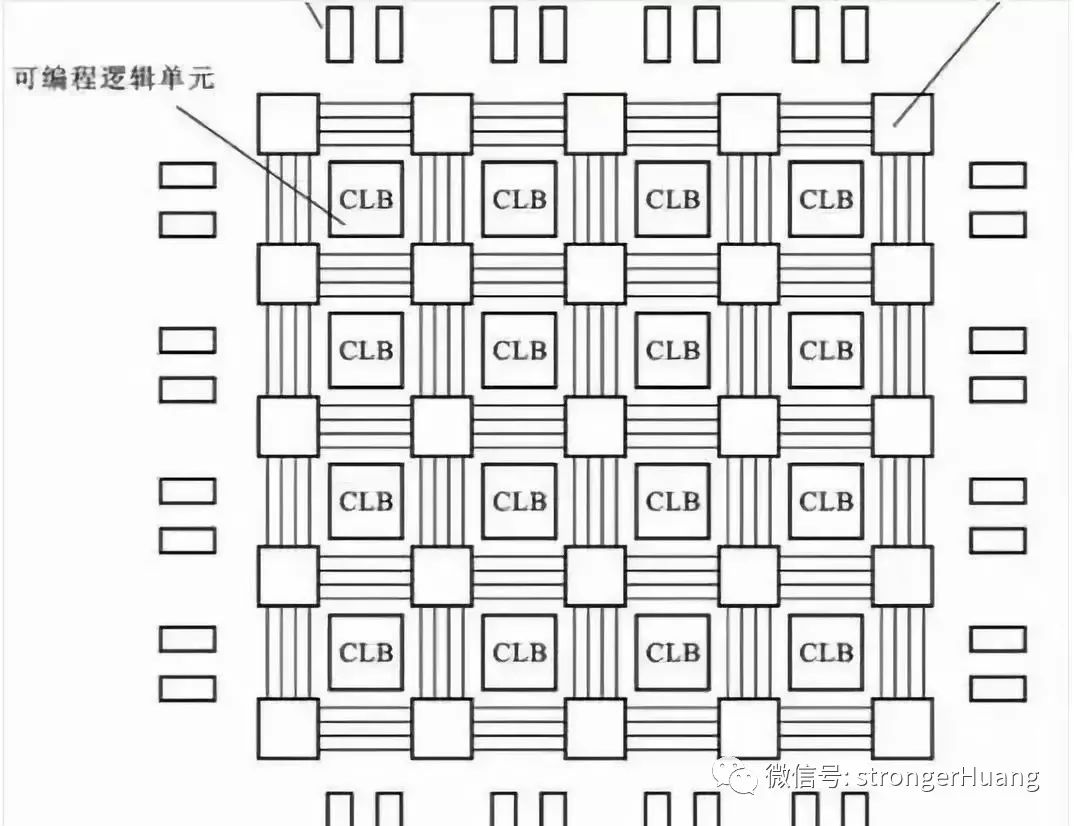

Block)和內部連線(Interconnect)三個部分。FPGA的基本特點主要有: 1)采用FPGA設計ASIC電路,用戶不需要投片生產,就能得到合用的芯片。 2)FPGA可做其它全定制或半

2012-02-27 17:46:03

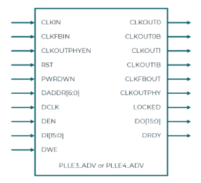

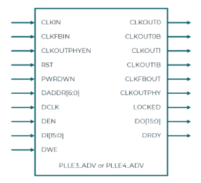

從ASIC到FPGA的轉換系統時鐘設計方案

2011-03-02 09:37:37

最優解。這或許也是為什么深鑒在FPGA原型開發完成之后,還付出了大量努力才能完成真正ASIC設計的原因。 FPGA原型驗證: 食之無味,棄之可惜? 傳統意義上,FPGA出現的一個重要因素是為了給

2023-03-28 11:14:04

Programmable Gate Array,現場可編程門陣列。

FPGA這些年在行業里很火,勢頭比ASIC還猛,甚至被人稱為“萬能芯片”。

其實,簡單來說,FPGA就是可以重構的芯片。它可以根據

2024-01-23 19:08:55

采用基于現場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰之一在于當原型系統未能發揮期望的性能時了解原型系統的內部行為。分析和調試這些設計的一個關鍵因素是難以觀察內部信號。 目前的頂級

2019-07-12 06:38:15

我的設計完全在Verilog中,并且已經使用Spartan FPGA進行了測試。我將源代碼提供給ASIC工廠,以實現作為ASIC使用他們(我認為)的概要工具。我的問題是,有沒有辦法使用任何

2019-07-25 13:44:31

ASIC驗證能夠采用的主要技術是什么?如何利用現成FPGA開發板進行ASIC原型開發?

2021-05-08 07:51:04

FPGA在嵌入式系統中的優勢有哪些?如何通過LabVIEW FPGA加速嵌入式系統原型化?

2021-05-06 07:42:56

的設計和驗證的復雜性需求。隨著原型技術在設計分割以及多 FPGA 聯 合調試領域的進步,基于FPGA 的原型系統不僅可以滿足百萬門級的設計需求,還可以實現設計規模高達15 億門。基 于FPGA

2018-08-07 09:41:23

嗨,我找不到每個頂點-5系列FPGA支持多少個門。你能告訴我如何計算嗎?因為對于我的應用程序,我需要選擇支持150000門的設備。如何在Vertex-5系列中選擇合適的FPGARegardsNanda Kumar M.

2020-06-15 08:49:47

用基于現場可編程門陣列(FPGA)的原型的驗證團隊面臨的最大挑戰之一在于當原型系統未能發揮期望的性能時了解原型系統的內部行為。分析和調試這些設計的一個關鍵因素是難以觀察內部信號。 目前的頂級

2020-07-07 09:08:34

擴展了旗下 16 納米 (nm)Virtex? UltraScale+? 產品系列。VU19P擁有 350 億個晶體管,有史以來單顆芯片最高邏輯密度和最大I/O 數量,用以支持未來最先進 ASIC 和 SoC 技術的仿真與原型設計,同時,也將廣泛支持測試測量、計算、網絡、航空航天和國防等相關應用。

2020-11-02 08:34:50

FPGA、ASIC、GPU 和微處理器以及采用這些及其他數字組件的系統之要求。利用經過驗證的電源管理解決方案設計電源管理電路,將確保項目從一開始就很有把握。這是讓設計方案從原型階段快速進入生產階段的關鍵

2018-10-15 10:30:31

失敗的原因不是時序或者功率的問題,而是邏輯或功能錯誤。為此,功能驗證已經成為ASIC開發周期中一個最關鍵的環節,通常最耗費時間。越來越多的ASIC設計人員發現通過采用FPGA進行功能原型設計能夠最好

2019-07-15 07:00:39

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法。本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。1、RFID芯片的FPGA

2019-05-29 08:03:31

描述XC7A50T-1FGG484C基于最先進的、高性能、低功耗(HPL)、28nm、高k金屬門(HKMG)工藝技術,以2.9Tb/s的I/O帶寬、200萬個邏輯單元容量和5.3TMAC/sDSP

2022-08-03 16:23:43

Xilinx?7系列FPGA包括四個FPGA系列,可滿足整個系統要求,包括低成本,小尺寸,成本敏感的大批量應用程序,可滿足最苛刻的超高端連接帶寬,邏輯容量和信號處理能力高性能的應用程序。7系列

2022-11-10 15:11:11

FPGA 原型設計人員艱苦努力所得的明顯回報就是 ASIC* 設計可以及時而毫無問題地完成產品定案(tape-out)。不過,原型設計還有一點日益重要的優勢,即 ASIC 或 SoC 中嵌入的軟件在項目

2010-01-18 08:35:09 18

18 ASIC和FPGA設計中的多點綜合技術

盡管在技術發展的每一個時刻做出精確的預言是困難的,但ASIC和FPGA所集成的門數仍象數年前INTEL的Gordon Monre預言的那樣平均每18個月增加一倍.

2010-06-19 10:05:09 11

11 Dini推出業界容量最大的基于Altera Stratix III器件的ASIC

Altera公司日前宣布,Dini集團在其業界容量最大的單板FPGA原型引擎中采用了具有340K邏輯單元(LE)的Strati

2008-11-12 10:36:25 631

631 FPGA原型驗證和其他驗證方法是不同的,任何一種其他驗證方法都是ASIC驗證中的一個環節,而FPGA驗證卻是一個過程。由于FPGA與ASIC在結構、性能上各不相同,ASIC是基于標準單元庫,FPGA用的

2010-09-10 17:22:26 1228

1228 HAPS-600系列以高達8100萬ASIC門的容量為各種基于FPGA的更大型的原型驗證項目提供高靈活性和可擴展性。

2011-03-21 10:28:38 1088

1088 電子系統設計人員使用FPGA來實現他們的原型開發,利用器件的可編程能力驗證硬件和軟件。一旦設計準備好進行量產時,設計人員尋找某類ASIC以達到功耗、性能和成本目標,特別是,

2011-03-24 10:21:48 98

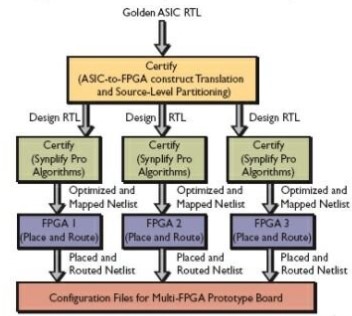

98 對ASIC設計進行FPGA原型驗證時,由于物理結構不同,ASIC的代碼必須進行一定的轉換后才能作為FPGA的輸入。 現代集成電路設計中,芯片的規模和復雜度正呈指數增加。尤其在ASIC設計流程中

2011-03-25 15:16:20 108

108 S2C公司發表最大容量SoC/ASIC原型系統,Quad S4 TAI Logic Module 能夠容納高達3,280萬閘的設計并且擁有 S2C 第4代原型系統的所有優點

2011-04-26 09:40:00 1394

1394 ,用戶可使用多種不同的接口(例如PCIe、千兆以太網、HDMI、LCD和雙A9 ARM處理器)進行SoC原型設計,并通過S2C的Virtex-7 TAI Logic Module系列快速搭建SoC/ASIC原型驗證平臺。

2013-01-30 10:39:43 2032

2032 在 FPGA、GPU 或 ASIC 控制的系統板上,僅有為數不多的幾種電源管理相關的設計挑戰,但是由于需要反復調試,所以這類挑戰可能使系統的推出時間嚴重滯后。不過,如果特定設計或類似設計已經得到電源

2016-11-04 15:57:06 1134

1134 顧名思義,proFPGA 的 Ultra-Scale? XCVU440 FPGA 模塊基于賽靈思 Virtex? UltraScale VU440,而且該原型板的額定容量高達 3000 萬個

2017-02-08 12:12:11 538

538 的 HAPS 系統,采用最新 Xilinx Virtex?-7 FPGA,為使用 HAPS-70 系列的設計人員提供超強容量、性能和先進驗證模式。 借助 HAPS-70 系列,SoC 設計人員將能夠以更快

2017-02-08 14:18:30 915

915 加速 RTI 前的軟件開發。 基于 FPGA 的原型設計,提供精確的周期、較高的執行效率和連接到外部的實際接口。 Synopsys 的混合原型解決方案將虛擬原型和基于 FPGA 的原型優勢集于一身,加速了項目周期中軟件開發和系統集成的進度。 借助 Synopsys 的混合原型驗

2017-02-08 14:32:11 572

572 PLDA集團的990美元XpressK7 PCIe板卡,為系統設計師提供了一個基于賽靈思Kintex-7 FPGA設計或硬件原型的快速部署方法。這個主板支持1代、2代和3代PCIe,同時帶有一個端點卡緣連接器,可以支持多達四個PCIe插槽。

2017-02-10 16:58:10 2668

2668 FPGA原型驗證和其他驗證方法是不同的,任何一種其他驗證方法都是ASIC驗證中的一個環節,而FPGA驗證卻是一個過程。

2017-02-11 12:46:11 3243

3243 ASIC設計在尺寸和復雜性上不斷增加,現代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。

2017-02-11 16:26:11 1342

1342

很多原始設備制造商 (OEM) 已經習慣于依賴現場可編程門陣列 (FPGA) 或ASIC技術來完善現成可用的產品所不支持的功能。這些功能中的其中一個就是與工業用伺服器和AC逆變器驅動中的位置傳感器相對接。使用FPGA和ASIC來支持位置傳感器反饋,增加了系統成本,并且增加了不必要的開發復雜度。

2017-04-26 15:37:41 1992

1992 電子系統設計人員使用FPGA來實現他們的原型開發,利用器件的可編程能力驗證硬件和軟件。一旦設計準備好進行量產時,設計人員尋找某類ASIC以達到功耗、性能和成本目標,特別是,能夠提供硬件平臺和工具包的ASIC,支持目前采用了FPGA的設計

2017-10-14 10:18:11 4

4 )要求一個基于多個FPGA的原型開發板。 在不太遙遠的過去,對ASIC設計團隊而言,在這類情況下主要的解決方案就是在內部建立他們自己的定制多個FPGA的原型開發板。

2017-11-25 09:05:02 1312

1312 可容納2600萬個ASIC門,結合ProtoCompiler設計自動化和調試軟件,可支持高達16億個ASIC門的設計。HAPS硬件與ProtoCompiler軟件的結合,極大地加速了軟件開發、硬件/軟件集

2018-07-10 10:42:00 3139

3139 加利福尼亞州,圣何塞 - 2014年2月25日 - 業界領先的SoC/ASIC快速原型解決方案提供商S2C Inc.于今日宣布,在其基于FPGA的原型平臺V7 TAI Logic Module系列

2018-02-11 14:27:00 4095

4095 近年來,ASIC設計規模的增大帶來了前所未有的芯片原型驗證問題,單顆大容量的FPGA通常已不足以容下千萬門級、甚至上億門級的邏輯設計。現今,將整個驗證設計分割到多個采用最新工藝大容量FPGA中,FPGA通過高速總線互聯,成為大規模ASIC或SOC原型驗證的極佳選擇。

2018-07-02 08:20:00 2166

2166 Dual V7 TAI Logic Module 可在單板上提供高達4000萬ASIC門容量以及1,200個外部I/O。而如此高的門容量,使其成為世界上最緊湊的原型驗證硬件。

2018-07-02 11:50:00 1712

1712 FPGA 原型設計人員艱苦努力所得的明顯回報就是 ASIC 設計可以及時而毫無問題地完成產品定案(tape-out)。

2018-07-19 11:33:00 2818

2818 在不太遙遠的過去,對ASIC設計團隊而言,在這類情況下主要的解決方案就是在內部建立他們自己的定制多個FPGA的原型開發板。然而,今天,使用現成的多個FPGA原型開發板——例如,由Synplicity

2019-05-16 08:07:00 3784

3784

采用fpga原型技術驗證asic設計,首先需要把asic設計轉化為fpga設計。但asic是基于標準單元庫,fpga則是基于查找表,asic和fpga物理結構上的不同,決定了asic代碼需要一定

2019-07-23 08:07:00 2763

2763

FPGA是可編程ASIC。 ASIC:專用集成電路,它是面向專門用途的電路,專門為一個用戶設計和制造的。

2018-12-15 09:58:46 6158

6158 在ASIC的世界里,衡量器件容量的常用標準是等效門。這是因為不同的廠商在單元庫里提供了不同的功能模塊,而每個功能模塊的實現都要求不同數量的晶體管。這樣在兩個器件之間比較容量和復雜度就很困難。

2019-02-16 09:31:02 2812

2812 ASIC芯片一旦流片功能就無法改變,基本專片專用。而FPGA可配置特性就可以應用在功能會改變的場合,例如,原型驗證,ASIC設計過程中會使用到FPGA來進行原型驗證;功能升級,在產品中采用FPGA實現一些業內暫時還沒成熟的解決方案,可以在后續功能變動時方便升級。

2019-08-25 10:40:01 12179

12179

一旦僅用于膠合邏輯,FPGA已經發展到可以在單個器件上構建片上系統(SoC)設計的程度。門和功能的數量急劇增加,以與傳統上僅通過ASIC設備提供的功能相競爭。本文介紹了FPGA設計方法優于ASIC的一些優勢,包括早期上市,輕松過渡到結構化ASIC,以及降低NRE成本。

2019-09-14 12:28:00 2923

2923 在ASIC的世界里,衡量器件容量的常用標準是等效門。這是因為不同的廠商在單元庫里提供了不同的功能模塊,而每個功能模塊的實現都要求不同數量的晶體管。這樣在兩個器件之間比較容量和復雜度就很困難。

2019-08-21 17:55:27 3736

3736 GX 10M FPGA的可插拔FPGA模塊,其每個FPGA模塊基于單顆FPGA,均擁有6000萬個ASIC門的原型設計能力,使得四模塊原型設計系統的仿真容量達到2.4 億個ASIC門。多達九個這樣的四

2019-12-06 15:09:14 2709

2709 從美通社獲知,2020年7月8日,國微思爾芯,全球領先的原型驗證解決方案供應商,推出新系列的原型驗證系統 Prodigy? S7。Prodigy? S7 是國微思爾芯第 7 代原型驗證系統,配備了

2020-07-13 09:32:30 1210

1210 主要驗證選擇是仿真(emulation)、模擬(simulation)和FPGA原型(prototypes)開發。隨著FPGA的門數越來越高,功能越來越強大,使其成為了ASIC驗證的強有力工具。

2020-10-04 12:48:00 2682

2682

主要驗證選擇是仿真(emulation)、模擬(simulation)和FPGA原型(prototypes)開發。隨著FPGA的門數越來越高,功能越來越強大,使其成為了ASIC驗證的強有力工具。

2020-09-30 17:23:03 1452

1452

Virtex UltraScale+ VU19P是賽靈思密度最高的FPGA,是ASIC和SOC原型驗證的最佳選擇。

2020-10-22 14:23:13 2078

2078 國微思爾芯推出VU19P原型驗證系統,加速十億門級芯片設計 新分割引擎顯著提升性能和效率 模塊化、可擴展的單、雙、四核VU19P原型系統,單系統支持高達1億9600萬門ASIC設計 增強的分割引擎

2020-10-23 15:02:18 3161

3161 FPGA_ASIC-一種改進的2D-DCT的FPGA實現(核達中遠通電源技術有限公司招聘文員嗎?)-該文檔為FPGA_ASIC-一種改進的2D-DCT的FPGA實現講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 10:35:54 4

4 將ASIC設計移植到FPGA芯片中,對于大部分設計團隊來講都是巨大的挑戰。主要體現在:ASIC的設計一般都非常大,往往需要做多FPGA芯片劃分;需要支持足夠的處理性能;需要保證其功能的正確性;需要保證移植前后的功能具有等價性。

2022-04-14 15:01:08 2806

2806 其次,部分FPGA開發板也被用在IP和小型芯片設計的開發驗證場景。這部分開發板配備大容量的FPGA芯片,甚至是單板配備多片FPGA芯片來適應開發驗證場景,一般由用戶自己負責手工實現從設計到FPGA功能原型的流程。

2022-04-28 09:38:33 3563

3563 從系統的特性上看,FPGA 原型系統支持多FPGA、自動分割;性能較高的情況下運行系統軟件;仿真加速器的超大容量可以放全芯片的設計,進行全芯片的系統功能/性能/功耗驗證。

2022-05-25 09:35:13 10849

10849 需要門級驗證:FPGA 和 ASIC 一樣需要設計級驗證。但是,FPGA 在門級不是細粒度的,因此它們不需要門級驗證。您將每個門都放置在 ASIC 設計中,因此您需要驗證每個門。

2022-06-20 16:13:05 3402

3402

FPGA vs ASIC 相同點 都設計使用硬件描述語言(HDL),如VHDL或Verilog。但ASIC相比于FPGA開發上,代碼風格更為隨意,因為FPGA是先有電路,后有代碼,ASIC是先有代碼

2022-11-28 10:30:13 2052

2052 FPGA要取代ASIC了,這是FPGA廠商喊了十多年的口號。可是,FPGA地盤占了不少,ASIC也依舊玩得愉快。那么,這兩位仁兄到底有啥不一樣呢?

2023-03-31 14:41:41 2534

2534

FPGA原型驗證在數字SoC系統項目當中已經非常普遍且非常重要,但對于一個SoC的項目而言,選擇合適的FPGA原型驗證系統顯的格外重要

2023-04-03 09:46:45 2074

2074 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2023-04-10 09:23:29 2664

2664 FPGA原型驗證平臺系統靈活性主要體現在其外部連接表現形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統。

2023-04-11 09:50:37 936

936 多片FPGA原型驗證系統的拓撲連接方式各不相同,理想的多片FPGA原型驗證系統應該可以靈活配置,可以使用其相應的EDA工具

2023-05-08 11:51:40 891

891

FPGA原型驗證的原理是將芯片RTL代碼綜合到FPGA上來驗證芯片的功能。對于目前主流行業應用而言,芯片規模通常達到上億門甚至數十億門,一顆FPGA的容量難以容納下芯片的所有邏輯功能。

2023-05-18 12:52:52 1145

1145

多片FPGA的原型驗證系統的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數量受封裝技術的限制,通常只有1000個左右的用戶IO引腳。

2023-05-23 17:12:35 2189

2189

)要求一個基于多個FPGA的原型開發板。 在不太遙遠的過去,對ASIC設計團隊而言,在這類情況下主要的解決方案就是在內部建立他們自己的定制多個FPGA的原型開發板。然而,今天,使用現成的多個FPGA原型開發板——例如,由Synplicity公司的原型開發伙伴生產的開發板——與合適

2023-06-04 16:50:01 2194

2194 2023年6月15日,國內領先的系統級驗證EDA解決方案提供商芯華章,正式發布國內首臺設計上支持超百億門大容量的硬件仿真系統樺敏HuaEmu E1,可滿足150億門以上芯片應用系統的驗證容量。產品

2023-06-15 14:44:28 1221

1221 FPGA和ASIC作為數字電路的常見實現方式,其聯系和區別備受關注。本文將從FPGA和ASIC的基本概念入手,深入研究它們的區別與聯系,以幫助讀者更好地理解兩者的應用場景和選擇方法。

2023-08-14 16:38:51 4330

4330 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2024-01-12 16:13:01 2194

2194 使用預先定制功能即IP核的必要性開始,通過闡述開發ASIC原型設計時需要考慮到的IP核相關因素,用八個重要主題詳細分享了利用ASIC所用IP來在FPGA上開發原型驗證系統設計時需要考量的因素。

2024-08-10 17:13:24 1295

1295

例子,工程師可以從 proFPGA Uno 系統開始進行 IP 或子片上系統 (SoC) 的開發,然后將其重復用于完整的 SoC 和專用集成電路 (ASIC)原型設計。這只需要將 Uno 中的相同

2025-06-30 13:53:59 1694

1694

電子發燒友App

電子發燒友App

硬聲App

硬聲App

5926

5926 2747

2747 2541

2541

3715

3715 2400

2400 11197

11197

1403

1403 18

18 11

11 631

631 1228

1228 1088

1088 98

98 108

108 1394

1394 2032

2032 1134

1134 538

538 915

915 572

572 2668

2668 3243

3243 1342

1342

1992

1992 4

4 1312

1312 3139

3139 4095

4095 2166

2166 1712

1712 3784

3784

2763

2763

2812

2812 12179

12179

2923

2923 3736

3736 2709

2709 1210

1210 2682

2682

1452

1452

2078

2078 3161

3161 4

4 2806

2806 3563

3563 10849

10849 3402

3402

2052

2052 2534

2534

2074

2074 2664

2664 936

936 891

891

1145

1145

2189

2189

2194

2194 1221

1221 4330

4330 2194

2194 1295

1295

1694

1694

評論