ASIC原型驗(yàn)證是整個(gè)驗(yàn)證環(huán)節(jié)中非常重要的步驟之一,也是將ASIC的代碼移植到FPGA平臺(tái)上最重要的原因,本文章的意義在于:

對于系統(tǒng)構(gòu)架師,將幫助他們在選擇商用模擬器還是自行設(shè)計(jì)方案之間做出更好的選擇;

對于邏輯工程師,他們能夠更好的將ASIC設(shè)計(jì)移植到FPGA原型驗(yàn)證平臺(tái)中;

對于驗(yàn)證工程師,其價(jià)值在于如何將現(xiàn)有的測試平臺(tái)移植到新的驗(yàn)證環(huán)境中。

將ASIC設(shè)計(jì)移植到FPGA芯片中,對于大部分設(shè)計(jì)團(tuán)隊(duì)來講都是巨大的挑戰(zhàn)。主要體現(xiàn)在:ASIC的設(shè)計(jì)一般都非常大,往往需要做多FPGA芯片劃分;需要支持足夠的處理性能;需要保證其功能的正確性;需要保證移植前后的功能具有等價(jià)性。

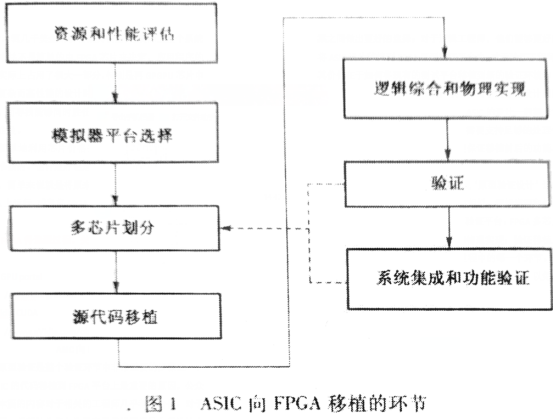

當(dāng)時(shí)ASIC設(shè)計(jì)的移植還沒有出現(xiàn)‘原型驗(yàn)證設(shè)計(jì)’這樣的方法學(xué),但是整個(gè)移植的任務(wù)大致相似:邏輯資源和處理性能評(píng)估:選擇硬件模擬器或者原型驗(yàn)證平臺(tái);FPGA多芯片劃分;RTL源代碼修改;邏輯綜合和物理實(shí)現(xiàn);驗(yàn)證移植后的整個(gè)設(shè)計(jì)。圖1說明了整個(gè)驗(yàn)證過程中的每一個(gè)環(huán)節(jié)。

移植過程的總體原則是盡量少地修改原始設(shè)計(jì),以免產(chǎn)生新的問題。

資源評(píng)估

從任何一個(gè)角度來看,精確的資源評(píng)估都是ASIC移植工作的重點(diǎn)。首先它的結(jié)果將直接影響到硬件模擬器或者原型驗(yàn)證平臺(tái)的選型,其次對于整個(gè)設(shè)計(jì)的多芯片劃分和成本都有直接的影響。資源估計(jì)過少,那么ASIC設(shè)計(jì)就不能完整的移植到FPGA中;而資源估計(jì)過多,則會(huì)導(dǎo)致毫無必要的成本開銷。

對于ASIC資源評(píng)估的不同方法。

性能評(píng)估

性能評(píng)估的結(jié)果,會(huì)直接影響驗(yàn)證方案的選擇,對于大部分的設(shè)計(jì)來說,不可能期望ASIC設(shè)計(jì)在FPGA平臺(tái)上擁有相同的性能指標(biāo)。除了FPGA內(nèi)核本身帶來的性能降低之外,芯片與芯片之間的通信延遲也降低了整體的性能。如果一個(gè)平臺(tái)的性能指標(biāo)能夠達(dá)到ASIC設(shè)計(jì)的幾分之一,那么這個(gè)方案就具有了可行性。但是如果只有原始性能的幾十分之一,很多驗(yàn)證任務(wù)就無法完成。

在多核處理器的SOC芯片中,某些嵌入式操作系統(tǒng)的啟動(dòng)時(shí)間甚至?xí)哌_(dá)5分鐘左右。如果驗(yàn)證平臺(tái)的性能只有十分之一,那么就要耗費(fèi)接近1小時(shí),某些程度上還能接受。但是如果性能只有一百分之一,那么基本上要耗費(fèi)半天來啟動(dòng)這個(gè)操作系統(tǒng)。對于絕大部分的嵌入式系統(tǒng)的驗(yàn)證來講,該方案將變的毫無可行性。

關(guān)于性能評(píng)估的內(nèi)容。

硬件模擬器與原型驗(yàn)證平臺(tái)

選擇硬件模擬器還是原型驗(yàn)證平臺(tái),對于驗(yàn)證團(tuán)隊(duì)來講一直都是長期而艱巨的任務(wù)。最終的選擇需要滿足所有的需求,例如資源容量、整體性能、系統(tǒng)成本、驗(yàn)證范圍及能夠支持的工具等

FPGA多芯片劃分

ASIC設(shè)計(jì)所占用的資源一般非常大,常常需要?jiǎng)澐值蕉囝wFPGA芯片中才能實(shí)現(xiàn)。簡單來說就是將ASIC設(shè)計(jì)的不同部分(一般是以功能模塊為劃分邊界)映射到不同的FPGA芯片中。劃分及優(yōu)化的過程較為復(fù)雜,需要考慮到整個(gè)方案的系統(tǒng)成本、整體性能、資源容量、FPGA芯片之間如何互聯(lián)、劃分的復(fù)雜度等指標(biāo)。

源代碼移植

雖然ASIC和FPGA都是使用相同的RTL編碼方式,但是將適合ASIC芯片的RTL源代碼移植到FPGA芯片中時(shí),需要進(jìn)行相當(dāng)多的重編碼和優(yōu)化工作。特別是ASIC設(shè)計(jì)中的時(shí)鐘樹結(jié)構(gòu),需要正確的分配到FPGA芯片的各種時(shí)鐘資源上,這將是一項(xiàng)非常大的挑戰(zhàn)。

同時(shí),ASIC設(shè)計(jì)中的某些資源,例如晶體管、傳輸門、雙向信號(hào)甚至是模擬電路,在FPGA芯片內(nèi)根本無法找到對應(yīng)的結(jié)構(gòu),因此需要找到其他方式進(jìn)行模擬(替代)。

幾乎所有的ASIC設(shè)計(jì)都會(huì)使用到各式各樣的IP核:從Synopsys Design Ware庫中的簡單功能模塊(大部分模塊都可以使用FPGA結(jié)構(gòu)實(shí)現(xiàn))復(fù)到復(fù)雜的存儲(chǔ)器控制器,PCIE,USB等總線子系統(tǒng),以及CPU內(nèi)核等。像Xilinx這樣的FPGA供應(yīng)商能夠提供許多可替代的對應(yīng)IP核,但并不是所有都可替代。

關(guān)于時(shí)鐘、鎖存器、存儲(chǔ)器、三態(tài)門、組合邏輯及不可綜合電路的移植。

邏輯綜合和物理實(shí)現(xiàn)

完成了代碼移植后,剩下的工作主要就是邏輯綜合和物理實(shí)現(xiàn)。其中包括解決由于ASIC和FPGA綜合工具的差異引起額問題,添加時(shí)序、資源、引腳約束、優(yōu)化工具的參數(shù)設(shè)置,最終達(dá)到時(shí)序收斂。

雖然最新的FPGA工具和設(shè)計(jì)流程和ASIC很相似,但是一些根本性的差異所造成的問題還是需要工程師解決。通常,ASIC綜合工具所支持的Verilog語法要比FPGA綜合工具更加寬松,而且由于設(shè)計(jì)優(yōu)化的目標(biāo)不同,ASIC和FPGA綜合工具所支持的引導(dǎo)語句和工具選項(xiàng)也不盡相同。另外,無論是資源占用還是布線密度,ASIC工具需要處理的工作遠(yuǎn)遠(yuǎn)比FPGA復(fù)雜的多。在某些復(fù)雜的情況下,F(xiàn)PGA工具甚至?xí)o法布局布線。因此某些情況下必須要修改RTL源代碼,甚至是重新規(guī)劃多芯片劃分方案。

驗(yàn)證移植后的設(shè)計(jì)

驗(yàn)證移植后的代碼是整個(gè)過程的最終環(huán)節(jié),其目標(biāo)就是保證移植前后的設(shè)計(jì)在功能上保持一致,并且符合原始的設(shè)計(jì)規(guī)范。驗(yàn)證的方法有基于軟件的功能仿真,基于硬件的模擬器或者原型驗(yàn)證平臺(tái),以及基于純數(shù)字推導(dǎo)的等價(jià)性驗(yàn)證。

系統(tǒng)集成和功能驗(yàn)證

ASIC流片之后,需要進(jìn)行系統(tǒng)集成和功能測試,其主要目的就是保證芯片的功能在整個(gè)系統(tǒng)中能夠正確的運(yùn)行。首先芯片被安置于特殊設(shè)計(jì)的PCB上,測試程序負(fù)責(zé)向芯片注入激勵(lì)向量,芯片的輸出和預(yù)期結(jié)果進(jìn)行比較,以判斷其功能是否正確。整個(gè)硅片的測試基本都是自動(dòng)化的測試過程,并且通常會(huì)在不同的條件下同時(shí)測試硅片。激勵(lì)向量的產(chǎn)生有多種方式:預(yù)先定義的激勵(lì)向量,使用多輸入移位寄存器產(chǎn)生隨機(jī)序列等。當(dāng)其中某項(xiàng)測試失敗時(shí),可以通過硬件模擬器進(jìn)行相同的測試來定位問題的根本原因。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1662文章

22480瀏覽量

638501 -

asic

+關(guān)注

關(guān)注

34文章

1277瀏覽量

124904

原文標(biāo)題:FPGA知識(shí)匯集-ASIC向FPGA的移植

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

深入解析IGLOO2 FPGA與SmartFusion2 SoC FPGA:性能、規(guī)格與應(yīng)用考量

深入解析IGLOO2 FPGA和SmartFusion2 SoC FPGA:特性、參數(shù)與應(yīng)用

Microsemi IGLOO2 FPGA與SmartFusion2 SoC FPGA深度剖析

瑞蘇盈科:FPGA領(lǐng)域的創(chuàng)新者,以技術(shù)實(shí)力賦能FPGA設(shè)計(jì)服務(wù)和解決方案

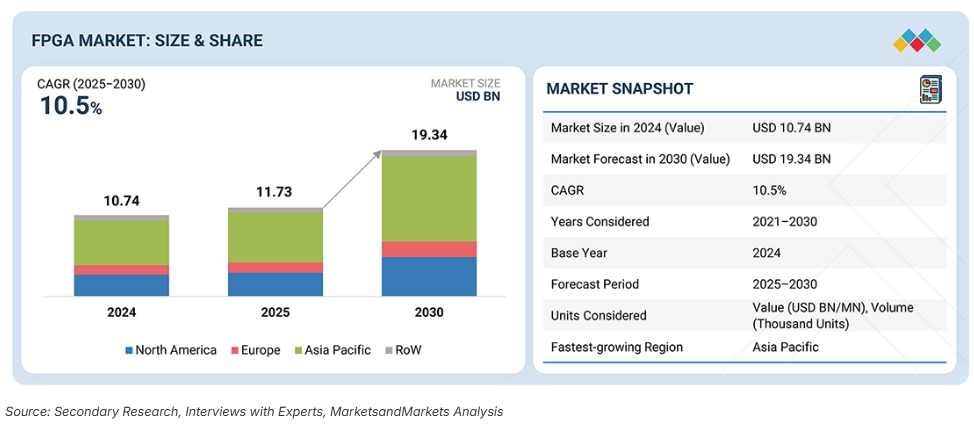

MarketsandMarkets FPGA行業(yè)報(bào)告,2026~2030 FPGA市場洞察

嵌入式與FPGA的區(qū)別

FPGA技術(shù)為什么越來越牛,這是有原因的

Altera Agilex? 3 FPGA和SoC FPGA

西門子桌面級(jí)原型驗(yàn)證系統(tǒng)Veloce proFPGA介紹

智多晶FPGA設(shè)計(jì)工具HqFpga接入DeepSeek大模型

從發(fā)明到 AI 加速:慶祝 FPGA 創(chuàng)新 40 周年

FPGA的定義和基本結(jié)構(gòu)

FPGA芯片的概念和結(jié)構(gòu)

國產(chǎn)FPGA往事

FPGA知識(shí)匯集-ASIC向FPGA的移植

FPGA知識(shí)匯集-ASIC向FPGA的移植

評(píng)論