感謝你對Vivado HLS也就是XILINX’s 高層次綜合解決方案有興趣,這個解決方案綜合c,c++和系統c代碼成Verilog和VHDL RTL結構。

2012-04-25 08:59:37 3141

3141 先給大家簡單快速地介紹一下 Vivado 集成設計環境,即 IDE。當打開 Vivado 工程后,會有一個工程概要,向您介紹工程的設置、警告和錯誤信息以及工程的一般狀態。

2012-04-25 09:00:43 7233

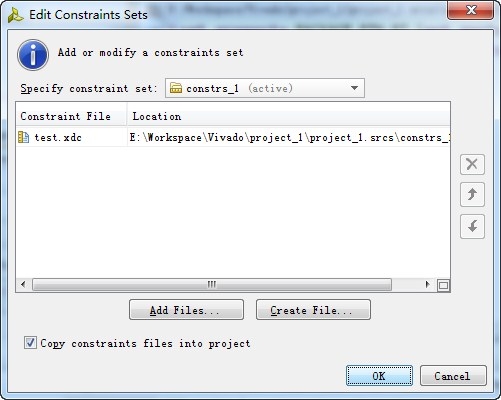

7233 在 Flow Navigator 中點擊設置, 然后選擇Synthesis,或者 selectFlow Settings Synthesis Settings。 如圖1所示: 1、綜合約束 在設置

2020-11-23 14:16:36 6670

6670

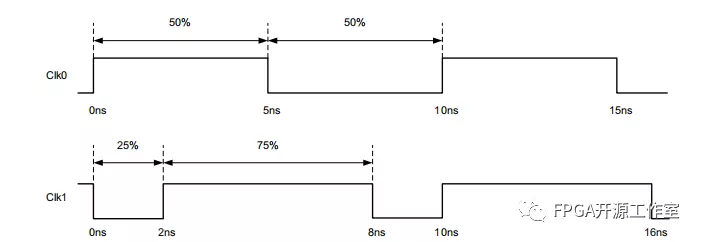

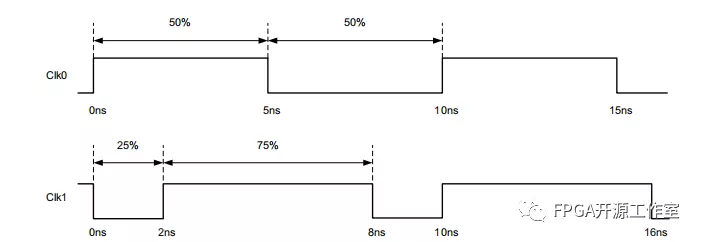

1. 時鐘介紹 在數字設計中,時鐘代表從寄存器(register)到寄存器可靠傳輸數據的時間基準。Xilinx Vivado集成設計環境(IDE)時序引擎使用ClocK特征計算時序路徑要求,并通過

2020-11-29 10:51:45 8525

8525

引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2022-07-25 10:13:44 5970

5970 通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 4432

4432

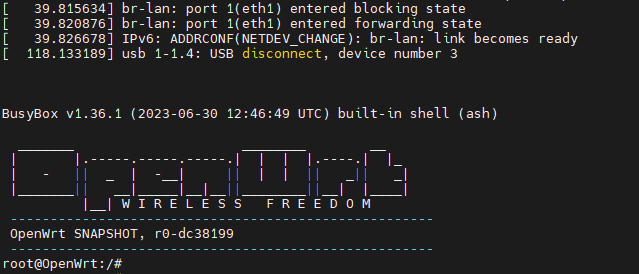

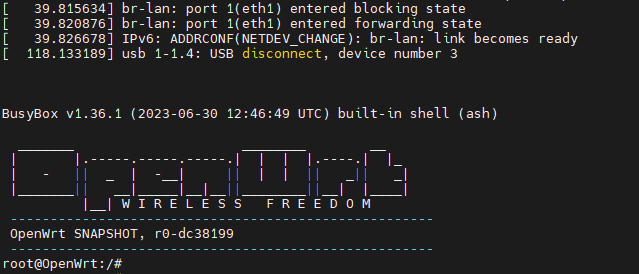

將IMG從weiyun上下載下來,利用U盤燒寫工具,我比較喜歡和習慣Rufus,將openwrt-visionfive2-generic-visionfive2-ext4-sdcard.img燒進TF卡,然后上電啟動。

2023-09-11 12:59:11 2563

2563

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 5117

5117

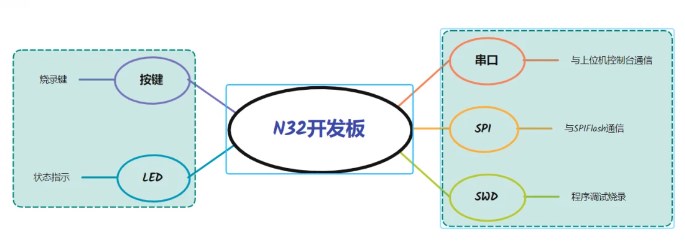

本篇文章主要介紹如何使用UART串口燒寫程序到瑞薩芯片,并以實際項目進行演示。

2023-12-01 13:58:58 1973

1973

本篇文章主要介紹如何使用UART串口燒寫程序到瑞薩芯片,并以實際項目進行演示。

2023-12-01 14:51:27 1712

1712

Vivado概述 / 251.3.1 Vivado下的FPGA設計流程 / 251.3.2 Vivado的兩種工作模式 / 261.3.3 Vivado的5個特征 / 30參考文獻 / 31第2章

2020-10-21 18:24:48

和Vivado的綜合性能,管腳位置與電平約束完全一致。PS:若時鐘和管腳約束直接敲命令,兩者除了語法,沒有明顯區別。6、綜合實現——點評:Vivado默認策略情況下從綜合到生成bit共計23分50秒。而

2021-01-08 17:07:20

1.1 Vivado出現內部異常導致內部異常的原因有很多,但是可行的解決方法有非常直接的,經測試后可行的就是關閉Vivado窗口,再次重新打開。2.Vivado綜合,仿真,實現過程中 出現的問題在

2021-07-31 09:09:20

/ brix用戶所在國家:美國用戶語言:en用戶區域設置:en_USRDI Base根目錄:/ opt / Xilinx / VivadoRDI數據目錄:/opt/Xilinx/Vivado/2016.2

2020-05-20 15:24:42

Vivado綜合可以理解多種多樣的RAM編寫方式,將其映射到分布式RAM或塊RAM中。兩種實現方法在向RAM寫入數據時都是采取同步方式,區別在于從RAM讀取數據時,分布式RAM采用異步方式,塊RAM

2020-09-29 09:40:40

。計數器為26位,led輸出為4位,那么我們將位寬設置好,點擊OK生成IP核。在這里,我們簡要介紹一下Vivado的OOC(Out-of-Context)綜合的概念。對于頂層設計,Vivado使用自頂向下

2023-04-17 16:33:55

本帖最后由 lee_st 于 2017-10-31 08:43 編輯

Xilinx_FPGA下載燒寫教程(超詳細)

2017-10-21 21:00:16

Xilinx_FPGA下載燒寫教程(超詳細)

2017-09-30 08:57:48

Xilinx_FPGA下載燒寫教程(超詳細)Step by step 學習下載配置 Xilinx 之 FPGA配合 Mars-EDA 的 Spartan2 核心板,用圖文方式向大家詳細講述如何下載配置 Xilinx的 FPGA。

2017-10-31 12:16:03

xilinx EDF已經綜合過的網表文件怎樣添加到Vivado工程中?買了一個第三方的IP,給出了端口列表和核心模塊發射機的.edf已經綜合過的網表文件,該網表文件里面富含了大量的信息,我想知道edf文件怎樣添加到Vivado工程中去?要不然的話,總是提示核心模塊實例化失敗!

2016-09-07 11:34:10

我用xilinx spartan-6fpga 它硬核的管腳是固定的還是可配置的我在xilinx提供的文檔里找不到關于硬核管腳的分配求指導

2012-08-11 09:28:44

使用xilinx spartan6,在工程中使用原語生成DDR控制器mig文件,DDR數據管腳定義發生改變,需要重新分配管腳,求告知,這個管腳分配要怎么弄

2016-07-19 09:54:37

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述GTX/GTH收發器時鐘

2021-11-11 07:42:37

使用OTG接口燒寫方式也可以成為fastboot 燒寫方式,下面介紹OTG方式燒寫時 所使用的硬件和軟件平臺,然后再給大家介紹燒寫過程的相關步驟,使用win10系統。硬件平臺使用串口線連接開發板串口

2022-01-10 06:36:59

是管腳的分配也必須在設計代碼出來之前完成。所以,管腳的分配更多的將是依賴人,而非工具,這個時候就更需要考慮各方面的因素。 綜合起來主要考慮以下的幾個方面: 1 、 FPGA 所承載邏輯的信號流向。 IC

2012-08-11 10:27:54

的 BANK 中。 2、 掌握 FPGA 內部 BANK 的分配的情況。現在 FPGA 內部都分成幾個區域,每個區域中可用的 I/O 管腳數量各不相同。在 IC 驗證中都是采用了ALTERA 與XILINX系列

2017-03-25 18:46:25

=FLASE繞過PAR的檢查,這樣就只是將本該接入專用時鐘管腳(或者叫做全局時鐘管腳)的信號,接到了普通IO口上,但并沒有做好如何用普通IO口來引入全局時鐘,Xilinx官方論壇上更是有老外直接指出這只

2019-07-09 08:00:00

求助大神!!!FPGA對于DDR3讀寫,FPGA是virtex6系列配置MIG IP 核時,需要管腳分配1.原理圖上dm是直接接地,管腳分配那里該怎么辦2.系統時鐘之類的管腳分配,是需要在原理圖上找FPGA與DDR3之間的連線嗎?還是?

2018-03-16 18:45:10

文件自動完成FPGA硬件電路的燒寫。這樣就不必每次調試軟件之前都需要重新打開vivado工程下載bitstream,可以更加方便地進行嵌入式軟件開發。

首先打開vivado工程,綜合,實現

2025-10-29 08:21:12

在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是

2015-01-06 17:38:22

。下面小編來詳細介紹一下不同仿真模式的區別。 數字電路設計中一般包括3個大的階段:源代碼輸入、綜合和實現,而電路仿真的切入點也基本與這些階段相吻合,根據適用的設計階段的不同仿真可以分為RTL行為級仿真

2018-01-24 11:06:12

當我試圖在Ubuntu的Synplify中調用xilinx for P& R時,它說XILINX變量尚未設置。我把它分配到vivado中的bin文件夾,但似乎是錯誤的。看起來Synplify

2018-12-19 11:04:40

如何通過設置boot引腳來實現ISP串口燒寫?

2021-12-06 07:16:07

前 言本文主要介紹HLS案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

CLOCK_DEDICATED_ROUTE FALSE [get_nets IOBUF_jtag_TCK/O]

8)綜合成功

9)燒寫板卡

燒寫到FPGA板卡后,第二個LED應該會亮。固化根據

2025-10-31 08:46:40

親愛的大家,我現在正在使用Vivado 2013.3。我試圖將PL結構時鐘從1 MHZ更改為500KHZ。 (1 MHZ下沒問題)但是,Vivado在運行綜合時崩潰了。對我來說減少PL結構時鐘非常重要,因為我打算在一個時鐘周期內收集更多的XADC數據。我該怎么辦?謝謝!

2020-03-25 08:40:07

常用三星單片機燒寫電壓設置參考表

燒寫電壓說明:Vdd 電壓指燒寫時加載到芯片Vdd 端子的邏輯電壓,Vpp 電壓指燒寫時加載到芯片Vpp(Test)端子的編程電壓, Vpp

2010-04-13 15:08:02 25

25 基于TMS320F2812內部Flash在線燒寫技術,提出了一種串口燒寫Flash技術。詳細論述了燒寫技術的實現步驟,給出了關鍵部分的程序代碼。通過對比發現,基于JTAG接口燒寫技術常用于調試

2010-12-20 17:02:57 57

57 1. 使用 SOC 平臺進行開發時,可以將SOC 平臺上的 25AA320 模塊插到燒寫器座上燒寫 2. 如果需要從 J1 口燒寫模塊,首先請確認25AA320 已焊在模塊上,并將燒寫器與模塊 下圖連接,下載線的

2011-06-01 17:53:25 34

34 本文闡述了一種針對TMS320VC5509A DSP 簡單有效的Flash 燒寫方法, 并提出了程序自舉引導的實現方法。可以有效地解決程序代碼存儲問題和DSP 脫機自舉問題.

2011-09-16 14:43:35 16391

16391

電子發燒友網站提供《藍牙燒寫軟件.rar》資料免費下載

2012-09-08 19:07:05 21

21 在OK6410上燒寫ucos ii 方法

2015-10-29 10:55:34 0

0 STC燒寫軟件,自己大學整理收集的文檔等相關資料,大家有需要的,就下載吧。

2015-10-29 10:55:00 14

14 單片機燒寫軟件,單片機燒寫軟件,單片機燒寫軟件

2015-12-09 18:40:56 18

18 DSP最新燒寫插件,很好的DSP自學資料,快來學習吧。

2016-04-15 11:36:12 6

6 最新燒寫插件,有興趣的同學可以下載學習

2016-04-27 17:12:18 9

9 很好用的EEPROM燒寫軟件

2016-12-17 16:09:22 11

11 普中科技燒寫軟件,推薦大家使用!絕對好用!!!

2017-01-24 15:24:13 64

64 Xilinx的JTAG電纜可以通過FPGA“直接”燒寫SPI/BPI。很多對xilinx開發環境不熟悉的用戶,如果第一次接觸這種燒寫模式可能會有疑惑,FPGA是如何做到JTAG和Flash之間的橋接

2017-02-08 02:40:11 10305

10305

如果用戶打算查看芯片是否已經programed,可以通過Blankcheck進行空片檢查。需要特別提醒的是,因為OTP是只能燒寫一次的,所以建議先燒寫幾片,測試確保燒寫的腳本沒問題后,再進行大批量的燒寫,避免造成損失。

2017-09-18 09:50:47 21

21 什么是燒寫 燒寫就是將寫好的程序編譯好形成HEX或BIN文件后,將這個程序寫進單片機芯片的過程就叫燒寫,是沿用最早的單片機只能一次性寫入,因此就叫做燒寫,后來有了紫外線可擦除的EEPROM,現在有了

2017-10-14 10:47:31 7906

7906 的FS2410及Flash燒寫工具為例進行講解,不同廠商的開發板都會提供相應的Flash燒寫工具,并有相應的說明文檔,請讀者在了解基本原理之后查閱相關手冊。 2.實驗內容 (1)熟悉開發板的硬件布局。 (2

2017-10-18 17:03:48 6

6 ,參考使用手冊 3.6小節安卓ADB功能介紹。 另外還需要使用Mfgtools-Rel-1.1.0_121218_MX6Q_UPDATER_V2.0工具。該工具 是光盤02編譯器以及燒寫工具\燒寫工具下

2017-11-16 03:27:00 14047

14047

,用來進行通信下載程序和數據;;對自己搭建的電路板來說,仍會有MAX232芯片和RS232串口用來實現程序的燒寫,實現對單片機寫入數據和程序的下載。用的是RS232串口實現的程序燒寫!若要用USB來燒寫,需要一個相應的ISP下載軟件和硬件燒寫器,一般這種燒寫器價格不菲。用的是USB口實現燒寫程序!

2017-11-16 11:18:37 60282

60282

使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實現浮點復數QRD矩陣分解并提升開發效率。使用VivadoHLS可以快速、高效地基于FPGA實現各種矩陣分解算法,降低開發者

2017-11-17 17:47:43 4363

4363

在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其時鐘分配樹結構如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 12586

12586

這個燒寫方式,是ESP8266無線模塊針對于Arduino開發的一種燒寫方式,可以方便的在Arduino IDE上對ESP8266進行透傳燒寫或者其他模式的燒寫。

2017-11-23 15:41:27 52009

52009

本文為大家帶來仿真器和燒寫器的介紹。

2018-01-05 14:10:19 24585

24585 什么是單片機燒寫軟件? 什么是單片機燒寫軟件? 簡單點說,就是把你寫好代碼(C或者是匯編)專程的機器語言通過一定的方式下載到單片機中。稱為燒寫。 燒寫軟件很多,方式也很多,主要看你的單片機型號.

2018-04-14 11:04:01 35362

35362 燒寫器也叫燒錄器、編程器。在臺灣,燒寫器也叫燒錄器;在大陸,客戶之所以叫它為“編程器”,是因為現在英文名為PROGRAMMER,這個英文名與一般編寫軟件程式的設計師同名,所以就叫“編程器”。燒寫器

2018-04-17 14:05:01 34156

34156 本文介紹一下xilinx的開發軟件 vivado 的仿真模式, vivado的仿真暫分為五種仿真模式。 分別為: 1. run behavioral simulation-----行為級仿真,行為

2018-05-29 13:46:52 9080

9080 本文檔的主要內容詳細介紹的是MicroBlaze(Vivado版)設置說明詳細資料免費下載開始IP綜合設計(步驟)

1、在工作流導向面板中的IP Integrator中,點擊Create

2018-09-05 08:00:00 0

0 本文檔的主要內容詳細介紹的是STM32時鐘系統時鐘樹和時鐘配置函數介紹及系統時鐘設置步驟資料。

2018-10-11 08:00:00 22

22 本文檔的主要內容詳細介紹的是UV4單片機燒寫軟件免費下載

2018-10-08 08:00:00 76

76 本文通過一個簡單的例子,介紹Vivado 下的仿真過程。主要參考了miz702的教程,同時也參考了Xilinx的ug937, xapp199.。

2018-11-10 10:53:51 38382

38382 本文檔的主要內容詳細介紹的是FlyMcu STM32程序ISP串口燒寫軟件資料免費下載。

2018-11-08 08:00:00 34

34 了解如何使用Vivado設計套件的電路板感知功能快速配置和實施針對Xilinx評估板的設計。

2018-11-26 06:03:00 3838

3838 在Vivado Design Suite中,Vivado綜合能夠合成多種類型的屬性。在大多數情況下,這些屬性具有相同的語法和相同的行為。

2019-05-02 10:13:00 4772

4772 本文檔的主要內容詳細介紹的是STC ISP下載燒寫軟件v6.85應用程序免費下載。

2019-03-25 17:27:48 32

32 本文檔的主要內容詳細介紹的是JLINK_V8固件燒寫經常會碰到那些常見的錯誤。

2019-08-16 17:32:00 4

4 從 Vivado 2019.1 版本開始,Vivado 綜合引擎就已經可以支持增量流程了。這使用戶能夠在設計變化較小時減少總的綜合運行時間。

2019-07-21 11:02:08 2129

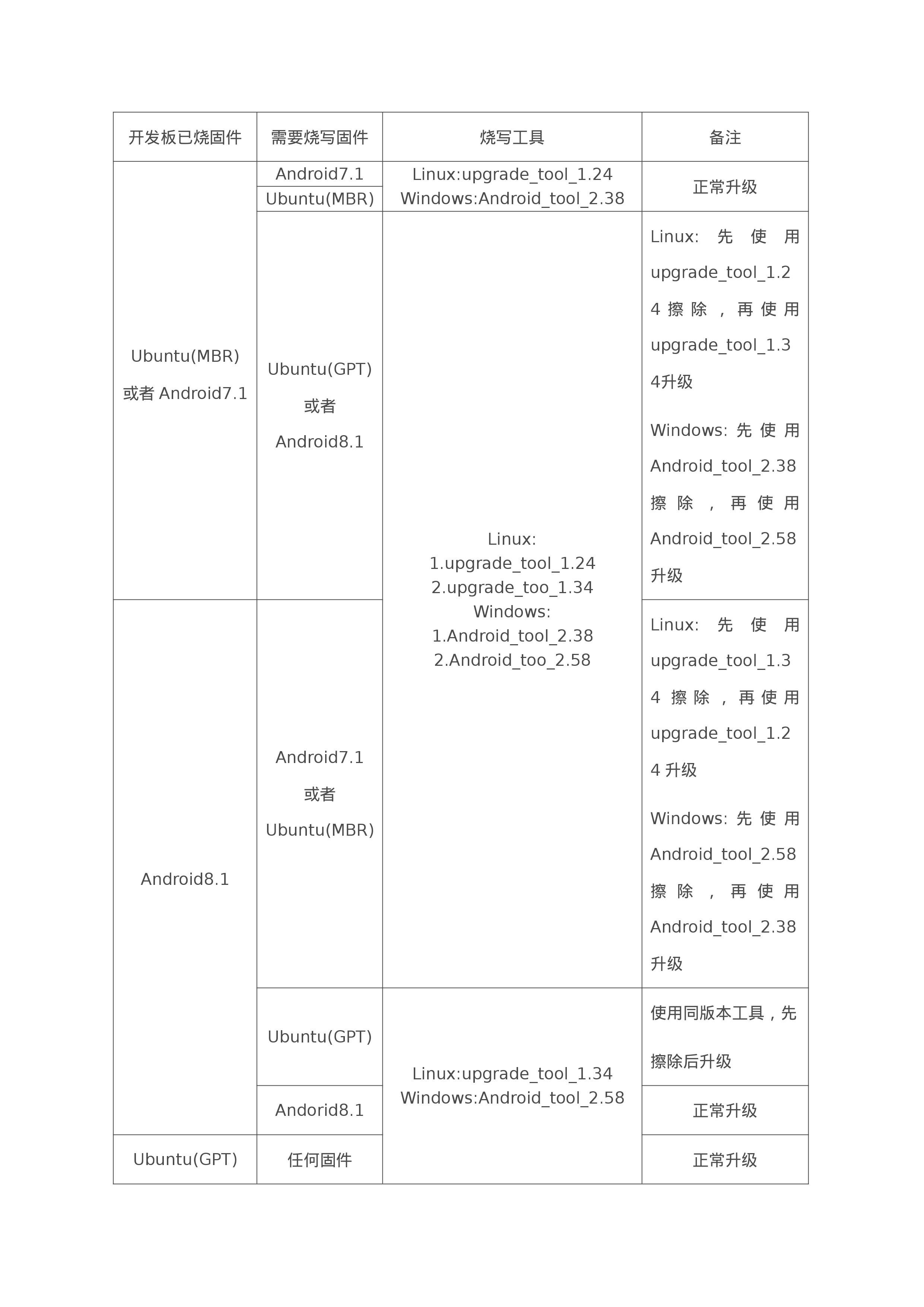

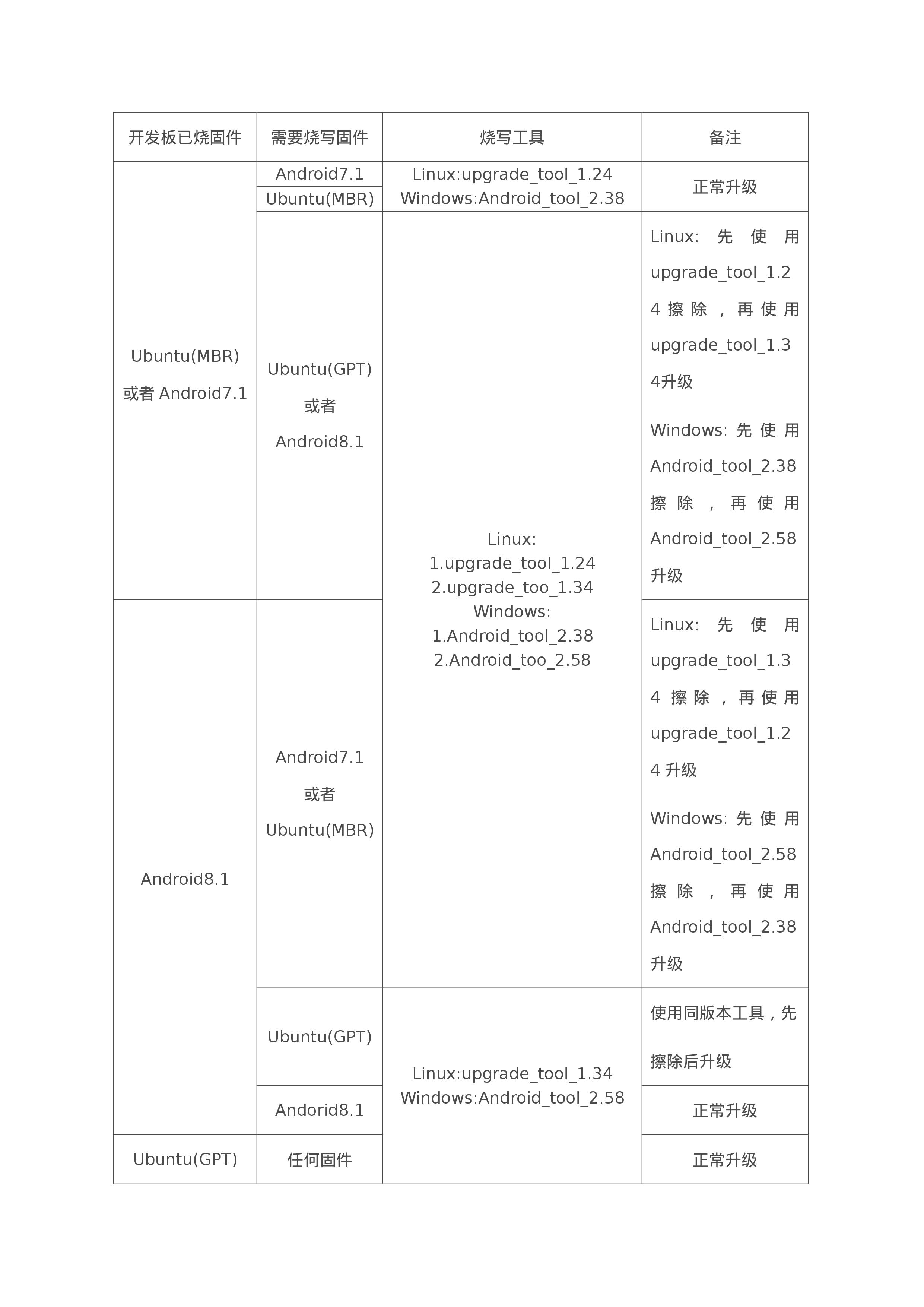

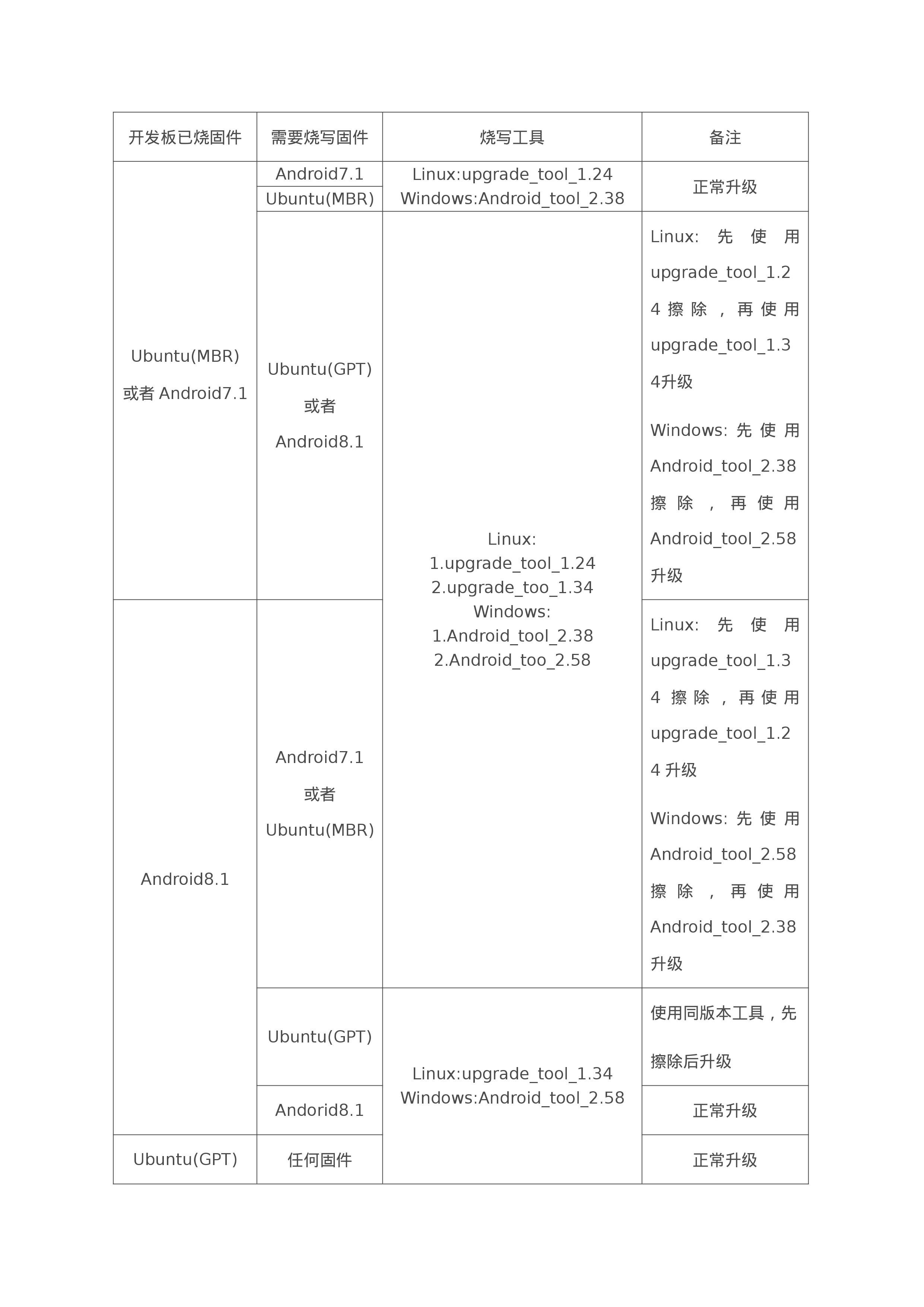

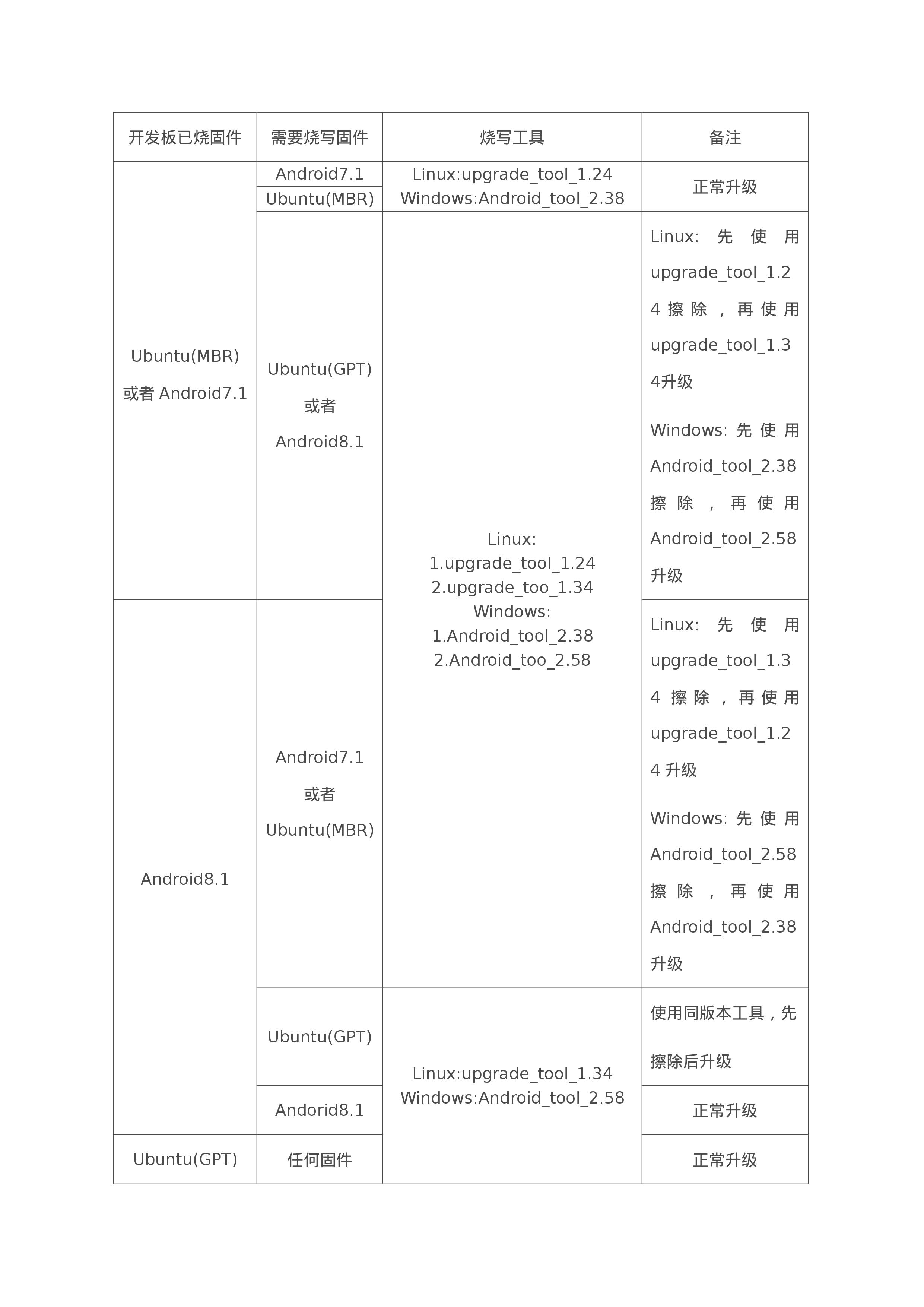

2129 燒寫工具下載地址(根據下表下載對應版本)

upgrade_tool

Android_tool

2019-11-23 11:43:58 2883

2883

請認真閱讀本章再對EMMC進行燒寫!!!

2019-12-20 11:16:29 2086

2086

燒寫 SD 卡 下面我們將介紹如何燒寫固件到 SD 卡。關于固件的類型說明可以看這里。 以下是支持的系統列表: Android 7.1.2 Android 8.1.0 Ubuntu 18.04

2019-12-23 15:20:14 4357

4357 本文檔的主要內容詳細介紹的是emmc啟動燒寫的詳細資料說明。

2020-03-12 16:43:04 29

29 1 I/O延遲約束介紹 要在設計中精確建模外部時序,必須為輸入和輸出端口提供時序信息。Xilinx Vivado集成設計環境(IDE)僅在FPGA邊界內識別時序,因此必須使用以下命令指定超出這些邊界

2020-11-29 10:01:16 6236

6236 Xilinx_Vivado_zynq7000入門筆記說明。

2021-04-08 11:48:02 71

71 Vivado 的XDC設置輸出延時 Vivado 的XDC設置輸出延時,用于輸出伴隨時鐘和數據的,數據是由系統時鐘125M驅動,伴隨時鐘是由125M經過Pll相位移動-90度。 設置輸出時鐘

2021-06-09 17:28:01 5014

5014

文章目錄一、使用flymcu燒寫程序一、使用flymcu燒寫程序燒寫程序之前要使ASP指示燈保持強亮狀態,同時要保證使flashIsp模式下也就是燈閃一下模式

2021-10-26 11:06:08 18

18 NODEMCU V3燒寫 AT固件NODEMCU V3燒寫AT指令固件,保存配置圖。1.AT固件 AiCloud 2.0 AT(32mbit) 2.刷寫工具 flash download tools 3.6.4 3.串口調試工具 sscom v5.13.1 打包下載地址燒寫配置截圖。...

2021-10-28 12:36:11 19

19 atmega168P燒寫bootloader燒寫bootloader的方法大體分為兩種:方法一:使用Arduino IDE燒寫中文教程使用另一塊arduino給我們對Markdown編輯器進行了一些

2021-11-15 19:36:03 22

22 ,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據 Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 ST-link下載器燒寫程序使用專門的編程器/調試器,具有下載功能和調試功能,還可以和IDE結合,實現一鍵下載和調試。這種接口是通過引腳直連ARM內核的,擁有較高的權限。實物圖:引腳圖:1. SWD

2021-12-07 10:51:12 16

16 大多數玩單片機的人都知道Jlink可以燒寫Hex文件,作為ARM仿真調試器,但是知道能燒寫SPI Flash的人應該不多,本篇文章將介紹如何使用JLi...

2022-01-26 18:37:40 4

4 為方便客戶針對 S698 芯片外接不同種類的 FLASH 進行在線編程。V8mon 的 FLASH

燒提供源碼寫可以進行用戶自行修改。FLASH 燒寫驅動實際是一段可下載運行的 SPARC

架構

2022-06-08 14:39:33 0

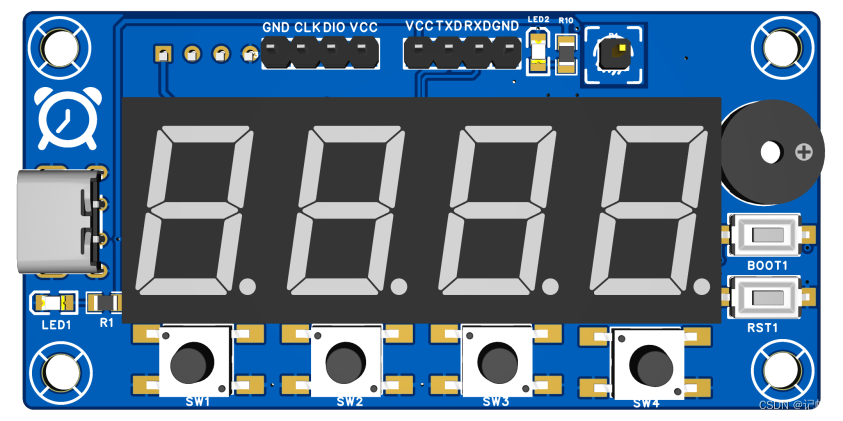

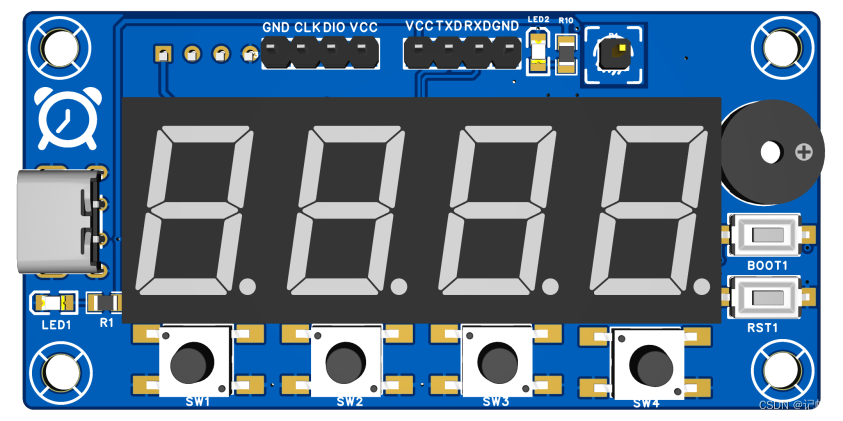

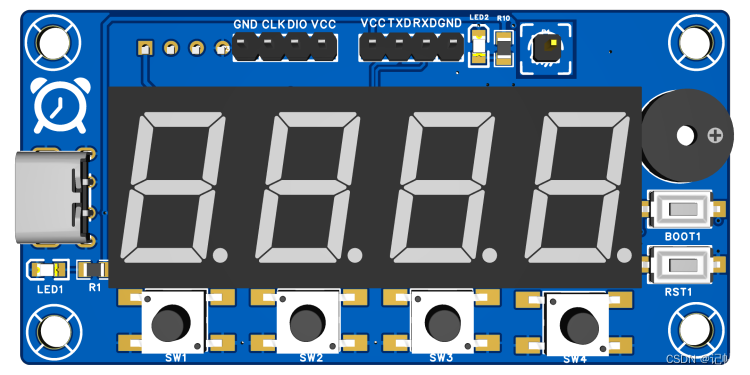

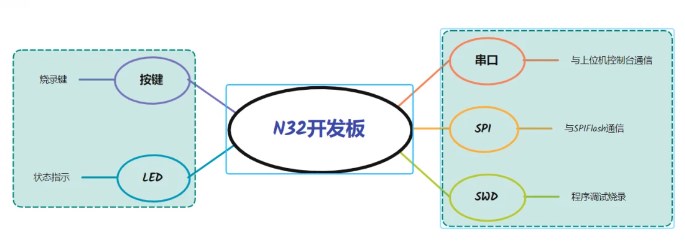

0 本節介紹使用串口工具對RA2L1進行程序的燒寫。采用CPK-RA2L1開發板,硬件如下圖所示。

2022-11-25 13:55:02 3106

3106 LOCK_PINS 是 Xilinx Vivado 做物理約束的屬性之一。用來將LUT的邏輯輸入(I0,,I1,I2...)綁定到其物理輸入pin上(A6,A5,A4...)。

2023-01-11 10:52:24 1810

1810 今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 2068

2068

本文主要介紹Vivado布線參數設置,基本設置方式和vivado綜合參數設置基本一致,將詳細說明如何設置布線參數以優化FPGA設計的性能,以及如何設置Vivado壓縮BIT文件。

2023-05-16 16:40:45 6174

6174

如果你正在使用Vivado開發套件進行設計,你會發現綜合設置中提供了許多綜合選項。這些選項對綜合結果有著潛在的影響,而且能夠提升設計效率。為了更好地利用這些資源,需要仔細研究每一個選項的功能。本文將要介紹一下Vivado的綜合參數設置。

2023-05-16 16:45:50 5589

5589

Vivado綜合默認是timing driven模式,除了IO管腳等物理約束,建議添加必要的時序約束,有利于綜合邏輯的優化,同時綜合后的design里面可以評估時序。

2023-07-03 09:03:19 1424

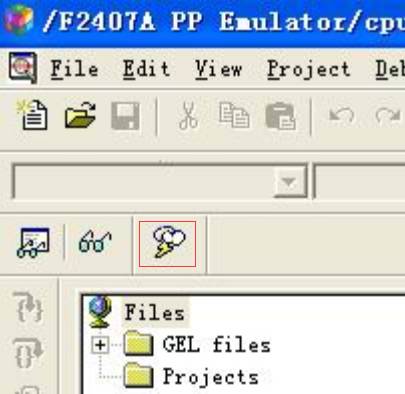

1424 由于 TI 的 DSP 燒寫要比單片機略微復雜,很多客戶對燒寫不是很熟悉,所以我們將燒寫方法做一個簡單的介紹。DSP 一般采用的是在線燒寫方法,即在電路板上有連接的 JTGA接口。燒寫工具是用 TI

2023-08-02 10:23:49 2348

2348

支持產線上對SPIFLASH內容的統一燒寫

2023-08-07 16:16:29 1608

1608

概述HPMManufacturingTool是HPMicro公司推出的配置及批量燒寫工具,旨在幫助企業用戶快速批量的對HPMicro公司推出的芯片進行鏡像配置及燒寫。該工具提供了用戶界面和命令行燒寫

2023-09-04 16:40:52 4104

4104

由于 TI 的 DSP 燒寫要比單片機略微復雜,很多客戶對燒寫不是很熟悉,所以我們將燒寫方法做一個簡單的介紹。DSP 一般采用的是在線燒寫方法,即在電路板上有連接的 JTGA接口。

2023-10-07 14:22:40 2785

2785

Xilinx Vivado開發環境編譯HDL時,對時鐘信號設置了編譯規則,如果時鐘由于硬件設計原因分配到了普通IO上,而非_SRCC或者_MRCC專用時鐘管腳上時,編譯器就會提示錯誤。

2024-04-15 11:38:26 13022

13022 白皮書:如何燒寫Flash——不同場景不同需求下的選擇認識Flash?NAND vs. NOR如何燒寫/編程不同方案比較

2025-07-28 16:05:52 0

0

電子發燒友App

電子發燒友App

評論