本文逐步演示了如何使用 AMD Vitis HLS 來創(chuàng)建一個(gè) HLS IP,通過 AXI4 接口從存儲(chǔ)器讀取數(shù)據(jù)、執(zhí)行簡單的數(shù)學(xué)運(yùn)算,然后將數(shù)據(jù)寫回存儲(chǔ)器。接著會(huì)在 AMD Vivado Design Suite 設(shè)計(jì)中使用此 HLS IP,并使用嵌入式 Vitis 應(yīng)用控制此 HLS IP。

2025-06-13 09:50:11 1447

1447

這篇文章在開發(fā)者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統(tǒng) IDE) 的基礎(chǔ)上撰寫,但使用的是 AMD Vitis Unified IDE,而不是之前傳統(tǒng)版本的 Vitis HLS。

2025-06-20 10:06:15 2068

2068

Vivado IP 流程(Vitis Unified),在這篇 AMD Vitis HLS 系列 3 中,我們將介紹如何使用 Unified IDE 創(chuàng)建 HLS 組件。這里采用“自下而上”的流程,從 HLS

2025-07-02 10:55:32 1263

1263

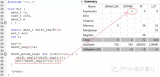

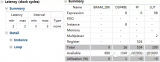

文件來與所得結(jié)果進(jìn)行對比驗(yàn)證。 3.實(shí)驗(yàn)步驟 3.1.在Vivado HLS GUI界面中創(chuàng)建項(xiàng)目 3.1.1.啟動(dòng)Vivado HLS 2018.1 ? ? 3.1.2.創(chuàng)建一個(gè)新的

2020-12-21 16:27:21 4357

4357 當(dāng)我們安裝好Vivado 的時(shí)候,也同時(shí)裝好了Vivado HLS.。 這是個(gè)什么東西?我就有一種想一探究的感覺。網(wǎng)上一查,Vivado High-Level Synthesis。學(xué)習(xí)了一

2020-10-14 15:17:19 4185

4185

時(shí)序分析是FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2022-10-21 09:28:58 4570

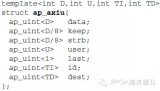

4570 ? HLS任務(wù)級編程第一篇文章可看這里: HLS之任務(wù)級并行編程 HLS的任務(wù)級并行性(Task-level Parallelism)分為兩種:一種是控制驅(qū)動(dòng)型;一種是數(shù)據(jù)驅(qū)動(dòng)型。對于控制驅(qū)動(dòng)型

2023-07-27 09:22:10 1950

1950

HLS的任務(wù)級并行性(Task-level Parallelism)分為兩種:一種是控制驅(qū)動(dòng)型;一種是數(shù)據(jù)驅(qū)動(dòng)型。

2023-07-27 09:21:40 1613

1613

該項(xiàng)目通過一個(gè)示例演示了 HLS 中組合電路對設(shè)計(jì)的影響。

2023-11-03 09:04:09 1549

1549

請教一下,我在HLS里面要將以下程序生成IP核,C Synthesis已經(jīng)做好了,但是在export RTL的時(shí)候一直在運(yùn)行

int sum_single(int A int B

2023-09-28 06:03:53

懷疑態(tài)度。高級語言IP的優(yōu)勢是顯而易見的,例如易維護(hù)性、在設(shè)計(jì)周期早期進(jìn)行重大變更的能力、以及大大節(jié)省產(chǎn)品上市時(shí)間等方面的優(yōu)勢都很明顯。目前的工具較之前一代工具,已有了大幅的進(jìn)步:它們允許一些受歡迎

2021-07-10 08:00:00

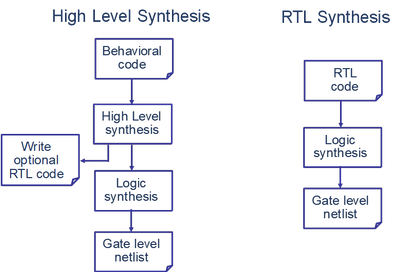

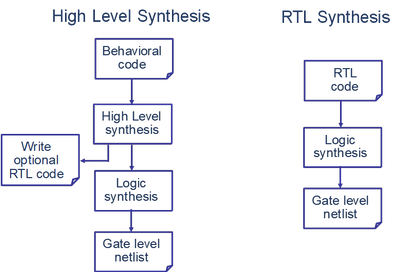

1、HLS最全知識(shí)庫介紹高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結(jié)構(gòu),自動(dòng)轉(zhuǎn)換成低抽象級語言描述的電路模型的過程。對于AMD Xilinx而言

2022-09-07 15:21:54

多個(gè)HLS解決方案2.實(shí)驗(yàn)內(nèi)容實(shí)驗(yàn)中文件中包含一個(gè)矩陣乘法器的實(shí)現(xiàn),實(shí)現(xiàn)兩個(gè)矩陣inA和inB相乘得出結(jié)果,并且提供了一個(gè)包含了計(jì)算結(jié)果的testbench文件來與所得結(jié)果進(jìn)行對比驗(yàn)證。...

2021-11-11 07:09:49

不同的編譯器,Xilinx Vivado High-Level Synthesis(高層綜合,HLS)工具同樣是一種編譯器,只不過它是用來將C或者C++程序部署到FPGA上,而不是部署到傳統(tǒng)的處理器上。在

2020-10-10 16:44:42

減少錯(cuò)誤并更容易調(diào)試。然而,經(jīng)常出現(xiàn)的問題是性能權(quán)衡。在高度復(fù)雜的 FPGA 設(shè)計(jì)中實(shí)現(xiàn)高性能需要手動(dòng)優(yōu)化 RTL 代碼,而這對于HLS開發(fā)環(huán)境生成的 RTL 代碼來說是不可能的。然而,存在一些解決方案

2024-08-16 19:56:07

1、使用Vitis HLS創(chuàng)建屬于自己的IP高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結(jié)構(gòu),自動(dòng)轉(zhuǎn)換成低抽象級語言描述的電路模型的過程。對于AMD

2022-09-09 16:45:27

Vivado 2017.4、Xilinx VivadoHLS 2017.4、Xilinx SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持

2021-02-19 18:36:48

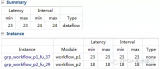

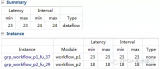

你好,我使用Vivado HLS生成了一個(gè)IP。從HLS測量的執(zhí)行和測量的執(zhí)行時(shí)間實(shí)際上顯著不同。由HLS計(jì)算的執(zhí)行非常小(0.14 ms),但是當(dāng)我使用AXI計(jì)時(shí)器在真實(shí)場景中測量它時(shí),顯示3.20 ms。為什么會(huì)有這么多差異? HLS沒有告訴實(shí)際執(zhí)行時(shí)間?等待回復(fù)。問候

2020-05-05 08:01:29

嗨? 如何在HLS 14.3中編寫pow功能? HLS 14.3不支持exp和pow功能。我在我的代碼中寫了“#include math.h”。但是,它不起作用。 另外,我想知道C代碼中

2019-03-05 13:40:09

Vivado HLS 2017.4 、Xilinx SDK 2017.4。

測試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC

2023-08-24 14:44:10

Vivado HLS 2017.4 、Xilinx SDK 2017.4。測試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設(shè)計(jì)的異構(gòu)多核SoC工業(yè)

2023-01-01 23:51:35

。

Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于 OpenCL 等框架對 Xilinx

2023-08-24 14:40:42

。Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于 OpenCL 等框架對 Xilinx

2023-01-01 23:52:54

(High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于 OpenCL 等框架對 Xilinx 可編程邏輯器件進(jìn)行開發(fā),可加速算法開發(fā)的進(jìn)程,縮短

2023-01-01 23:46:20

(High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于 OpenCL 等框架對 Xilinx 可編程邏輯器件進(jìn)行開發(fā),可加速算法開發(fā)的進(jìn)程,縮短

2023-08-24 14:54:01

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。

Xilinx Vivado HLS (High-Level Synthesis

2023-08-24 14:52:17

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。Xilinx Vivado HLS (High-Level Synthesis,高層次

2023-01-01 23:50:04

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于OpenCL等框架

2021-11-11 09:38:32

新思科技公司(Synopsys)目前推出該公司最新研發(fā)的Synphony HLS (High Level Synthesis)解決方案。該解決方案集成了M語言和基于模型的綜合法,與 傳統(tǒng)RTL流程

2019-08-13 08:21:49

的經(jīng)驗(yàn)幾乎為0,因此我想就如何解決這個(gè)問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉(zhuǎn)換VHDL中的C代碼(我現(xiàn)在有一些經(jīng)驗(yàn))2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

尊敬的先生,由于突然斷電我的桌面電腦在vivado HLS正在進(jìn)行我的代碼的C-Synthesis時(shí)關(guān)閉了,電源恢復(fù)后我啟動(dòng)計(jì)算機(jī)并嘗試啟動(dòng)HLS,然后小方形HLS符號來了(我把屏幕截圖放在了注冊

2020-04-09 06:00:49

同樣輸出AXI-Stream,再連到DMA.但是新手不知道那個(gè)HLS生成的IP怎么連?HLS的IP多了很多接口,這個(gè)IP有AXI control BUS,好像分辨率不一致,這個(gè)HLS的IP處理

2017-01-16 09:22:25

您好Xilinx的用戶和員工,我們正在考慮購買Zynq 7000用于機(jī)器視覺任務(wù)。我們沒有編程FPGA的經(jīng)驗(yàn),并希望使用Vivado HLS來指導(dǎo)和加速我們的工作。關(guān)于這種方法的一些問題:您對

2020-03-25 09:04:39

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于OpenCL等框架

2021-11-11 15:54:48

嗨伙計(jì),在我的PC Vivado設(shè)計(jì)套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2沒有打開,這就是為什么我想重新安裝Vivado HLS 2015.2。如何下載

2018-12-27 10:57:49

阻抗控制部分包括兩部分內(nèi)容:基本概念及阻抗匹配。本篇主要介紹阻抗控制相關(guān)的一些基本概念。

2021-02-25 08:11:03

描述 HLS系列霍爾效應(yīng)液位傳感器(HLS)是用于連續(xù)液位監(jiān)測的定制設(shè)計(jì)解決方案,適用溫度范圍寬廣,可校準(zhǔn)定制編程輸出以適應(yīng)各種幾何形狀的液位儲(chǔ)存箱。HLS系列是一款智能傳感器,帶有板載

2021-07-14 14:08:24

本文主要講述了實(shí)時(shí)多任務(wù)系統(tǒng)中的一些基本概念。

2009-04-22 16:17:36 15

15 Synopsys天宣布推出其Synphony HLS (High Level Synthesis)解決方案

新思科技公司,今天宣布推出其Synphony HLS (High Level Synthesis)解決方案。該解決方案集成了M語言和基于模型的綜合

2009-11-04 16:55:53 1417

1417 關(guān)于單片機(jī)的一些基本概念

隨著電子技術(shù)的迅速發(fā)展,計(jì)算機(jī)已深入地滲透到我們的生活中,許多電子愛好者開始學(xué)習(xí)單片機(jī)知識(shí),但單片機(jī)的內(nèi)容比較抽象,相

2010-03-18 16:54:07 1218

1218 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進(jìn)行 FPGA 設(shè)計(jì)的簡介

2016-01-06 11:32:55 65

65 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料——電路的一些基本概念

2016-08-22 16:18:03 0

0 電子專業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料——電路的一些基本概念

2016-10-10 14:17:59 0

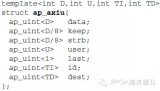

0 高層次綜合設(shè)計(jì)最常見的的使用就是為CPU創(chuàng)建一個(gè)加速器,將在CPU中執(zhí)行的代碼移動(dòng)到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設(shè)計(jì)中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 4243

4243

HLS非常適合一些信號處理模塊的快速實(shí)現(xiàn)。下面是一個(gè)實(shí)際的例子,由于使用了HLS,非常高效的就完成了模塊的rtl的實(shí)現(xiàn),比用手工coding節(jié)約了大量的時(shí)間! 需求描述: 在一個(gè)項(xiàng)目里面,需要

2017-02-08 02:33:36 1118

1118

Interface的另一個(gè)子類別:MemoryInterface: Memory Interface中分為3個(gè)子類別,分別是:ap_memroy,bram和ap_fifo。 ap_memory和bram

2017-02-08 02:42:41 1332

1332

繼續(xù)HLS的基本概念。 1、DataFlow的概念,以及Dataflow和Pipeline的區(qū)別 如下所示的圖像處理過程,數(shù)據(jù)處理由2個(gè)濾波器構(gòu)成: 默認(rèn)情況下,HLS會(huì)遵循c邏輯中的先后順序,依次

2017-02-08 03:20:41 1339

1339

在上一章HLS的端口綜合里有提及,HLS綜合后的端口分為2中類型:BlockLevel和Port Level Interface。其中Port level是我們需要重點(diǎn)關(guān)注的,它又可以細(xì)分為4中類型

2017-02-08 03:27:11 838

838

在之前HLS的基本概念1里有提及,HLS會(huì)把c的參數(shù)映射成rtl的端口實(shí)現(xiàn)。本章開始總結(jié)下HLS端口綜合的一些知識(shí)。 1.HLS綜合后的rtl端口大體可以分成2類: Clock Reset端口

2017-02-08 03:29:11 1162

1162

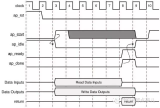

在上一章HLS提到了axi lite端口的綜合方式,以及directive的一些語法規(guī)則。這一章里面,介紹一下axi-stream和full axi端口的綜合實(shí)現(xiàn)問題。 1. AXI-Stream

2017-02-08 03:31:04 774

774

在上一章HLS提到了axi lite端口的綜合方式,以及directive的一些語法規(guī)則。這一章里面,介紹一下axi-stream和full axi端口的綜合實(shí)現(xiàn)問題。 AXI FULL端口的實(shí)現(xiàn)

2017-02-08 03:35:34 1124

1124

在之前的3章里,著重講解了HLS對AXI端口(包括axi-lite,axi-stream和full axi端口)的綜合實(shí)現(xiàn)問題,下面讓我們來介紹一下其它的端口類型是如何實(shí)現(xiàn)的。 在開始之前,先來

2017-02-08 03:39:11 849

849

端口就是在rtl代碼里所寫的。 因?yàn)閍p_none非常簡單,所以它不會(huì)帶來額外的硬件資源效率開銷。但是使用的時(shí)候,也有一些注意事項(xiàng): 1、 對輸入端口,數(shù)據(jù)需要在合適的時(shí)間及時(shí)準(zhǔn)備好,

2017-02-08 03:45:02 878

878

眾所周知,HLS是Xilinx于幾年前推出的一個(gè)高級綜合工具,可以直接把C/C++代碼,轉(zhuǎn)換成可綜合的verilog/VHDL代碼。聽起來很高級,是不是?。但看新鮮的人多,愿意吃螃蟹的人卻很少。這里

2017-02-08 05:07:20 2467

2467

在這個(gè)系列的上一篇文章“HighLevel Synthesis(HLS) 從一個(gè)最簡單的fir濾波器開始1”中,我們從一個(gè)最簡單的FIR濾波器,介紹了HLS是如何把C映射成RTL代碼的一些基本細(xì)節(jié)

2017-02-08 05:10:34 743

743 在上一章“High LevelSynthesis(HLS) 從一個(gè)最簡單的fir濾波器開始2”中,我們通過修改c的頭文件里面的類型精度定義,把DSP48E的消耗數(shù)量從8個(gè)壓縮到了2個(gè): 但這個(gè)結(jié)果

2017-02-08 05:11:11 775

775

在這個(gè)系列的前3篇文章“HighLevel Synthesis(HLS) 從一個(gè)最簡單的fir濾波器開始1-3”中,我們從一個(gè)最簡單的FIR濾波器,一步步優(yōu)化,得到了一個(gè)比較理想的HLS綜合結(jié)果

2017-02-08 05:13:37 1546

1546

在這個(gè)系列的前4篇文章“HighLevel Synthesis(HLS) 從一個(gè)最簡單的fir濾波器開始1-4”中,我們從一個(gè)最簡單的FIR濾波器,一步步優(yōu)化,得到了一個(gè)資源和Latency都比

2017-02-08 05:18:11 991

991

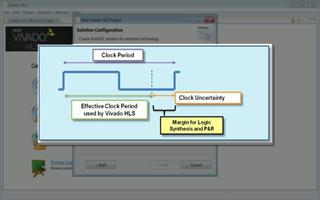

相信通過前面5篇fir濾波器的實(shí)現(xiàn)和優(yōu)化過程,大家對HLS已經(jīng)有了基本的認(rèn)識(shí)。是時(shí)候提煉一些HLS的基本概念了。 HLS支持C,C++,和SystemC作為輸入,輸出為Verilog(2001

2017-02-08 05:23:11 1111

1111

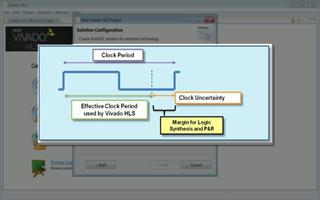

1. HLS僅支持一個(gè)主時(shí)鐘和復(fù)位 因此,目前還沒有辦法完全用HLS做出一個(gè)多時(shí)鐘域的設(shè)計(jì)。 2. 對于同一個(gè)參數(shù),HLS可以綜合出各種各樣的端口類型 這也需要額外的約束去進(jìn)行設(shè)置 3. 雖然一個(gè)c

2017-02-08 05:24:31 459

459

HLS工具 以個(gè)人的理解,xilinx將HLS(高層次綜合)定位于更方便的將復(fù)雜算法轉(zhuǎn)化為硬件語言,通過添加某些配置條件HLS工具可以把可并行化的C/C++的代碼轉(zhuǎn)化為vhdl或verilog,相比于純?nèi)斯な褂胿hdl實(shí)現(xiàn)圖像算法,該工具綜合出的代碼的硬件資源占用可能較多。

2019-10-12 17:34:00 2937

2937

,Xilinx Vivado HLS是一個(gè)高級綜合工具,能夠?qū)語言轉(zhuǎn)換成硬件描述語言(HDL),也就是說我們可以用C語言來實(shí)現(xiàn)HDL模塊編程了。 圖1 Vivado HLS工作流程 第一位Hacker

2017-02-08 20:01:59 846

846

David C Black是Doulos技術(shù)類高級成員 您是否設(shè)想過,“是否能有一種簡單的方法,將一些代碼加入不太昂貴的自定義處理器或自定義硬件?” 如果將這些慢代碼集成在硬件中難度是否會(huì)加大,我

2017-02-09 02:15:11 496

496 Design Tools>Vivado2014.2>Vivado HLS>Vivado HLS 2014.2 Command Prompt b. 在linux系統(tǒng)下,打開新的shell 2.變更到lab3

2017-02-09 05:07:11 1116

1116

高層次綜合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA設(shè)計(jì)工具,它能讓用戶通過編寫C/C++等高級語言代碼實(shí)現(xiàn)RTL級的硬件功能。隨著這款工具

2018-07-14 06:42:00 8006

8006 時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2017-02-11 19:08:29 4953

4953

在特定圖像處理硬件設(shè)計(jì)中成功運(yùn)用 High-Level Synthesis (HLS) 和 High-Level Verification (HLV) 數(shù)年之后, Qualcomm 認(rèn)識(shí)到了 HLS

2017-09-11 11:37:38 9

9 1 Vivado HLS簡介 2創(chuàng)建一個(gè)Vivado-HLS工程 2.1打開Vivado HLS GUI 2.2創(chuàng)建新工程 在 Welcome Page, 選擇Create New Project

2017-12-04 10:07:17 0

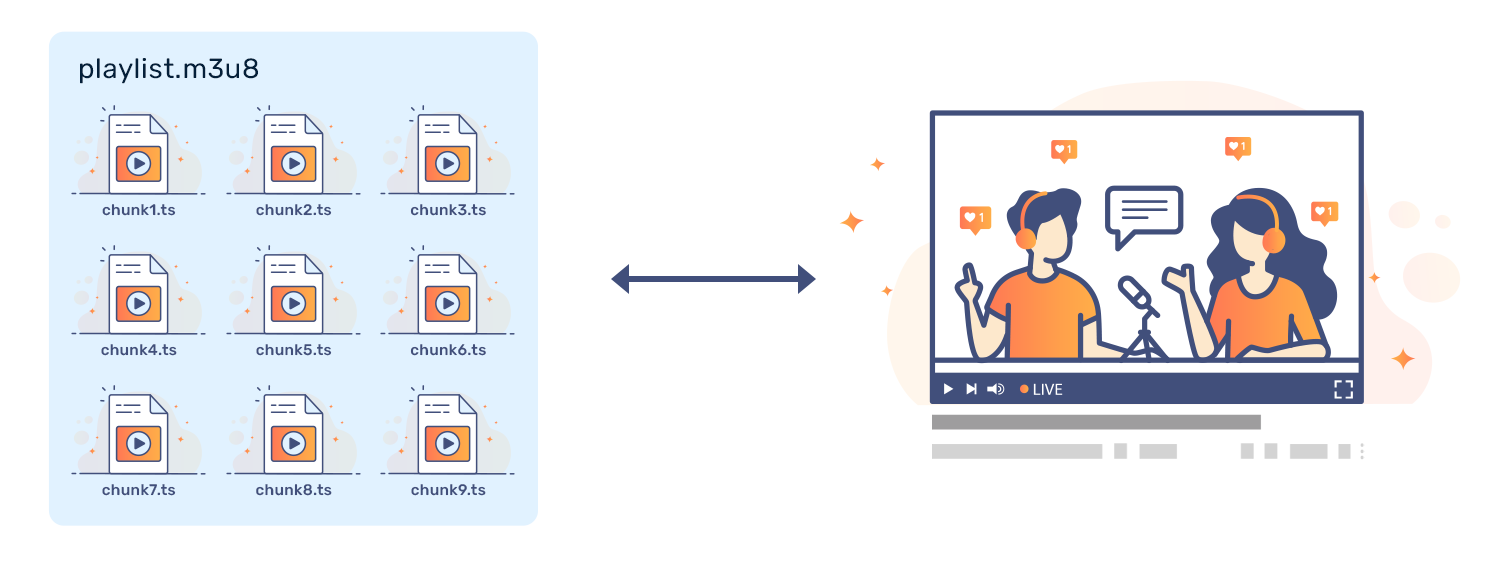

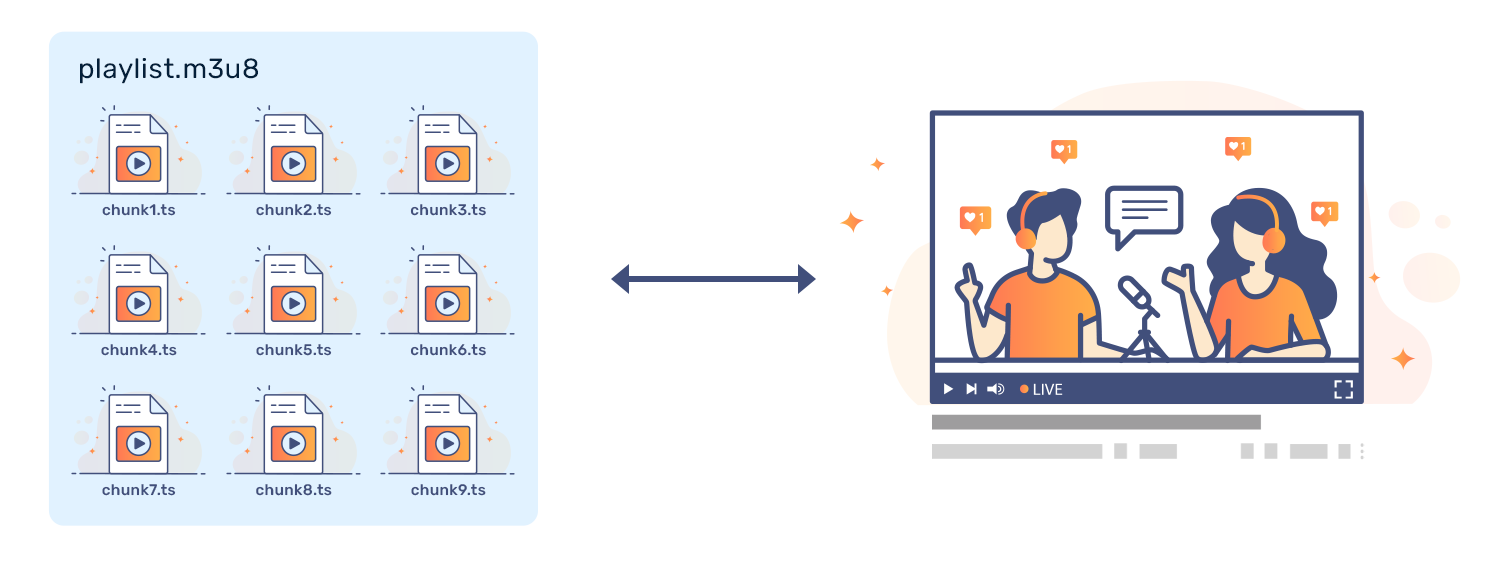

0 摘要:HTTP Live Streaming(縮寫是HLS)是一個(gè)由蘋果公司提出的基于HTTP的流媒體網(wǎng)絡(luò)傳輸協(xié)議。今天主要以HLS協(xié)議為中心講述它的一些原理。

2017-12-10 09:25:37 56558

56558 Xilinx公司講述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47:00 4478

4478

在集成電路行業(yè)飛速發(fā)展的今天,縮短產(chǎn)品開發(fā)的周期而又不犧牲驗(yàn)證過程,這不可避免地成為了商業(yè)市場的一個(gè)關(guān)鍵因素。Xilinx Vivado High Level Synthesis (即Vivado

2018-06-04 01:43:00 7738

7738

為了顯著加快驗(yàn)證速度,處理每天都會(huì)變化的復(fù)雜算法,很多公司轉(zhuǎn)向采用 High-Level Synthesis (HLS) 方法。但是,要利用在更高抽象度開展設(shè)計(jì)帶來的相關(guān)性能改進(jìn),采用 C++ 或

2019-05-21 17:11:40 6

6 接著開始正文。據(jù)觀察,HLS的發(fā)展呈現(xiàn)愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入門門檻(不用編寫

2019-07-31 09:45:17 7434

7434

高層次綜合(High-level Synthesis)簡稱 HLS,指的是將高層次語言描述的邏輯結(jié)構(gòu),自動(dòng)轉(zhuǎn)換成低抽象級語言描述的電路模型的過程。所謂的高層次語言,包括 C、C++、SystemC

2019-11-21 16:28:56 9587

9587 HLS高階綜合(high level synthesis)在被廣泛使用之前,作為商業(yè)技術(shù)其實(shí)已經(jīng)存在了20多年。設(shè)計(jì)團(tuán)隊(duì)對于這項(xiàng)技術(shù)可以說呈現(xiàn)出兩極化的態(tài)度:要么堅(jiān)信它是先進(jìn)技術(shù)之翹楚,要么對其持謹(jǐn)慎懷疑態(tài)度。

2020-11-04 13:45:03 3728

3728 的是VivadoIP,用于支持Vivado IP 設(shè)計(jì)流程。后者用于Vitis應(yīng)用加速流程,此時(shí),Vitis HLS會(huì)自動(dòng)推斷接口,無需在代碼里通過Pragma或Directive的方式定義Interface,最終會(huì)輸出.xo文件。 User Control Settings還有其他的一些變化,如下表

2020-11-05 17:43:16 40985

40985 本篇為邏輯電平系列文章中的第一篇,主要介紹邏輯電平相關(guān)的一些基本概念。后續(xù)將會(huì)介紹常見的單端邏輯電平(針對CMOS的閂鎖效應(yīng)進(jìn)行詳細(xì)介紹)、差分邏輯電平、單端邏輯電平的互連、差分邏輯電平的互連、一些特殊功能的互連、邏輯互連中的電流倒灌問題、以及邏輯電平的轉(zhuǎn)換等。

2021-01-06 17:40:17 16

16 說起高層次綜合技術(shù)(High-level synthesis)的概念,現(xiàn)在有很多初學(xué)者簡單地把它理解為可以自動(dòng)把c/c++之類地高級語言直接轉(zhuǎn)換成底層硬件描述語言(RTL)的技術(shù)。其實(shí)更準(zhǔn)確的表述是:由更高抽象度的行為描述生產(chǎn)電路的技術(shù)。

2022-02-08 17:26:42 9381

9381

<!--<img src="ams"-->HLS442_HLS440P_HPS100 (issued 2017-Apr)

2021-02-04 07:06:06 8

8 電子發(fā)燒友網(wǎng)為你提供阻抗控制相關(guān)的一些基本概念資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:55:57 39

39 gitee-monitor-rtsp-hls.zip

2022-05-07 11:06:57 4

4 在整個(gè)流程中,用戶先創(chuàng)建一個(gè)設(shè)計(jì) C、C++ 或 SystemC 源代碼,以及一個(gè)C的測試平臺(tái)。通過 Vivado HLS Synthesis 運(yùn)行設(shè)計(jì),生成 RTL 設(shè)計(jì),代碼可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 8680

8680 FPGA各位和數(shù)字IC設(shè)計(jì)崗位面試時(shí)常常會(huì)問下verilog的一些基本概念,做了下整理,面試時(shí)一定用得上!

2022-07-07 09:51:10 2192

2192 HLS導(dǎo)出的.xo文件如何導(dǎo)入到Vitis里面?需要把.xo文件解壓,然后把文件夾導(dǎo)入到Vitis Kernel/src文件夾下嗎?

2022-08-03 11:20:26 3933

3933

Vitis HLS 工具能夠?qū)?C++ 和 OpenCL 功能部署到器件的邏輯結(jié)構(gòu)和 RAM/DSP 塊上。在 GitHub 上提供 Vitis HLS 前端為研究人員、開發(fā)人員和編譯器愛好者開啟了無限可能的新世界,使他們可以利用 Vitis HLS 技術(shù)并根據(jù)其應(yīng)用的特定需求進(jìn)行修改。

2022-08-03 09:53:58 1602

1602 對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

2022-09-02 09:06:23 4612

4612 軟件編譯器講高級語言翻譯成為機(jī)器語言。主要關(guān)注的語言的語法轉(zhuǎn)換規(guī)則,相比之下,HLS 的翻譯難度更大一些,模塊中的語句形式上是前后順序排列。但是HLS盡力轉(zhuǎn)換成為并行執(zhí)執(zhí)行的硬件邏輯。

2022-10-10 14:50:29 2419

2419 1、HLS簡介 HLS(High-Level Synthesis)高層綜合,就是將 C/C++的功能用 RTL 來實(shí)現(xiàn),將 FPGA 的組件在一個(gè)軟件環(huán)境中來開發(fā),這個(gè)模塊的功能驗(yàn)證在軟件環(huán)境中來

2022-12-02 12:30:02 7407

7407 對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時(shí)將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點(diǎn)介紹Vitis HLS。

2023-01-15 11:27:49 4024

4024 HLS ?(high-level synthesis)稱為高級綜合, 它的主要功能是用 C/C++為 FPGA開發(fā) 算法。這將提升FPGA 算法開發(fā)的生產(chǎn)力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 6467

6467 HLS,Http Live Streaming 是由Apple公司定義的用于實(shí)時(shí)流傳輸?shù)膮f(xié)議,HLS基于HTTP協(xié)議實(shí)現(xiàn),傳輸內(nèi)容包括兩部分,一是M3U8描述文件,二是TS媒體文件。

2023-04-06 09:29:50 1357

1357 Xilinx平臺(tái)的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令會(huì)無法導(dǎo)出 IP

2023-07-07 14:14:57 1929

1929

電子發(fā)燒友網(wǎng)站提供《UltraFast Vivado HLS方法指南.pdf》資料免費(fèi)下載

2023-09-13 11:23:19 2

2 電子發(fā)燒友網(wǎng)站提供《Vitis HLS移植指南.pdf》資料免費(fèi)下載

2023-09-13 09:21:12 1

1 電子發(fā)燒友網(wǎng)站提供《將VIVADO HLS設(shè)計(jì)移植到CATAPULT HLS平臺(tái).pdf》資料免費(fèi)下載

2023-09-13 09:12:46 2

2 -自適應(yīng)流- HTTP) HLS(HTTP- Live-流) 兩種協(xié)議的工作方式相似——數(shù)據(jù)被編碼(分割)成塊并發(fā)送到客戶端進(jìn)行查看。 一、HLS(HTTP直播) HLS(即HTTP Live

2023-10-09 17:16:54 2349

2349

STMicroelectronics成像部門負(fù)責(zé)向消費(fèi)者、工業(yè)、安全和汽車市場提供創(chuàng)新的成像技術(shù)和產(chǎn)品。該團(tuán)隊(duì)精心制定了一套通過模板實(shí)現(xiàn)的High-Level Synthesis(HLS)高層次綜合流程,使得上述產(chǎn)品能夠迅速上市。對于汽車市場,該流程符合ISO 26262標(biāo)準(zhǔn),因此能確保可靠性。

2025-01-08 14:39:37 1209

1209

電子發(fā)燒友App

電子發(fā)燒友App

評論