添加Zynq Processing System IP核,配置DDR控制器和時(shí)鐘。7000系列的Zynq可以參考正點(diǎn)原子DMA回環(huán)測(cè)試設(shè)置。

2025-11-24 09:25:50 2881

2881

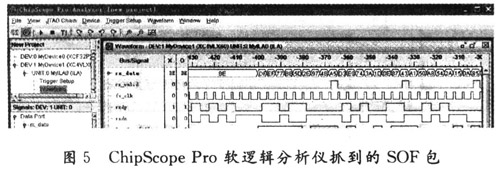

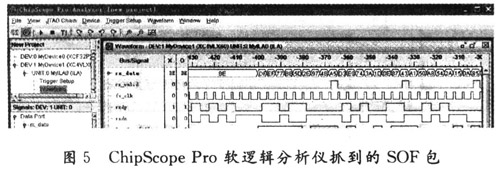

介紹了一款可配置的USB IP核設(shè)計(jì),重點(diǎn)描述USB IP核的結(jié)構(gòu)劃分,詳細(xì)闡述了各模塊的設(shè)計(jì)思想。為了提高USB lP的可重用性,本USB IP核設(shè)計(jì)了總線適配器,經(jīng)

2010-07-17 10:39:51 3124

3124

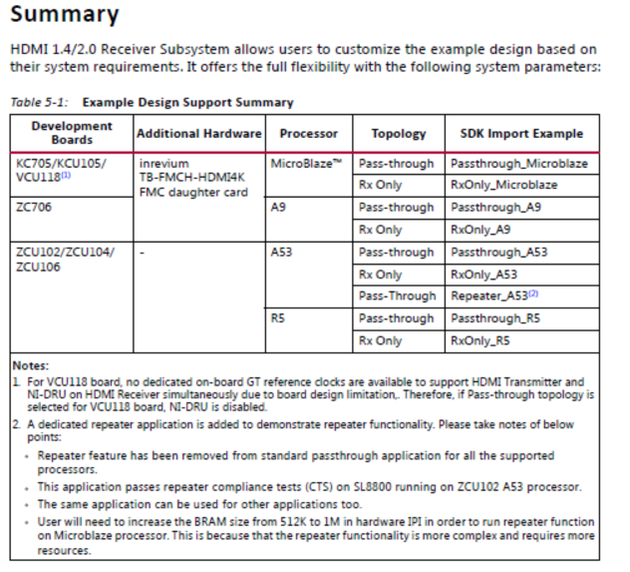

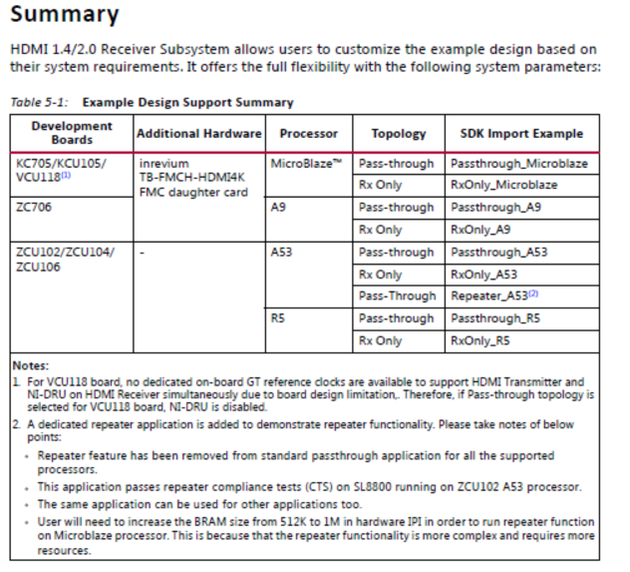

) IP 核 (HDMI 1.4/2.0 TX Subsystem) 和 Sink IP 核 (HDMI 1.4/2.0 RX Subsystem)。 這些 IP 核的介紹請(qǐng)參閱 (PG235) 和 (PG236)。《產(chǎn)品指南》第 5 章中

2020-11-20 11:44:15 7527

7527

創(chuàng)建自己的IP核有很多好處,例如系統(tǒng)設(shè)計(jì)定制化;設(shè)計(jì)復(fù)用,可以在在IP核中加入license, 有償提供給別人使用;簡(jiǎn)化系統(tǒng)設(shè)計(jì)和縮短設(shè)計(jì)時(shí)間。用ZYNQ系統(tǒng)設(shè)計(jì)IP核,最常用的就是使用AXI總線將

2021-02-01 10:13:00 6025

6025

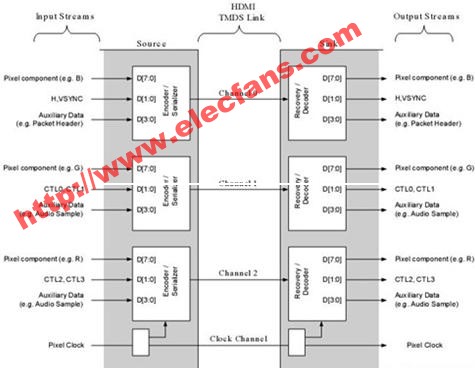

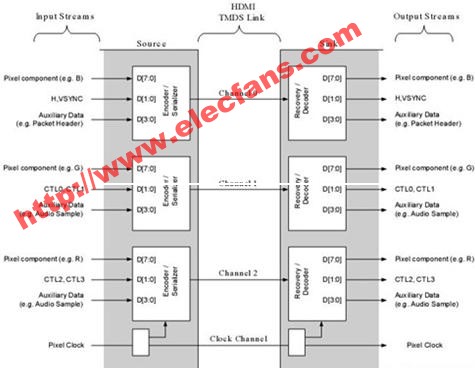

HDMI傳輸原理介紹如同最頂級(jí)的發(fā)動(dòng)機(jī)是F1賽車馳騁賽場(chǎng)的保障一樣,HDMI標(biāo)準(zhǔn)之所以擁有強(qiáng)大的數(shù)據(jù)傳輸能力,和它的傳輸原理是分不開的,下面我們就看看HDMI標(biāo)準(zhǔn)的傳輸原理是什么。

2008-10-20 13:43:15

我們?yōu)?b class="flag-6" style="color: red">Zynq開發(fā)了我們自己的基于Qt的gui,但HDMI輸出卻遇到了相當(dāng)大的不穩(wěn)定性。這意味著即使您沒有顯示除linux命令行之外的任何內(nèi)容,HDMI也會(huì)經(jīng)常出現(xiàn)故障。當(dāng)您按Ctrl-c gui

2019-09-03 06:17:02

本帖最后由 Tronlong創(chuàng)龍科技 于 2021-6-7 08:48 編輯

?本文主要介紹ZYNQ PS + PL異構(gòu)多核案例的使用說明,適用開發(fā)環(huán)境:Windows 7/10 64bit

2021-05-28 14:28:28

ZYNQ學(xué)習(xí)筆記_ZYNQ簡(jiǎn)介和Hello WorldZYNQ介紹PS和PL的連接ZYNQ開發(fā)工具鏈在PS端編寫Hello World程序ZYNQ介紹ZYNQ-7000系列是基于Xilinx開發(fā)環(huán)境

2022-02-17 07:37:36

我想問一下,在quartus上直接調(diào)用IP核和在qsys中用IP核有什么區(qū)別?自個(gè)有點(diǎn)迷糊了

2017-08-07 10:09:03

zynq的PS如何向一個(gè)基于AXI4-FULL協(xié)議的自定義IP批量傳輸數(shù)據(jù)?

2017-02-22 12:05:35

目前,我在設(shè)計(jì)中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉(zhuǎn)換器AD9683轉(zhuǎn)換完成后的數(shù)據(jù)。但是JESD204 IP核的端口很多,我不知道應(yīng)該如何將AD9683

2023-12-15 07:14:52

公司現(xiàn)需12bit sar adc的IP核,國(guó)內(nèi)有哪些公司提供相關(guān)方面的服務(wù)了?

2015-11-06 08:37:44

用Quartus II 調(diào)用IP核時(shí),在哪可以查看IP核的例程

2014-07-27 20:28:04

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨(dú)立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個(gè)RAM?如果我以ROM的形式調(diào)用該IP核,在

2013-01-10 17:19:11

:

注意保護(hù)所使用的IP軟核的知識(shí)產(chǎn)權(quán)。遵守相關(guān)的知識(shí)產(chǎn)權(quán)法律和協(xié)議,避免侵犯他人的知識(shí)產(chǎn)權(quán)。

持續(xù)學(xué)習(xí)和更新 :

FPGA技術(shù)和IP軟核不斷發(fā)展,建議持續(xù)學(xué)習(xí)和關(guān)注最新的技術(shù)動(dòng)態(tài)和更新。這將

2024-05-27 16:13:24

有誰知道現(xiàn)在國(guó)內(nèi)外有哪些公司賣FPGA的圖像處理相關(guān)的IP核?

2015-04-28 21:34:24

H-HDMI-IP - Typical H-HDMI-IP Application - THOR communications

2022-11-04 17:22:44

本帖最后由 gk320830 于 2015-3-8 09:29 編輯

LCD的通用驅(qū)動(dòng)電路IP核設(shè)計(jì) 摘 要:本文介紹了一種新型的LCD驅(qū)動(dòng)電路IP核的總體設(shè)計(jì),采用自頂向下的設(shè)計(jì)方法將其

2012-08-12 12:28:42

Mixer IP核將兩路視頻進(jìn)行疊加顯示。程序功能框圖2 操作說明將MT9V034攝像頭接到評(píng)估板CAMERA1接口,將HDMI顯示屏通過HDMI數(shù)據(jù)線連接至評(píng)估板HDMI OUT接口。將本案例的動(dòng)態(tài)設(shè)備

2021-05-24 11:12:40

發(fā)生IP核鎖定,一般是Vivado版本不同導(dǎo)致的,下面介紹幾種方法: 1 常用的方法 1)生成IP核的狀態(tài)報(bào)告 Report -》 Report IP Status 2)點(diǎn)擊

2021-01-08 17:12:52

正點(diǎn)原子FPGA新品ZYNQ7035/7045/7100開發(fā)板,ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

正點(diǎn)原子Z100 ZYNQ開發(fā)板,搭載Xilinx Zynq

2024-09-02 17:18:43

請(qǐng)問哪位高手有ise軟件中的各個(gè)ip核的功能介紹

2013-10-08 16:41:25

2.5MHz 振幅0-5V 的正弦信號(hào),請(qǐng)問 data 端口應(yīng)該輸入怎樣的信號(hào)?如果有Altera IP核相關(guān)的詳解資料推薦下更好。多謝了。

2014-10-28 12:34:41

大家伙,又到了每日學(xué)習(xí)的時(shí)間了,今天咱們來聊一聊vivado 調(diào)用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

大量使用了高云的IP核,包括:* 同步和異步FIFO:一方面為DispRAM提供連續(xù)傳輸的支持(HyperRAM Controller要求數(shù)據(jù)必須連續(xù)傳輸),另一方面也提供時(shí)鐘域(AHB總線到VGA

2021-05-15 00:00:28

”。32.2實(shí)驗(yàn)任務(wù)本章的實(shí)驗(yàn)任務(wù)是通過調(diào)用OSD IP核,在領(lǐng)航者Zynq開發(fā)板上實(shí)現(xiàn)雙目OV5640攝像頭HDMI顯示器的實(shí)時(shí)顯示,并在HDMI顯示器上疊加字符。32.3硬件設(shè)計(jì)我們的領(lǐng)航者Zynq

2020-09-07 15:56:04

詳細(xì)介紹了BMP圖片的數(shù)據(jù)格式;另外在《領(lǐng)航者FPGA開發(fā)指南》中的“HDMI彩條顯示實(shí)驗(yàn)”一章,我們介紹了HDMI接口。如果大家對(duì)這兩部分的內(nèi)容不熟悉的話,可以參考相應(yīng)的章節(jié),此處就不再贅述了

2020-09-05 15:40:56

口信號(hào)的管腳分配與“HDMI彩條顯示實(shí)驗(yàn)”完全相同,請(qǐng)參考“HDMI彩條顯示實(shí)驗(yàn)”中的硬件設(shè)計(jì)部分。19.4程序設(shè)計(jì)圖 19.4.1是根據(jù)本章實(shí)驗(yàn)任務(wù)畫出的系統(tǒng)框圖。其中,時(shí)鐘生成IP核

2020-09-26 16:55:15

對(duì)于深入學(xué)習(xí)使用FPGA的小伙伴們,特別是一些復(fù)雜的、大規(guī)模的設(shè)計(jì)應(yīng)用,適宜的IP核對(duì)開發(fā)能起到事半功倍的作用。IP核的概念與我們sdk里庫(kù)的概念相似。IP即電路功能模塊,用戶可以直接調(diào)用這些模塊

2024-04-29 21:01:16

,因此,開發(fā)統(tǒng)一的IP核接口標(biāo)準(zhǔn)對(duì)提高IP核的復(fù)用意義重大。本文簡(jiǎn)單介紹IP核概念,然后從接口標(biāo)準(zhǔn)的角度討論在SoC設(shè)計(jì)中提高IP核的復(fù)用度,從而簡(jiǎn)化系統(tǒng)設(shè)計(jì)和驗(yàn)證的方法,主要討論OCP(開放核協(xié)議

2019-06-11 05:00:07

,一路用于邊緣檢測(cè)處理(Sobel算法),另一路直接回顯。利用Video Mixer IP核將圖像疊加,通過HDMI輸出原始圖像或者算法處理后的圖像。本案例支持CameraLink Base/Full

2020-09-17 09:48:13

大家好,我正在做一個(gè)需要在zynq 702板上將你的IP核集成到ARM的項(xiàng)目。有人可以提供一些參考來處理它的界面嗎?謝謝。

2019-11-05 09:48:49

本文介紹了IP核的概念及其在SoC設(shè)計(jì)中的應(yīng)用,討論了為提高IP核的復(fù)用能力而采用的IP核與系統(tǒng)的接口技術(shù)。引言隨著半導(dǎo)體技術(shù)的發(fā)展,深亞微米工藝加工技術(shù)允許開發(fā)上百萬門級(jí)的單芯片,已能夠?qū)⑾到y(tǒng)級(jí)

2018-12-11 11:07:21

上篇推文為大家介紹了創(chuàng)龍科技(Tronlong)最新推出的DSP + ZYNQ評(píng)估板TL6678ZH-EVM,由核心板和底板構(gòu)成,核心板(SOM-TL6678ZH)集成了C6678

2021-03-16 17:53:53

本帖最后由 jf_85110202 于 2024-9-14 10:33 編輯

正點(diǎn)原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富

2024-09-14 10:12:14

`玩轉(zhuǎn)Zynq連載21——Vivado中IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https://pan.baidu.com

2019-09-04 10:06:45

LED,而是IP核的應(yīng)用,當(dāng)然,僅以PLL IP核為例。2 模塊化設(shè)計(jì)參考文檔《玩轉(zhuǎn)Zynq-基礎(chǔ)篇:基于FPGA的模塊化設(shè)計(jì).pdf》。3 PLL IP核添加配置 3.1Vivado標(biāo)準(zhǔn)IP核概述我們

2019-09-06 08:13:18

`玩轉(zhuǎn)Zynq連載23——用戶自定義IP核的創(chuàng)建與封裝更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https

2019-09-09 10:55:24

`玩轉(zhuǎn)Zynq連載24——用戶自定義IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https://pan.baidu.com/s

2019-09-15 09:55:57

`玩轉(zhuǎn)Zynq連載25——[ex04] 基于Zynq PL的自定義IP核集成更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https

2019-09-20 11:35:29

Zynq-7020 SOC。以上來自于谷歌翻譯以下為原文I've obtained an evaluation license for the Xilinx HDMI IP core, and I've

2019-01-02 15:02:41

。目前,我在設(shè)計(jì)中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉(zhuǎn)換器AD9683轉(zhuǎn)換完成后的數(shù)據(jù)。但是JESD204 IP核的端口很多,我不知道應(yīng)該如何將AD9683

2018-09-05 11:45:31

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設(shè)計(jì)?

2021-04-28 06:10:23

我有興趣購(gòu)買“Xilinx Zynq-7000 SoC ZC702評(píng)估套件”我想知道成像/視頻IP核是否包含在主板附帶的軟件開發(fā)中。謝謝---------- Khlitoshi

2019-09-05 09:48:00

各位大家好,我找到了xilinx zynq單板電腦板,但我發(fā)現(xiàn)它有顯示限制,我問他們的工程師,他們告訴我這塊板子使用xylon試用版IP而且只能在啟動(dòng)后30分鐘內(nèi)工作,我需要購(gòu)買IP核的許可證,但我認(rèn)為許可證價(jià)格非常高,是否有可能自己開發(fā)IP核?有什么好建議嗎?

2019-10-21 09:50:42

基于Spartan_3E的LCD IP核設(shè)計(jì)與實(shí)現(xiàn)相關(guān)文檔及源碼

2009-08-03 09:37:00 48

48 USB設(shè)備接口IP核的設(shè)計(jì):討論了用Verilog硬件描述語(yǔ)言來實(shí)現(xiàn)USB設(shè)備接口IP核的方法,并進(jìn)行了FPGA的驗(yàn)證。簡(jiǎn)要介紹USB系統(tǒng)的體系結(jié)構(gòu),重點(diǎn)描述USB設(shè)備接口IP核的結(jié)構(gòu)劃分和各模塊的

2010-01-08 18:15:38 22

22 基于Avalon總線的可配置LCD 控制器IP核的設(shè)計(jì)

本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設(shè)計(jì),根據(jù)自頂向下的設(shè)計(jì)思想,將IP 核進(jìn)行層次功能

2010-02-09 09:34:44 27

27 介紹了用于IP核測(cè)試的內(nèi)建自測(cè)試方法(BIST)和面向測(cè)試的IP核設(shè)計(jì)方法,指出基于IP核的系統(tǒng)芯片(SOC) 的測(cè)試、驗(yàn)證以及相關(guān)性測(cè)試具有較大難度,傳統(tǒng)的測(cè)試和驗(yàn)證方法均難以滿足

2010-12-13 17:09:11 10

10 HDMI傳輸原理詳解

如同最頂級(jí)的發(fā)動(dòng)機(jī)是F1賽車馳騁賽場(chǎng)的保障一樣,HDMI標(biāo)準(zhǔn)之所以擁有強(qiáng)大的數(shù)據(jù)傳輸能力,和它的傳輸原理是分不開的

2008-10-20 13:42:53 7569

7569

基于PCI IP核的碼流接收卡的設(shè)計(jì)

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統(tǒng)的硬件設(shè)計(jì)方案及設(shè)計(jì)要點(diǎn)的分析。該設(shè)計(jì)采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

本文介紹的基于Wishbone總線的UART IP核的設(shè)計(jì)方法,通過驗(yàn)證表明了各項(xiàng)功能達(dá)到預(yù)期要求,為IP核接口的標(biāo)準(zhǔn)化設(shè)計(jì)提供了依據(jù)。此外,該IP核代碼全部采用模塊化的Verilog-HDL語(yǔ)言編寫,

2011-06-10 11:47:37 4199

4199

介紹了SoPC(System on a Programmable Chip)系統(tǒng)的概念和特點(diǎn),給出了基于PLB總線的異步串行通信(UART)IP核的硬件設(shè)計(jì)和實(shí)現(xiàn)。通過將設(shè)計(jì)好的UART IP核集成到SoPC系統(tǒng)中加以驗(yàn)證,證明了所

2012-03-05 17:53:49 63

63 電子發(fā)燒友網(wǎng)核心提示:本文主要介紹了紅外解碼IP核在SoPC系統(tǒng)中的設(shè)計(jì)與實(shí)現(xiàn)方法,重點(diǎn)研究紅外系統(tǒng)的數(shù)據(jù)編碼和傳輸機(jī)制、紅外解碼電路的HDL設(shè)計(jì)、IP核的制作及在SoPC系統(tǒng)中的應(yīng)

2012-11-30 10:56:40 7361

7361 FPGA中IP核的生成,簡(jiǎn)單介紹Quartus II生成IP核的基本操作,簡(jiǎn)單實(shí)用挺不錯(cuò)的資料

2015-11-30 17:36:15 12

12 高層次綜合設(shè)計(jì)最常見的的使用就是為CPU創(chuàng)建一個(gè)加速器,將在CPU中執(zhí)行的代碼移動(dòng)到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設(shè)計(jì)中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 4243

4243

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(kù)(例如C語(yǔ)言

2017-02-08 13:08:11 3085

3085

Zynq-7010 IP核的歷程

2017-03-01 21:43:20 3

3 本文主要介紹zynq linux AXI DMA傳輸步驟教程,具體的跟隨小編一起來了解一下。

2018-07-08 05:46:00 32067

32067

在對(duì)zynq進(jìn)行Linux驅(qū)動(dòng)開發(fā)時(shí),除了需要針對(duì)zynq內(nèi)ARM自帶的控制器適配驅(qū)動(dòng)外,還需要對(duì)zynq PL部分的IP核進(jìn)行驅(qū)動(dòng)開發(fā)。對(duì)于ARM來說,zynq PL部分的IP核就是一段地址空間

2018-06-30 15:10:00 10289

10289 本文主要介紹Zedboard HDMI核的構(gòu)建和輸出顯示測(cè)試,具體的跟隨小編一起來了解一下。

2018-06-29 11:15:00 7449

7449

本文介紹一種使用Zynq SoC和賽靈思IP 核簡(jiǎn)化高速光學(xué)收發(fā)器模塊熱測(cè)試的方法。 隨著數(shù)據(jù)中心內(nèi)部光學(xué)收發(fā)器模塊的傳輸速度提高到前所未有的高度,數(shù)據(jù)中心內(nèi)每個(gè)機(jī)架的溫度也在不斷大幅上升。機(jī)架中有

2017-11-17 18:11:01 2062

2062 提出一種便于用戶操作并能快速運(yùn)用到產(chǎn)品的DDR2控制器IP核的FPGA實(shí)現(xiàn),使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡(jiǎn)單介紹了DDR2的特點(diǎn)和操作原理,并

2017-11-22 07:20:50 5930

5930

本文包含兩部分內(nèi)容:1)AXI接口簡(jiǎn)介;2)AXI IP核的創(chuàng)建流程及讀寫邏輯分析。 1AXI簡(jiǎn)介(本部分內(nèi)容參考官網(wǎng)資料翻譯) 自定義IP核是Zynq學(xué)習(xí)與開發(fā)中的難點(diǎn),AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

具體應(yīng)用區(qū)別就是:1、具體HDMI延長(zhǎng)器與HDMI IP延長(zhǎng)器的區(qū)別就一個(gè)關(guān)鍵點(diǎn)過不過路由器或者交換機(jī),HDMI延長(zhǎng)器一發(fā)一收單網(wǎng)線最長(zhǎng)不超過120M的信號(hào)傳輸過程。HDMI IP延長(zhǎng)器一發(fā)多收

2017-12-27 10:14:48 18404

18404

本文檔內(nèi)容介紹了建立用戶自己的IP核的操作步驟,供參考

2018-04-03 11:26:51 4

4 大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天咱們來聊一聊vivado 調(diào)用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 Zynq-7000 PL端HDMI的顯示控制 Zynq-7000 PS到PL端emio的使用 Vivado 專家文章:Tcl 是什么? Zynq-7000 ARM端MIO的使用 Zynq

2019-09-15 14:57:00 4227

4227 Xilinx的HDMI 1.4 Tx / Rx和HDMI 2.0 Tx / Rx的IP內(nèi)核將采用最新發(fā)布的inrevium AMERICA FMC HDMI 4K。

2018-11-28 06:23:00 13736

13736 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3814

3814 本視頻將向您講解如何使用Zynq-7000 VIP(驗(yàn)證IP)來高效地驗(yàn)證基于Zynq-7000處理系統(tǒng)的設(shè)計(jì)。另外,視頻還介紹了如何配置,以及如何使用范例項(xiàng)目進(jìn)行仿真的實(shí)施步驟。

2018-11-22 06:48:00 5300

5300 復(fù)旦大學(xué)微電子學(xué)院某國(guó)家重點(diǎn)實(shí)驗(yàn)室內(nèi)部教學(xué)視頻:基于ZYNQ FPGA與PC的IP設(shè)計(jì)與驗(yàn)證方案。

關(guān)鍵詞:IP設(shè)計(jì),IP驗(yàn)證,AXI總線協(xié)議,ARM,UDP傳輸,PYTHON

2019-08-06 06:16:00 2714

2714

Zynq-7000系列的可編程結(jié)構(gòu)經(jīng)定制可以最大化系統(tǒng)級(jí)性能,滿足特定應(yīng)用的各種需求。該套件提供了包括開發(fā)工具、AMB4AXI4即插即用IP核和總線功能模型(BFM)等在內(nèi)的完整硬件開發(fā)環(huán)境,有助于加速設(shè)計(jì)和驗(yàn)證工作。

2019-12-20 07:06:00 1482

1482

Zynq-7000系列的可編程邏輯完全基于賽靈思最新7系列FPGA架構(gòu)來設(shè)計(jì),可確保28nm系列器件的IP核、工具和性能100%兼容。

2019-12-20 07:02:00 2109

2109

質(zhì)量的不同;HDMI圖像處理設(shè)備不同;導(dǎo)致傳輸距離也是不同的。下面我介紹邁拓維矩給最新的HDMI遠(yuǎn)距離傳輸解決方案:(注明:距離均為從HDMI信號(hào)源開始計(jì)算到最終的顯示設(shè)備的線材長(zhǎng)度,非直線距離,而是布線距離,對(duì)于不同的距離我們有不同的解決傳輸的方式) 1、HD

2020-07-02 14:52:05 17073

17073 ZYNQ是一個(gè)可擴(kuò)展平臺(tái),就是有FPGA作為外設(shè)的A9雙核處理器,它的啟動(dòng)流程與FPGA完全不同,而與傳統(tǒng)的ARM處理器類似,ZYNQ的啟動(dòng)配置需要多個(gè)處理步驟。

2020-12-05 10:48:58 6747

6747 ? Xilinx公司的FPGA中有著很多的有用且對(duì)整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 ZYNQ OpenAMP雙核ARM通信案例開發(fā)手冊(cè)

2021-07-06 10:27:07 32

32 IP核目前的IP設(shè)計(jì)已成為目前FPGA設(shè)計(jì)的主流方法之一,應(yīng)用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數(shù)據(jù)塊。IP核在SoC中的集成方式及應(yīng)用場(chǎng)景,芯片設(shè)計(jì)中的IP核具有特定功能的可復(fù)用的標(biāo)準(zhǔn)性和可交易性,已經(jīng)成為集成電路設(shè)計(jì)技術(shù)的核心與精華。

2021-10-01 09:08:00 3100

3100 :HDMI輸入:1080P60,HDMI輸出:1080P60;距離:200米;特色:支持紅外遠(yuǎn)程遙控;優(yōu)勢(shì):H.265畫質(zhì)好,低延時(shí);標(biāo)準(zhǔn)的TCP/IP協(xié)議;KVM遠(yuǎn)程傳輸,一對(duì)多,多對(duì)一,多對(duì)多分布式矩陣

2022-01-19 16:02:25 2196

2196 HDMI延長(zhǎng)器是用來延長(zhǎng)信號(hào)的器件,通常用于長(zhǎng)距離直連線材無法滿足傳輸要求的情況,一般是為了確保信號(hào)長(zhǎng)距離無衰減的傳輸而設(shè)計(jì),因此多是有源的。 傳統(tǒng)的HDMI延長(zhǎng)器分為兩種,一類是傳輸模擬信號(hào)

2022-03-24 18:12:45 1023

1023 Xilinx HDMI 1.4/2.0 RX的解決方案是由HDMI 1.4/2.0 Receiver Subsystem IP作為MAC和Video PHY Controller IP作為PHY組成,在板上,由外部電阻來實(shí)現(xiàn)TMDS level shifter,還有TMDS181作為retimer。

2022-03-25 09:13:08 5446

5446 學(xué)習(xí)關(guān)于ZYNQ IP核中的GP接口和HP接口的異同,介紹關(guān)于AXI_GP接口和AXI_HP接口的相關(guān)內(nèi)容。

2022-07-03 14:17:34 4898

4898 本文主要介紹關(guān)于AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核相關(guān)內(nèi)容。為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測(cè)試工程做準(zhǔn)備。

2022-07-03 16:11:05 10565

10565 在仿真Vivado IP核時(shí)分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

armbian、 hdmi、 zynq、 mpsoc、 rk3399

2023-10-13 18:11:00 3362

3362 HDMI光纖傳輸器的特點(diǎn) HDMI光纖傳輸器的傳輸距離有多遠(yuǎn)? HDMI光纖傳輸器是一種用于傳輸高清視頻和音頻信號(hào)的設(shè)備,它通過使用光纖傳輸線路保證了傳輸的高質(zhì)量和穩(wěn)定性。下面將詳細(xì)介紹HDMI光纖

2023-12-04 14:40:42 1858

1858 Xilinx公司的FPGA中有著很多的有用且對(duì)整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 在使用FPGA的時(shí)候,有些IP核是需要申請(qǐng)后才能使用的,本文介紹如何申請(qǐng)xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

在創(chuàng)新加速的浪潮中,為更好地響應(yīng)客戶群需求, 芯驛電子 ALINX 推出全新 IP 核產(chǎn)品線 ,致力于為高性能數(shù)據(jù)傳輸和復(fù)雜計(jì)算需求提供 高帶寬、低延遲 的解決方案。發(fā)布的第一批 IP 核包括

2024-10-30 17:39:43 1459

1459

本文介紹了Vidado中FFT IP核的使用,具體內(nèi)容為:調(diào)用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測(cè)試數(shù)據(jù)>>測(cè)試verilogHDL>>TestBench仿真>>結(jié)果驗(yàn)證>>FFT運(yùn)算。

2024-11-06 09:51:43 5640

5640

ALINX近日宣布,基于AMD 100G以太網(wǎng)MAC IP,成功開發(fā)出全新的100G以太網(wǎng)UDP/IP協(xié)議棧IP核。該IP核在數(shù)據(jù)傳輸方面表現(xiàn)出色,MTU支持高達(dá)9000Bytes,采用標(biāo)準(zhǔn)

2025-01-07 11:25:25 1254

1254

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論