聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133435 -

Zynq

+關(guān)注

關(guān)注

10文章

630瀏覽量

49448

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

HLS設(shè)計中的BRAM使用優(yōu)勢

HLS設(shè)計的IP可以直接使用BRAM,但Block Memory Generator和AXI BRAM Controller仍然在FPGA設(shè)計中發(fā)揮著重要作用。

通過vivado HLS設(shè)計一個FIR低通濾波器

Vivado HLS是一款強大的高層次綜合工具,可將C/C++代碼轉(zhuǎn)換為硬件描述語言(HDL),顯著提升FPGA開發(fā)效率。

響應(yīng)謎云:誰按下了車機的“慢放鍵”#DDS #AIagent #數(shù)字智能體 #分布式數(shù)字分發(fā)服務(wù)

DDS

北匯信息POLELINK

發(fā)布于 :2025年11月26日 15:38:39

基于AXI DMA IP核的DDR數(shù)據(jù)存儲與PS端讀取

添加Zynq Processing System IP核,配置DDR控制器和時鐘。7000系列的Zynq可以參考正點原子DMA回環(huán)測試設(shè)置。

AMD Vivado IP integrator的基本功能特性

我們還將帶您了解在 AMD Zynq UltraScale+ MPSoC 開發(fā)板與 AMD Versal 自適應(yīng) SoC 開發(fā)板上使用 IP integrator 時,兩種設(shè)計流程之間存在的差異。

STM32H743 移植 Micro-XRCE-DDS 時,在調(diào)用 gethostbyname() 時出現(xiàn)異常怎么解決?

packagesMicro-XRCE-DDS-Client-latestsrccprofiletransportipudpudp_transport_external.c

uxr_init_udp_platform() 函數(shù)調(diào)用

host = (struct hostent

發(fā)表于 09-22 06:54

DDS-TSN 到底是如何實現(xiàn)的?

概述1.1TSN與DDS的獨立優(yōu)勢與局限隨著智能網(wǎng)聯(lián)汽車和車載網(wǎng)絡(luò)架構(gòu)的不斷迭代,車載網(wǎng)絡(luò)對實時性、確定性和高效數(shù)據(jù)分發(fā)的需求日益嚴(yán)苛。TSN和DDS的結(jié)合為車載以太網(wǎng)提供了確定性實時通信(TSN

如何在Unified IDE中創(chuàng)建視覺庫HLS組件

Vivado IP 流程(Vitis Unified),在這篇 AMD Vitis HLS 系列 3 中,我們將介紹如何使用 Unified IDE 創(chuàng)建 HLS 組件。這里采用“自

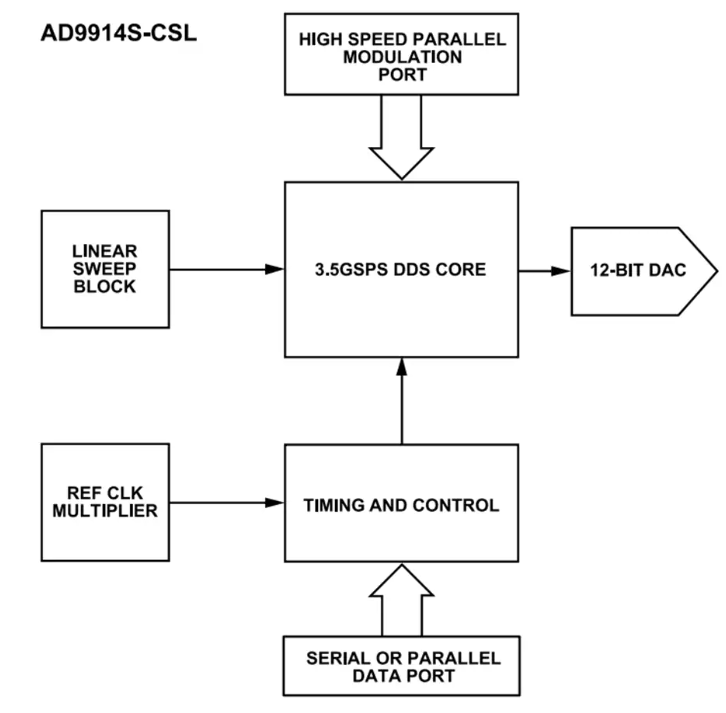

Analog Devices Inc. AD9914S直接數(shù)字合成 (DDS)數(shù)據(jù)手冊

Analog Devices Inc. AD9914S直接數(shù)字合成 (DDS) 采用12位數(shù)模轉(zhuǎn)換器 (DAC)。AD9914S采用先進的DDS技術(shù)以及內(nèi)部高速、高性能DAC,形成數(shù)字

使用AMD Vitis Unified IDE創(chuàng)建HLS組件

這篇文章在開發(fā)者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統(tǒng) IDE) 的基礎(chǔ)上撰寫,但使用的是 AMD Vitis Unified IDE,而不是之前傳統(tǒng)版本的 Vitis HLS

如何使用AMD Vitis HLS創(chuàng)建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 來創(chuàng)建一個 HLS IP,通過 AXI4 接口從存儲器讀取數(shù)據(jù)、執(zhí)行簡單的數(shù)學(xué)運算,然后將數(shù)據(jù)寫回存儲器。接著會在 AMD Vivado Design Suite 設(shè)計中使用此

服務(wù)與數(shù)據(jù)的雙螺旋:從SOME/IP到DDS看汽車電子架構(gòu)的進化之路

底層通信技術(shù)的演進始終是由應(yīng)用需求的不斷變化所驅(qū)動的。正如“進化論”所強調(diào)的,“適者生存”才是核心:并不存在放之四海而皆準(zhǔn)的“最優(yōu)”技術(shù),只有在特定場景下最合適的解決方案。對于SOME/IP和DDS,很多人習(xí)慣于直接問“孰優(yōu)孰劣”,但如果脫離具體的應(yīng)用場景去討論優(yōu)劣,往往

Vivado HLS設(shè)計流程

為了盡快把新產(chǎn)品推向市場,數(shù)字系統(tǒng)的設(shè)計者需要考慮如何加速設(shè)計開發(fā)的周期。設(shè)計加速主要可以從“設(shè)計的重用”和“抽象層級的提升”這兩個方面來考慮。Xilinx 推出的 Vivado HLS 工具可以

Zynq7000處理器的配置詳解

添加好ZYNQ7 Processing System IP核后,需要對其進行配置,雙擊彈出如下窗口。綠色部分表示ZYNQ PS部分中可配置的項目,可以雙擊轉(zhuǎn)向相應(yīng)的設(shè)置界面,也可以直接在左邊的導(dǎo)航列表中選擇。

采用Zynq SDR套件的DDS HLS IP

采用Zynq SDR套件的DDS HLS IP

評論